Go to the source code of this file.

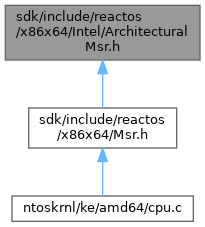

Detailed Description

Intel Architectural MSR Definitions.

Provides defines for Machine Specific Registers(MSR) indexes. Data structures are provided for MSRs that contain one or more bit fields. If the MSR value returned is a single 32-bit or 64-bit value, then a data structure is not provided for that MSR.

Copyright (c) 2016 - 2023, Intel Corporation. All rights reserved.

SPDX-License-Identifier: BSD-2-Clause-Patent

- Specification Reference:

- Intel(R) 64 and IA-32 Architectures Software Developer's Manual, Volume 4, May 2018, Volume 4: Model-Specific-Registers (MSR)

Definition in file ArchitecturalMsr.h.

Macro Definition Documentation

◆ MSR_IA32_A_PMC0

| #define MSR_IA32_A_PMC0 0x000004C1 |

Full Width Writable IA32_PMCn Alias (R/W). (If CPUID.0AH: EAX[15:8] > n) && IA32_PERF_CAPABILITIES[ 13] = 1.

- Parameters

-

ECX MSR_IA32_A_PMCn EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_A_PMC0 is defined as IA32_A_PMC0 in SDM. MSR_IA32_A_PMC1 is defined as IA32_A_PMC1 in SDM. MSR_IA32_A_PMC2 is defined as IA32_A_PMC2 in SDM. MSR_IA32_A_PMC3 is defined as IA32_A_PMC3 in SDM. MSR_IA32_A_PMC4 is defined as IA32_A_PMC4 in SDM. MSR_IA32_A_PMC5 is defined as IA32_A_PMC5 in SDM. MSR_IA32_A_PMC6 is defined as IA32_A_PMC6 in SDM. MSR_IA32_A_PMC7 is defined as IA32_A_PMC7 in SDM.

Definition at line 4231 of file ArchitecturalMsr.h.

◆ MSR_IA32_A_PMC1

| #define MSR_IA32_A_PMC1 0x000004C2 |

Definition at line 4232 of file ArchitecturalMsr.h.

◆ MSR_IA32_A_PMC2

| #define MSR_IA32_A_PMC2 0x000004C3 |

Definition at line 4233 of file ArchitecturalMsr.h.

◆ MSR_IA32_A_PMC3

| #define MSR_IA32_A_PMC3 0x000004C4 |

Definition at line 4234 of file ArchitecturalMsr.h.

◆ MSR_IA32_A_PMC4

| #define MSR_IA32_A_PMC4 0x000004C5 |

Definition at line 4235 of file ArchitecturalMsr.h.

◆ MSR_IA32_A_PMC5

| #define MSR_IA32_A_PMC5 0x000004C6 |

Definition at line 4236 of file ArchitecturalMsr.h.

◆ MSR_IA32_A_PMC6

| #define MSR_IA32_A_PMC6 0x000004C7 |

Definition at line 4237 of file ArchitecturalMsr.h.

◆ MSR_IA32_A_PMC7

| #define MSR_IA32_A_PMC7 0x000004C8 |

Definition at line 4238 of file ArchitecturalMsr.h.

◆ MSR_IA32_APERF

| #define MSR_IA32_APERF 0x000000E8 |

Actual Performance Clock Counter (R/Write to clear). If CPUID.06H: ECX[0] =

- C0_ACNT: C0 Actual Frequency Clock Count Accumulates core clock counts at the coordinated clock frequency, when the logical processor is in C0. Cleared upon overflow / wrap-around of IA32_MPERF.

- Parameters

-

ECX MSR_IA32_APERF (0x000000E8) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_APERF is defined as IA32_APERF in SDM.

Definition at line 624 of file ArchitecturalMsr.h.

◆ MSR_IA32_APIC_BASE

| #define MSR_IA32_APIC_BASE 0x0000001B |

06_01H.

- Parameters

-

ECX MSR_IA32_APIC_BASE (0x0000001B) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_APIC_BASE_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_APIC_BASE_REGISTER.

Example usage

- Note

- MSR_IA32_APIC_BASE is defined as IA32_APIC_BASE in SDM.

Definition at line 167 of file ArchitecturalMsr.h.

◆ MSR_IA32_BIOS_SIGN_ID

| #define MSR_IA32_BIOS_SIGN_ID 0x0000008B |

BIOS Update Signature (RO) Returns the microcode update signature following the execution of CPUID.01H. A processor may prevent writing to this MSR when loading guest states on VM entries or saving guest states on VM exits. Introduced at Display Family / Display Model 06_01H.

- Parameters

-

ECX MSR_IA32_BIOS_SIGN_ID (0x0000008B) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_BIOS_SIGN_ID_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_BIOS_SIGN_ID_REGISTER.

Example usage

- Note

- MSR_IA32_BIOS_SIGN_ID is defined as IA32_BIOS_SIGN_ID in SDM.

Definition at line 374 of file ArchitecturalMsr.h.

◆ MSR_IA32_BIOS_UPDT_TRIG

| #define MSR_IA32_BIOS_UPDT_TRIG 0x00000079 |

BIOS Update Trigger (W) Executing a WRMSR instruction to this MSR causes a microcode update to be loaded into the processor. See Section 9.11.6, "Microcode Update Loader." A processor may prevent writing to this MSR when loading guest states on VM entries or saving guest states on VM exits. Introduced at Display Family / Display Model 06_01H.

- Parameters

-

ECX MSR_IA32_BIOS_UPDT_TRIG (0x00000079) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_BIOS_UPDT_TRIG is defined as IA32_BIOS_UPDT_TRIG in SDM.

Definition at line 352 of file ArchitecturalMsr.h.

◆ MSR_IA32_BNDCFGS

| #define MSR_IA32_BNDCFGS 0x00000D90 |

Supervisor State of MPX Configuration. (R/W). If (CPUID.(EAX=07H, ECX=0H):EBX[14] = 1).

- Parameters

-

ECX MSR_IA32_BNDCFGS (0x00000D90) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_BNDCFGS_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_BNDCFGS_REGISTER.

Example usage

- Note

- MSR_IA32_BNDCFGS is defined as IA32_BNDCFGS in SDM.

Definition at line 6103 of file ArchitecturalMsr.h.

◆ MSR_IA32_CLOCK_MODULATION

| #define MSR_IA32_CLOCK_MODULATION 0x0000019A |

Clock Modulation Control (R/W) See Section 14.7.3, "Software Controlled Clock Modulation.". If CPUID.01H:EDX[22] = 1.

- Parameters

-

ECX MSR_IA32_CLOCK_MODULATION (0x0000019A) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_CLOCK_MODULATION_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_CLOCK_MODULATION_REGISTER.

Example usage

- Note

- MSR_IA32_CLOCK_MODULATION is defined as IA32_CLOCK_MODULATION in SDM.

Definition at line 1148 of file ArchitecturalMsr.h.

◆ MSR_IA32_CPU_DCA_CAP

| #define MSR_IA32_CPU_DCA_CAP 0x000001F9 |

If set, CPU supports Prefetch-Hint type. If CPUID.01H: ECX[18] = 1.

- Parameters

-

ECX MSR_IA32_CPU_DCA_CAP (0x000001F9) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_CPU_DCA_CAP is defined as IA32_CPU_DCA_CAP in SDM.

Definition at line 1989 of file ArchitecturalMsr.h.

◆ MSR_IA32_CSTAR

| #define MSR_IA32_CSTAR 0xC0000083 |

IA-32e Mode System Call Target Address (R/W) Not used, as the SYSCALL instruction is not recognized in compatibility mode. If CPUID.80000001:EDX.[29] = 1.

- Parameters

-

ECX MSR_IA32_CSTAR (0xC0000083) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_CSTAR is defined as IA32_CSTAR in SDM.

Definition at line 6414 of file ArchitecturalMsr.h.

◆ MSR_IA32_DCA_0_CAP

| #define MSR_IA32_DCA_0_CAP 0x000001FA |

DCA type 0 Status and Control register. If CPUID.01H: ECX[18] = 1.

- Parameters

-

ECX MSR_IA32_DCA_0_CAP (0x000001FA) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_DCA_0_CAP_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_DCA_0_CAP_REGISTER.

Example usage

- Note

- MSR_IA32_DCA_0_CAP is defined as IA32_DCA_0_CAP in SDM.

Definition at line 2009 of file ArchitecturalMsr.h.

◆ MSR_IA32_DEBUG_INTERFACE

| #define MSR_IA32_DEBUG_INTERFACE 0x00000C80 |

Silicon Debug Feature Control (R/W). If CPUID.01H:ECX.[11] = 1.

- Parameters

-

ECX MSR_IA32_DEBUG_INTERFACE (0x00000C80) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_DEBUG_INTERFACE_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_DEBUG_INTERFACE_REGISTER.

Example usage

- Note

- MSR_IA32_DEBUG_INTERFACE is defined as IA32_DEBUG_INTERFACE in SDM.

Definition at line 5804 of file ArchitecturalMsr.h.

◆ MSR_IA32_DEBUGCTL

| #define MSR_IA32_DEBUGCTL 0x000001D9 |

Trace/Profile Resource Control (R/W). Introduced at Display Family / Display Model 06_0EH.

- Parameters

-

ECX MSR_IA32_DEBUGCTL (0x000001D9) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_DEBUGCTL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_DEBUGCTL_REGISTER.

Example usage

- Note

- MSR_IA32_DEBUGCTL is defined as IA32_DEBUGCTL in SDM.

Definition at line 1765 of file ArchitecturalMsr.h.

◆ MSR_IA32_DS_AREA

| #define MSR_IA32_DS_AREA 0x00000600 |

DS Save Area (R/W) Points to the linear address of the first byte of the DS buffer management area, which is used to manage the BTS and PEBS buffers. See Section 18.6.3.4, "Debug Store (DS) Mechanism.". If( CPUID.01H:EDX.DS[21] = 1. The linear address of the first byte of the DS buffer management area, if IA-32e mode is active.

- Parameters

-

ECX MSR_IA32_DS_AREA (0x00000600) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_DS_AREA_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_DS_AREA_REGISTER.

Example usage

- Note

- MSR_IA32_DS_AREA is defined as IA32_DS_AREA in SDM.

Definition at line 4846 of file ArchitecturalMsr.h.

◆ MSR_IA32_EFER

| #define MSR_IA32_EFER 0xC0000080 |

Extended Feature Enables. If ( CPUID.80000001H:EDX.[2 0] CPUID.80000001H:EDX.[2 9]).

- Parameters

-

ECX MSR_IA32_EFER (0xC0000080) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_EFER_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_EFER_REGISTER.

Example usage

- Note

- MSR_IA32_EFER is defined as IA32_EFER in SDM.

Definition at line 6316 of file ArchitecturalMsr.h.

◆ MSR_IA32_ENERGY_PERF_BIAS

| #define MSR_IA32_ENERGY_PERF_BIAS 0x000001B0 |

Performance Energy Bias Hint (R/W). if CPUID.6H:ECX[3] = 1.

- Parameters

-

ECX MSR_IA32_ENERGY_PERF_BIAS (0x000001B0) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_ENERGY_PERF_BIAS_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_ENERGY_PERF_BIAS_REGISTER.

Example usage

- Note

- MSR_IA32_ENERGY_PERF_BIAS is defined as IA32_ENERGY_PERF_BIAS in SDM.

Definition at line 1541 of file ArchitecturalMsr.h.

◆ MSR_IA32_FEATURE_CONTROL

| #define MSR_IA32_FEATURE_CONTROL 0x0000003A |

Control Features in Intel 64 Processor (R/W). If any one enumeration condition for defined bit field holds.

- Parameters

-

ECX MSR_IA32_FEATURE_CONTROL (0x0000003A) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_FEATURE_CONTROL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_FEATURE_CONTROL_REGISTER.

Example usage

- Note

- MSR_IA32_FEATURE_CONTROL is defined as IA32_FEATURE_CONTROL in SDM.

Definition at line 226 of file ArchitecturalMsr.h.

◆ MSR_IA32_FIXED_CTR0

| #define MSR_IA32_FIXED_CTR0 0x00000309 |

Fixed-Function Performance Counter 0 (R/W): Counts Instr_Retired.Any. If CPUID.0AH: EDX[4:0] > 0.

- Parameters

-

ECX MSR_IA32_FIXED_CTR0 (0x00000309) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_FIXED_CTR0 is defined as IA32_FIXED_CTR0 in SDM.

Definition at line 2675 of file ArchitecturalMsr.h.

◆ MSR_IA32_FIXED_CTR1

| #define MSR_IA32_FIXED_CTR1 0x0000030A |

Fixed-Function Performance Counter 1 (R/W): Counts CPU_CLK_Unhalted.Core. If CPUID.0AH: EDX[4:0] > 1.

- Parameters

-

ECX MSR_IA32_FIXED_CTR1 (0x0000030A) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_FIXED_CTR1 is defined as IA32_FIXED_CTR1 in SDM.

Definition at line 2694 of file ArchitecturalMsr.h.

◆ MSR_IA32_FIXED_CTR2

| #define MSR_IA32_FIXED_CTR2 0x0000030B |

Fixed-Function Performance Counter 2 (R/W): Counts CPU_CLK_Unhalted.Ref. If CPUID.0AH: EDX[4:0] > 2.

- Parameters

-

ECX MSR_IA32_FIXED_CTR2 (0x0000030B) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_FIXED_CTR2 is defined as IA32_FIXED_CTR2 in SDM.

Definition at line 2713 of file ArchitecturalMsr.h.

◆ MSR_IA32_FIXED_CTR_CTRL

| #define MSR_IA32_FIXED_CTR_CTRL 0x0000038D |

Fixed-Function Performance Counter Control (R/W) Counter increments while the results of ANDing respective enable bit in IA32_PERF_GLOBAL_CTRL with the corresponding OS or USR bits in this MSR is true. If CPUID.0AH: EAX[7:0]

1.

- Parameters

-

ECX MSR_IA32_FIXED_CTR_CTRL (0x0000038D) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_FIXED_CTR_CTRL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_FIXED_CTR_CTRL_REGISTER.

Example usage

- Note

- MSR_IA32_FIXED_CTR_CTRL is defined as IA32_FIXED_CTR_CTRL in SDM.

Definition at line 2801 of file ArchitecturalMsr.h.

◆ MSR_IA32_FMASK

| #define MSR_IA32_FMASK 0xC0000084 |

System Call Flag Mask (R/W). If CPUID.80000001:EDX.[29] = 1.

- Parameters

-

ECX MSR_IA32_FMASK (0xC0000084) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_FMASK is defined as IA32_FMASK in SDM.

Definition at line 6432 of file ArchitecturalMsr.h.

◆ MSR_IA32_FS_BASE

| #define MSR_IA32_FS_BASE 0xC0000100 |

Map of BASE Address of FS (R/W). If CPUID.80000001:EDX.[29] = 1.

- Parameters

-

ECX MSR_IA32_FS_BASE (0xC0000100) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_FS_BASE is defined as IA32_FS_BASE in SDM.

Definition at line 6450 of file ArchitecturalMsr.h.

◆ MSR_IA32_GS_BASE

| #define MSR_IA32_GS_BASE 0xC0000101 |

Map of BASE Address of GS (R/W). If CPUID.80000001:EDX.[29] = 1.

- Parameters

-

ECX MSR_IA32_GS_BASE (0xC0000101) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_GS_BASE is defined as IA32_GS_BASE in SDM.

Definition at line 6468 of file ArchitecturalMsr.h.

◆ MSR_IA32_HWP_CAPABILITIES

| #define MSR_IA32_HWP_CAPABILITIES 0x00000771 |

HWP Performance Range Enumeration (RO). If CPUID.06H:EAX.[7] = 1.

- Parameters

-

ECX MSR_IA32_HWP_CAPABILITIES (0x00000771) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_HWP_CAPABILITIES_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_HWP_CAPABILITIES_REGISTER.

Example usage

- Note

- MSR_IA32_HWP_CAPABILITIES is defined as IA32_HWP_CAPABILITIES in SDM.

Definition at line 4930 of file ArchitecturalMsr.h.

◆ MSR_IA32_HWP_INTERRUPT

| #define MSR_IA32_HWP_INTERRUPT 0x00000773 |

Control HWP Native Interrupts (R/W). If CPUID.06H:EAX.[8] = 1.

- Parameters

-

ECX MSR_IA32_HWP_INTERRUPT (0x00000773) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_HWP_INTERRUPT_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_HWP_INTERRUPT_REGISTER.

Example usage

- Note

- MSR_IA32_HWP_INTERRUPT is defined as IA32_HWP_INTERRUPT in SDM.

Definition at line 5052 of file ArchitecturalMsr.h.

◆ MSR_IA32_HWP_REQUEST

| #define MSR_IA32_HWP_REQUEST 0x00000774 |

Power Management Control Hints to a Logical Processor (R/W). If CPUID.06H:EAX.[7] = 1.

- Parameters

-

ECX MSR_IA32_HWP_REQUEST (0x00000774) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_HWP_REQUEST_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_HWP_REQUEST_REGISTER.

Example usage

- Note

- MSR_IA32_HWP_REQUEST is defined as IA32_HWP_REQUEST in SDM.

Definition at line 5104 of file ArchitecturalMsr.h.

◆ MSR_IA32_HWP_REQUEST_PKG

| #define MSR_IA32_HWP_REQUEST_PKG 0x00000772 |

Power Management Control Hints for All Logical Processors in a Package (R/W). If CPUID.06H:EAX.[11] = 1.

- Parameters

-

ECX MSR_IA32_HWP_REQUEST_PKG (0x00000772) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_HWP_REQUEST_PKG_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_HWP_REQUEST_PKG_REGISTER.

Example usage

- Note

- MSR_IA32_HWP_REQUEST_PKG is defined as IA32_HWP_REQUEST_PKG in SDM.

Definition at line 4991 of file ArchitecturalMsr.h.

◆ MSR_IA32_HWP_STATUS

| #define MSR_IA32_HWP_STATUS 0x00000777 |

Log bits indicating changes to Guaranteed & excursions to Minimum (R/W). If CPUID.06H:EAX.[7] = 1.

- Parameters

-

ECX MSR_IA32_HWP_STATUS (0x00000777) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_HWP_STATUS_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_HWP_STATUS_REGISTER.

Example usage

- Note

- MSR_IA32_HWP_STATUS is defined as IA32_HWP_STATUS in SDM.

Definition at line 5171 of file ArchitecturalMsr.h.

◆ MSR_IA32_KERNEL_GS_BASE

| #define MSR_IA32_KERNEL_GS_BASE 0xC0000102 |

Swap Target of BASE Address of GS (R/W). If CPUID.80000001:EDX.[29] = 1.

- Parameters

-

ECX MSR_IA32_KERNEL_GS_BASE (0xC0000102) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_KERNEL_GS_BASE is defined as IA32_KERNEL_GS_BASE in SDM.

Definition at line 6486 of file ArchitecturalMsr.h.

◆ MSR_IA32_L2_QOS_CFG

| #define MSR_IA32_L2_QOS_CFG 0x00000C82 |

L2 QOS Configuration (R/W). If ( CPUID.(EAX=10H, ECX=2):ECX.[2] = 1 ).

- Parameters

-

ECX MSR_IA32_L2_QOS_CFG (0x00000C82) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_L2_QOS_CFG_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_L2_QOS_CFG_REGISTER.

Example usage

- Note

- MSR_IA32_L2_QOS_CFG is defined as IA32_L2_QOS_CFG in SDM.

Definition at line 5907 of file ArchitecturalMsr.h.

◆ MSR_IA32_L3_QOS_CFG

| #define MSR_IA32_L3_QOS_CFG 0x00000C81 |

L3 QOS Configuration (R/W). If ( CPUID.(EAX=10H, ECX=1):ECX.[2] = 1 ).

- Parameters

-

ECX MSR_IA32_L3_QOS_CFG (0x00000C81) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_L3_QOS_CFG_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_L3_QOS_CFG_REGISTER.

Example usage

- Note

- MSR_IA32_L3_QOS_CFG is defined as IA32_L3_QOS_CFG in SDM.

Definition at line 5861 of file ArchitecturalMsr.h.

◆ MSR_IA32_LSTAR

| #define MSR_IA32_LSTAR 0xC0000082 |

IA-32e Mode System Call Target Address (R/W). If CPUID.80000001:EDX.[29] = 1.

- Parameters

-

ECX MSR_IA32_LSTAR (0xC0000082) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_LSTAR is defined as IA32_LSTAR in SDM.

Definition at line 6394 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC0_ADDR

| #define MSR_IA32_MC0_ADDR 0x00000402 |

MCn_ADDR. If IA32_MCG_CAP.CNT > n.

- Parameters

-

ECX MSR_IA32_MCn_ADDR EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MC0_ADDR is defined as IA32_MC0_ADDR in SDM. MSR_IA32_MC1_ADDR is defined as IA32_MC1_ADDR in SDM. MSR_IA32_MC2_ADDR is defined as IA32_MC2_ADDR in SDM. MSR_IA32_MC3_ADDR is defined as IA32_MC3_ADDR in SDM. MSR_IA32_MC4_ADDR is defined as IA32_MC4_ADDR in SDM. MSR_IA32_MC5_ADDR is defined as IA32_MC5_ADDR in SDM. MSR_IA32_MC6_ADDR is defined as IA32_MC6_ADDR in SDM. MSR_IA32_MC7_ADDR is defined as IA32_MC7_ADDR in SDM. MSR_IA32_MC8_ADDR is defined as IA32_MC8_ADDR in SDM. MSR_IA32_MC9_ADDR is defined as IA32_MC9_ADDR in SDM. MSR_IA32_MC10_ADDR is defined as IA32_MC10_ADDR in SDM. MSR_IA32_MC11_ADDR is defined as IA32_MC11_ADDR in SDM. MSR_IA32_MC12_ADDR is defined as IA32_MC12_ADDR in SDM. MSR_IA32_MC13_ADDR is defined as IA32_MC13_ADDR in SDM. MSR_IA32_MC14_ADDR is defined as IA32_MC14_ADDR in SDM. MSR_IA32_MC15_ADDR is defined as IA32_MC15_ADDR in SDM. MSR_IA32_MC16_ADDR is defined as IA32_MC16_ADDR in SDM. MSR_IA32_MC17_ADDR is defined as IA32_MC17_ADDR in SDM. MSR_IA32_MC18_ADDR is defined as IA32_MC18_ADDR in SDM. MSR_IA32_MC19_ADDR is defined as IA32_MC19_ADDR in SDM. MSR_IA32_MC20_ADDR is defined as IA32_MC20_ADDR in SDM. MSR_IA32_MC21_ADDR is defined as IA32_MC21_ADDR in SDM. MSR_IA32_MC22_ADDR is defined as IA32_MC22_ADDR in SDM. MSR_IA32_MC23_ADDR is defined as IA32_MC23_ADDR in SDM. MSR_IA32_MC24_ADDR is defined as IA32_MC24_ADDR in SDM. MSR_IA32_MC25_ADDR is defined as IA32_MC25_ADDR in SDM. MSR_IA32_MC26_ADDR is defined as IA32_MC26_ADDR in SDM. MSR_IA32_MC27_ADDR is defined as IA32_MC27_ADDR in SDM. MSR_IA32_MC28_ADDR is defined as IA32_MC28_ADDR in SDM.

Definition at line 3567 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC0_CTL

| #define MSR_IA32_MC0_CTL 0x00000400 |

MCn_CTL. If IA32_MCG_CAP.CNT > n.

- Parameters

-

ECX MSR_IA32_MCn_CTL EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MC0_CTL is defined as IA32_MC0_CTL in SDM. MSR_IA32_MC1_CTL is defined as IA32_MC1_CTL in SDM. MSR_IA32_MC2_CTL is defined as IA32_MC2_CTL in SDM. MSR_IA32_MC3_CTL is defined as IA32_MC3_CTL in SDM. MSR_IA32_MC4_CTL is defined as IA32_MC4_CTL in SDM. MSR_IA32_MC5_CTL is defined as IA32_MC5_CTL in SDM. MSR_IA32_MC6_CTL is defined as IA32_MC6_CTL in SDM. MSR_IA32_MC7_CTL is defined as IA32_MC7_CTL in SDM. MSR_IA32_MC8_CTL is defined as IA32_MC8_CTL in SDM. MSR_IA32_MC9_CTL is defined as IA32_MC9_CTL in SDM. MSR_IA32_MC10_CTL is defined as IA32_MC10_CTL in SDM. MSR_IA32_MC11_CTL is defined as IA32_MC11_CTL in SDM. MSR_IA32_MC12_CTL is defined as IA32_MC12_CTL in SDM. MSR_IA32_MC13_CTL is defined as IA32_MC13_CTL in SDM. MSR_IA32_MC14_CTL is defined as IA32_MC14_CTL in SDM. MSR_IA32_MC15_CTL is defined as IA32_MC15_CTL in SDM. MSR_IA32_MC16_CTL is defined as IA32_MC16_CTL in SDM. MSR_IA32_MC17_CTL is defined as IA32_MC17_CTL in SDM. MSR_IA32_MC18_CTL is defined as IA32_MC18_CTL in SDM. MSR_IA32_MC19_CTL is defined as IA32_MC19_CTL in SDM. MSR_IA32_MC20_CTL is defined as IA32_MC20_CTL in SDM. MSR_IA32_MC21_CTL is defined as IA32_MC21_CTL in SDM. MSR_IA32_MC22_CTL is defined as IA32_MC22_CTL in SDM. MSR_IA32_MC23_CTL is defined as IA32_MC23_CTL in SDM. MSR_IA32_MC24_CTL is defined as IA32_MC24_CTL in SDM. MSR_IA32_MC25_CTL is defined as IA32_MC25_CTL in SDM. MSR_IA32_MC26_CTL is defined as IA32_MC26_CTL in SDM. MSR_IA32_MC27_CTL is defined as IA32_MC27_CTL in SDM. MSR_IA32_MC28_CTL is defined as IA32_MC28_CTL in SDM.

Definition at line 3415 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC0_CTL2

| #define MSR_IA32_MC0_CTL2 0x00000280 |

Provides the programming interface to use corrected MC error signaling capability (R/W). If IA32_MCG_CAP[10] = 1 && IA32_MCG_CAP[7:0] > n.

- Parameters

-

ECX MSR_IA32_MCn_CTL2 EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_MC_CTL2_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_MC_CTL2_REGISTER.

Example usage

- Note

- MSR_IA32_MC0_CTL2 is defined as IA32_MC0_CTL2 in SDM. MSR_IA32_MC1_CTL2 is defined as IA32_MC1_CTL2 in SDM. MSR_IA32_MC2_CTL2 is defined as IA32_MC2_CTL2 in SDM. MSR_IA32_MC3_CTL2 is defined as IA32_MC3_CTL2 in SDM. MSR_IA32_MC4_CTL2 is defined as IA32_MC4_CTL2 in SDM. MSR_IA32_MC5_CTL2 is defined as IA32_MC5_CTL2 in SDM. MSR_IA32_MC6_CTL2 is defined as IA32_MC6_CTL2 in SDM. MSR_IA32_MC7_CTL2 is defined as IA32_MC7_CTL2 in SDM. MSR_IA32_MC8_CTL2 is defined as IA32_MC8_CTL2 in SDM. MSR_IA32_MC9_CTL2 is defined as IA32_MC9_CTL2 in SDM. MSR_IA32_MC10_CTL2 is defined as IA32_MC10_CTL2 in SDM. MSR_IA32_MC11_CTL2 is defined as IA32_MC11_CTL2 in SDM. MSR_IA32_MC12_CTL2 is defined as IA32_MC12_CTL2 in SDM. MSR_IA32_MC13_CTL2 is defined as IA32_MC13_CTL2 in SDM. MSR_IA32_MC14_CTL2 is defined as IA32_MC14_CTL2 in SDM. MSR_IA32_MC15_CTL2 is defined as IA32_MC15_CTL2 in SDM. MSR_IA32_MC16_CTL2 is defined as IA32_MC16_CTL2 in SDM. MSR_IA32_MC17_CTL2 is defined as IA32_MC17_CTL2 in SDM. MSR_IA32_MC18_CTL2 is defined as IA32_MC18_CTL2 in SDM. MSR_IA32_MC19_CTL2 is defined as IA32_MC19_CTL2 in SDM. MSR_IA32_MC20_CTL2 is defined as IA32_MC20_CTL2 in SDM. MSR_IA32_MC21_CTL2 is defined as IA32_MC21_CTL2 in SDM. MSR_IA32_MC22_CTL2 is defined as IA32_MC22_CTL2 in SDM. MSR_IA32_MC23_CTL2 is defined as IA32_MC23_CTL2 in SDM. MSR_IA32_MC24_CTL2 is defined as IA32_MC24_CTL2 in SDM. MSR_IA32_MC25_CTL2 is defined as IA32_MC25_CTL2 in SDM. MSR_IA32_MC26_CTL2 is defined as IA32_MC26_CTL2 in SDM. MSR_IA32_MC27_CTL2 is defined as IA32_MC27_CTL2 in SDM. MSR_IA32_MC28_CTL2 is defined as IA32_MC28_CTL2 in SDM. MSR_IA32_MC29_CTL2 is defined as IA32_MC29_CTL2 in SDM. MSR_IA32_MC30_CTL2 is defined as IA32_MC30_CTL2 in SDM. MSR_IA32_MC31_CTL2 is defined as IA32_MC31_CTL2 in SDM.

Definition at line 2539 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC0_MISC

| #define MSR_IA32_MC0_MISC 0x00000403 |

MCn_MISC. If IA32_MCG_CAP.CNT > n.

- Parameters

-

ECX MSR_IA32_MCn_MISC EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MC0_MISC is defined as IA32_MC0_MISC in SDM. MSR_IA32_MC1_MISC is defined as IA32_MC1_MISC in SDM. MSR_IA32_MC2_MISC is defined as IA32_MC2_MISC in SDM. MSR_IA32_MC3_MISC is defined as IA32_MC3_MISC in SDM. MSR_IA32_MC4_MISC is defined as IA32_MC4_MISC in SDM. MSR_IA32_MC5_MISC is defined as IA32_MC5_MISC in SDM. MSR_IA32_MC6_MISC is defined as IA32_MC6_MISC in SDM. MSR_IA32_MC7_MISC is defined as IA32_MC7_MISC in SDM. MSR_IA32_MC8_MISC is defined as IA32_MC8_MISC in SDM. MSR_IA32_MC9_MISC is defined as IA32_MC9_MISC in SDM. MSR_IA32_MC10_MISC is defined as IA32_MC10_MISC in SDM. MSR_IA32_MC11_MISC is defined as IA32_MC11_MISC in SDM. MSR_IA32_MC12_MISC is defined as IA32_MC12_MISC in SDM. MSR_IA32_MC13_MISC is defined as IA32_MC13_MISC in SDM. MSR_IA32_MC14_MISC is defined as IA32_MC14_MISC in SDM. MSR_IA32_MC15_MISC is defined as IA32_MC15_MISC in SDM. MSR_IA32_MC16_MISC is defined as IA32_MC16_MISC in SDM. MSR_IA32_MC17_MISC is defined as IA32_MC17_MISC in SDM. MSR_IA32_MC18_MISC is defined as IA32_MC18_MISC in SDM. MSR_IA32_MC19_MISC is defined as IA32_MC19_MISC in SDM. MSR_IA32_MC20_MISC is defined as IA32_MC20_MISC in SDM. MSR_IA32_MC21_MISC is defined as IA32_MC21_MISC in SDM. MSR_IA32_MC22_MISC is defined as IA32_MC22_MISC in SDM. MSR_IA32_MC23_MISC is defined as IA32_MC23_MISC in SDM. MSR_IA32_MC24_MISC is defined as IA32_MC24_MISC in SDM. MSR_IA32_MC25_MISC is defined as IA32_MC25_MISC in SDM. MSR_IA32_MC26_MISC is defined as IA32_MC26_MISC in SDM. MSR_IA32_MC27_MISC is defined as IA32_MC27_MISC in SDM. MSR_IA32_MC28_MISC is defined as IA32_MC28_MISC in SDM.

Definition at line 3643 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC0_STATUS

| #define MSR_IA32_MC0_STATUS 0x00000401 |

MCn_STATUS. If IA32_MCG_CAP.CNT > n.

- Parameters

-

ECX MSR_IA32_MCn_STATUS EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MC0_STATUS is defined as IA32_MC0_STATUS in SDM. MSR_IA32_MC1_STATUS is defined as IA32_MC1_STATUS in SDM. MSR_IA32_MC2_STATUS is defined as IA32_MC2_STATUS in SDM. MSR_IA32_MC3_STATUS is defined as IA32_MC3_STATUS in SDM. MSR_IA32_MC4_STATUS is defined as IA32_MC4_STATUS in SDM. MSR_IA32_MC5_STATUS is defined as IA32_MC5_STATUS in SDM. MSR_IA32_MC6_STATUS is defined as IA32_MC6_STATUS in SDM. MSR_IA32_MC7_STATUS is defined as IA32_MC7_STATUS in SDM. MSR_IA32_MC8_STATUS is defined as IA32_MC8_STATUS in SDM. MSR_IA32_MC9_STATUS is defined as IA32_MC9_STATUS in SDM. MSR_IA32_MC10_STATUS is defined as IA32_MC10_STATUS in SDM. MSR_IA32_MC11_STATUS is defined as IA32_MC11_STATUS in SDM. MSR_IA32_MC12_STATUS is defined as IA32_MC12_STATUS in SDM. MSR_IA32_MC13_STATUS is defined as IA32_MC13_STATUS in SDM. MSR_IA32_MC14_STATUS is defined as IA32_MC14_STATUS in SDM. MSR_IA32_MC15_STATUS is defined as IA32_MC15_STATUS in SDM. MSR_IA32_MC16_STATUS is defined as IA32_MC16_STATUS in SDM. MSR_IA32_MC17_STATUS is defined as IA32_MC17_STATUS in SDM. MSR_IA32_MC18_STATUS is defined as IA32_MC18_STATUS in SDM. MSR_IA32_MC19_STATUS is defined as IA32_MC19_STATUS in SDM. MSR_IA32_MC20_STATUS is defined as IA32_MC20_STATUS in SDM. MSR_IA32_MC21_STATUS is defined as IA32_MC21_STATUS in SDM. MSR_IA32_MC22_STATUS is defined as IA32_MC22_STATUS in SDM. MSR_IA32_MC23_STATUS is defined as IA32_MC23_STATUS in SDM. MSR_IA32_MC24_STATUS is defined as IA32_MC24_STATUS in SDM. MSR_IA32_MC25_STATUS is defined as IA32_MC25_STATUS in SDM. MSR_IA32_MC26_STATUS is defined as IA32_MC26_STATUS in SDM. MSR_IA32_MC27_STATUS is defined as IA32_MC27_STATUS in SDM. MSR_IA32_MC28_STATUS is defined as IA32_MC28_STATUS in SDM.

Definition at line 3491 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC10_ADDR

| #define MSR_IA32_MC10_ADDR 0x0000042A |

Definition at line 3577 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC10_CTL

| #define MSR_IA32_MC10_CTL 0x00000428 |

Definition at line 3425 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC10_CTL2

| #define MSR_IA32_MC10_CTL2 0x0000028A |

Definition at line 2549 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC10_MISC

| #define MSR_IA32_MC10_MISC 0x0000042B |

Definition at line 3653 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC10_STATUS

| #define MSR_IA32_MC10_STATUS 0x00000429 |

Definition at line 3501 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC11_ADDR

| #define MSR_IA32_MC11_ADDR 0x0000042E |

Definition at line 3578 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC11_CTL

| #define MSR_IA32_MC11_CTL 0x0000042C |

Definition at line 3426 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC11_CTL2

| #define MSR_IA32_MC11_CTL2 0x0000028B |

Definition at line 2550 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC11_MISC

| #define MSR_IA32_MC11_MISC 0x0000042F |

Definition at line 3654 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC11_STATUS

| #define MSR_IA32_MC11_STATUS 0x0000042D |

Definition at line 3502 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC12_ADDR

| #define MSR_IA32_MC12_ADDR 0x00000432 |

Definition at line 3579 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC12_CTL

| #define MSR_IA32_MC12_CTL 0x00000430 |

Definition at line 3427 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC12_CTL2

| #define MSR_IA32_MC12_CTL2 0x0000028C |

Definition at line 2551 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC12_MISC

| #define MSR_IA32_MC12_MISC 0x00000433 |

Definition at line 3655 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC12_STATUS

| #define MSR_IA32_MC12_STATUS 0x00000431 |

Definition at line 3503 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC13_ADDR

| #define MSR_IA32_MC13_ADDR 0x00000436 |

Definition at line 3580 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC13_CTL

| #define MSR_IA32_MC13_CTL 0x00000434 |

Definition at line 3428 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC13_CTL2

| #define MSR_IA32_MC13_CTL2 0x0000028D |

Definition at line 2552 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC13_MISC

| #define MSR_IA32_MC13_MISC 0x00000437 |

Definition at line 3656 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC13_STATUS

| #define MSR_IA32_MC13_STATUS 0x00000435 |

Definition at line 3504 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC14_ADDR

| #define MSR_IA32_MC14_ADDR 0x0000043A |

Definition at line 3581 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC14_CTL

| #define MSR_IA32_MC14_CTL 0x00000438 |

Definition at line 3429 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC14_CTL2

| #define MSR_IA32_MC14_CTL2 0x0000028E |

Definition at line 2553 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC14_MISC

| #define MSR_IA32_MC14_MISC 0x0000043B |

Definition at line 3657 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC14_STATUS

| #define MSR_IA32_MC14_STATUS 0x00000439 |

Definition at line 3505 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC15_ADDR

| #define MSR_IA32_MC15_ADDR 0x0000043E |

Definition at line 3582 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC15_CTL

| #define MSR_IA32_MC15_CTL 0x0000043C |

Definition at line 3430 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC15_CTL2

| #define MSR_IA32_MC15_CTL2 0x0000028F |

Definition at line 2554 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC15_MISC

| #define MSR_IA32_MC15_MISC 0x0000043F |

Definition at line 3658 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC15_STATUS

| #define MSR_IA32_MC15_STATUS 0x0000043D |

Definition at line 3506 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC16_ADDR

| #define MSR_IA32_MC16_ADDR 0x00000442 |

Definition at line 3583 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC16_CTL

| #define MSR_IA32_MC16_CTL 0x00000440 |

Definition at line 3431 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC16_CTL2

| #define MSR_IA32_MC16_CTL2 0x00000290 |

Definition at line 2555 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC16_MISC

| #define MSR_IA32_MC16_MISC 0x00000443 |

Definition at line 3659 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC16_STATUS

| #define MSR_IA32_MC16_STATUS 0x00000441 |

Definition at line 3507 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC17_ADDR

| #define MSR_IA32_MC17_ADDR 0x00000446 |

Definition at line 3584 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC17_CTL

| #define MSR_IA32_MC17_CTL 0x00000444 |

Definition at line 3432 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC17_CTL2

| #define MSR_IA32_MC17_CTL2 0x00000291 |

Definition at line 2556 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC17_MISC

| #define MSR_IA32_MC17_MISC 0x00000447 |

Definition at line 3660 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC17_STATUS

| #define MSR_IA32_MC17_STATUS 0x00000445 |

Definition at line 3508 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC18_ADDR

| #define MSR_IA32_MC18_ADDR 0x0000044A |

Definition at line 3585 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC18_CTL

| #define MSR_IA32_MC18_CTL 0x00000448 |

Definition at line 3433 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC18_CTL2

| #define MSR_IA32_MC18_CTL2 0x00000292 |

Definition at line 2557 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC18_MISC

| #define MSR_IA32_MC18_MISC 0x0000044B |

Definition at line 3661 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC18_STATUS

| #define MSR_IA32_MC18_STATUS 0x00000449 |

Definition at line 3509 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC19_ADDR

| #define MSR_IA32_MC19_ADDR 0x0000044E |

Definition at line 3586 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC19_CTL

| #define MSR_IA32_MC19_CTL 0x0000044C |

Definition at line 3434 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC19_CTL2

| #define MSR_IA32_MC19_CTL2 0x00000293 |

Definition at line 2558 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC19_MISC

| #define MSR_IA32_MC19_MISC 0x0000044F |

Definition at line 3662 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC19_STATUS

| #define MSR_IA32_MC19_STATUS 0x0000044D |

Definition at line 3510 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC1_ADDR

| #define MSR_IA32_MC1_ADDR 0x00000406 |

Definition at line 3568 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC1_CTL

| #define MSR_IA32_MC1_CTL 0x00000404 |

Definition at line 3416 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC1_CTL2

| #define MSR_IA32_MC1_CTL2 0x00000281 |

Definition at line 2540 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC1_MISC

| #define MSR_IA32_MC1_MISC 0x00000407 |

Definition at line 3644 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC1_STATUS

| #define MSR_IA32_MC1_STATUS 0x00000405 |

Definition at line 3492 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC20_ADDR

| #define MSR_IA32_MC20_ADDR 0x00000452 |

Definition at line 3587 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC20_CTL

| #define MSR_IA32_MC20_CTL 0x00000450 |

Definition at line 3435 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC20_CTL2

| #define MSR_IA32_MC20_CTL2 0x00000294 |

Definition at line 2559 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC20_MISC

| #define MSR_IA32_MC20_MISC 0x00000453 |

Definition at line 3663 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC20_STATUS

| #define MSR_IA32_MC20_STATUS 0x00000451 |

Definition at line 3511 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC21_ADDR

| #define MSR_IA32_MC21_ADDR 0x00000456 |

Definition at line 3588 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC21_CTL

| #define MSR_IA32_MC21_CTL 0x00000454 |

Definition at line 3436 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC21_CTL2

| #define MSR_IA32_MC21_CTL2 0x00000295 |

Definition at line 2560 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC21_MISC

| #define MSR_IA32_MC21_MISC 0x00000457 |

Definition at line 3664 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC21_STATUS

| #define MSR_IA32_MC21_STATUS 0x00000455 |

Definition at line 3512 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC22_ADDR

| #define MSR_IA32_MC22_ADDR 0x0000045A |

Definition at line 3589 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC22_CTL

| #define MSR_IA32_MC22_CTL 0x00000458 |

Definition at line 3437 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC22_CTL2

| #define MSR_IA32_MC22_CTL2 0x00000296 |

Definition at line 2561 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC22_MISC

| #define MSR_IA32_MC22_MISC 0x0000045B |

Definition at line 3665 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC22_STATUS

| #define MSR_IA32_MC22_STATUS 0x00000459 |

Definition at line 3513 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC23_ADDR

| #define MSR_IA32_MC23_ADDR 0x0000045E |

Definition at line 3590 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC23_CTL

| #define MSR_IA32_MC23_CTL 0x0000045C |

Definition at line 3438 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC23_CTL2

| #define MSR_IA32_MC23_CTL2 0x00000297 |

Definition at line 2562 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC23_MISC

| #define MSR_IA32_MC23_MISC 0x0000045F |

Definition at line 3666 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC23_STATUS

| #define MSR_IA32_MC23_STATUS 0x0000045D |

Definition at line 3514 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC24_ADDR

| #define MSR_IA32_MC24_ADDR 0x00000462 |

Definition at line 3591 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC24_CTL

| #define MSR_IA32_MC24_CTL 0x00000460 |

Definition at line 3439 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC24_CTL2

| #define MSR_IA32_MC24_CTL2 0x00000298 |

Definition at line 2563 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC24_MISC

| #define MSR_IA32_MC24_MISC 0x00000463 |

Definition at line 3667 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC24_STATUS

| #define MSR_IA32_MC24_STATUS 0x00000461 |

Definition at line 3515 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC25_ADDR

| #define MSR_IA32_MC25_ADDR 0x00000466 |

Definition at line 3592 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC25_CTL

| #define MSR_IA32_MC25_CTL 0x00000464 |

Definition at line 3440 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC25_CTL2

| #define MSR_IA32_MC25_CTL2 0x00000299 |

Definition at line 2564 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC25_MISC

| #define MSR_IA32_MC25_MISC 0x00000467 |

Definition at line 3668 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC25_STATUS

| #define MSR_IA32_MC25_STATUS 0x00000465 |

Definition at line 3516 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC26_ADDR

| #define MSR_IA32_MC26_ADDR 0x0000046A |

Definition at line 3593 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC26_CTL

| #define MSR_IA32_MC26_CTL 0x00000468 |

Definition at line 3441 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC26_CTL2

| #define MSR_IA32_MC26_CTL2 0x0000029A |

Definition at line 2565 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC26_MISC

| #define MSR_IA32_MC26_MISC 0x0000046B |

Definition at line 3669 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC26_STATUS

| #define MSR_IA32_MC26_STATUS 0x00000469 |

Definition at line 3517 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC27_ADDR

| #define MSR_IA32_MC27_ADDR 0x0000046E |

Definition at line 3594 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC27_CTL

| #define MSR_IA32_MC27_CTL 0x0000046C |

Definition at line 3442 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC27_CTL2

| #define MSR_IA32_MC27_CTL2 0x0000029B |

Definition at line 2566 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC27_MISC

| #define MSR_IA32_MC27_MISC 0x0000046F |

Definition at line 3670 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC27_STATUS

| #define MSR_IA32_MC27_STATUS 0x0000046D |

Definition at line 3518 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC28_ADDR

| #define MSR_IA32_MC28_ADDR 0x00000472 |

Definition at line 3595 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC28_CTL

| #define MSR_IA32_MC28_CTL 0x00000470 |

Definition at line 3443 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC28_CTL2

| #define MSR_IA32_MC28_CTL2 0x0000029C |

Definition at line 2567 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC28_MISC

| #define MSR_IA32_MC28_MISC 0x00000473 |

Definition at line 3671 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC28_STATUS

| #define MSR_IA32_MC28_STATUS 0x00000471 |

Definition at line 3519 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC29_CTL2

| #define MSR_IA32_MC29_CTL2 0x0000029D |

Definition at line 2568 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC2_ADDR

| #define MSR_IA32_MC2_ADDR 0x0000040A |

Definition at line 3569 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC2_CTL

| #define MSR_IA32_MC2_CTL 0x00000408 |

Definition at line 3417 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC2_CTL2

| #define MSR_IA32_MC2_CTL2 0x00000282 |

Definition at line 2541 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC2_MISC

| #define MSR_IA32_MC2_MISC 0x0000040B |

Definition at line 3645 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC2_STATUS

| #define MSR_IA32_MC2_STATUS 0x00000409 |

Definition at line 3493 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC30_CTL2

| #define MSR_IA32_MC30_CTL2 0x0000029E |

Definition at line 2569 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC31_CTL2

| #define MSR_IA32_MC31_CTL2 0x0000029F |

Definition at line 2570 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC3_ADDR

| #define MSR_IA32_MC3_ADDR 0x0000040E |

Definition at line 3570 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC3_CTL

| #define MSR_IA32_MC3_CTL 0x0000040C |

Definition at line 3418 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC3_CTL2

| #define MSR_IA32_MC3_CTL2 0x00000283 |

Definition at line 2542 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC3_MISC

| #define MSR_IA32_MC3_MISC 0x0000040F |

Definition at line 3646 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC3_STATUS

| #define MSR_IA32_MC3_STATUS 0x0000040D |

Definition at line 3494 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC4_ADDR

| #define MSR_IA32_MC4_ADDR 0x00000412 |

Definition at line 3571 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC4_CTL

| #define MSR_IA32_MC4_CTL 0x00000410 |

Definition at line 3419 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC4_CTL2

| #define MSR_IA32_MC4_CTL2 0x00000284 |

Definition at line 2543 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC4_MISC

| #define MSR_IA32_MC4_MISC 0x00000413 |

Definition at line 3647 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC4_STATUS

| #define MSR_IA32_MC4_STATUS 0x00000411 |

Definition at line 3495 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC5_ADDR

| #define MSR_IA32_MC5_ADDR 0x00000416 |

Definition at line 3572 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC5_CTL

| #define MSR_IA32_MC5_CTL 0x00000414 |

Definition at line 3420 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC5_CTL2

| #define MSR_IA32_MC5_CTL2 0x00000285 |

Definition at line 2544 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC5_MISC

| #define MSR_IA32_MC5_MISC 0x00000417 |

Definition at line 3648 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC5_STATUS

| #define MSR_IA32_MC5_STATUS 0x00000415 |

Definition at line 3496 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC6_ADDR

| #define MSR_IA32_MC6_ADDR 0x0000041A |

Definition at line 3573 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC6_CTL

| #define MSR_IA32_MC6_CTL 0x00000418 |

Definition at line 3421 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC6_CTL2

| #define MSR_IA32_MC6_CTL2 0x00000286 |

Definition at line 2545 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC6_MISC

| #define MSR_IA32_MC6_MISC 0x0000041B |

Definition at line 3649 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC6_STATUS

| #define MSR_IA32_MC6_STATUS 0x00000419 |

Definition at line 3497 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC7_ADDR

| #define MSR_IA32_MC7_ADDR 0x0000041E |

Definition at line 3574 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC7_CTL

| #define MSR_IA32_MC7_CTL 0x0000041C |

Definition at line 3422 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC7_CTL2

| #define MSR_IA32_MC7_CTL2 0x00000287 |

Definition at line 2546 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC7_MISC

| #define MSR_IA32_MC7_MISC 0x0000041F |

Definition at line 3650 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC7_STATUS

| #define MSR_IA32_MC7_STATUS 0x0000041D |

Definition at line 3498 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC8_ADDR

| #define MSR_IA32_MC8_ADDR 0x00000422 |

Definition at line 3575 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC8_CTL

| #define MSR_IA32_MC8_CTL 0x00000420 |

Definition at line 3423 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC8_CTL2

| #define MSR_IA32_MC8_CTL2 0x00000288 |

Definition at line 2547 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC8_MISC

| #define MSR_IA32_MC8_MISC 0x00000423 |

Definition at line 3651 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC8_STATUS

| #define MSR_IA32_MC8_STATUS 0x00000421 |

Definition at line 3499 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC9_ADDR

| #define MSR_IA32_MC9_ADDR 0x00000426 |

Definition at line 3576 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC9_CTL

| #define MSR_IA32_MC9_CTL 0x00000424 |

Definition at line 3424 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC9_CTL2

| #define MSR_IA32_MC9_CTL2 0x00000289 |

Definition at line 2548 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC9_MISC

| #define MSR_IA32_MC9_MISC 0x00000427 |

Definition at line 3652 of file ArchitecturalMsr.h.

◆ MSR_IA32_MC9_STATUS

| #define MSR_IA32_MC9_STATUS 0x00000425 |

Definition at line 3500 of file ArchitecturalMsr.h.

◆ MSR_IA32_MCG_CAP

| #define MSR_IA32_MCG_CAP 0x00000179 |

Global Machine Check Capability (RO). Introduced at Display Family / Display Model 06_01H.

- Parameters

-

ECX MSR_IA32_MCG_CAP (0x00000179) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_MCG_CAP_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_MCG_CAP_REGISTER.

Example usage

- Note

- MSR_IA32_MCG_CAP is defined as IA32_MCG_CAP in SDM.

Definition at line 784 of file ArchitecturalMsr.h.

◆ MSR_IA32_MCG_CTL

| #define MSR_IA32_MCG_CTL 0x0000017B |

Global Machine Check Control (R/W). If IA32_MCG_CAP.CTL_P[8] =1.

- Parameters

-

ECX MSR_IA32_MCG_CTL (0x0000017B) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MCG_CTL is defined as IA32_MCG_CTL in SDM.

Definition at line 935 of file ArchitecturalMsr.h.

◆ MSR_IA32_MCG_EXT_CTL

| #define MSR_IA32_MCG_EXT_CTL 0x000004D0 |

(R/W). If IA32_MCG_CAP.LMCE_P =1.

- Parameters

-

ECX MSR_IA32_MCG_EXT_CTL (0x000004D0) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_MCG_EXT_CTL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_MCG_EXT_CTL_REGISTER.

Example usage

- Note

- MSR_IA32_MCG_EXT_CTL is defined as IA32_MCG_EXT_CTL in SDM.

Definition at line 4259 of file ArchitecturalMsr.h.

◆ MSR_IA32_MCG_STATUS

| #define MSR_IA32_MCG_STATUS 0x0000017A |

Global Machine Check Status (R/W0). Introduced at Display Family / Display Model 06_01H.

- Parameters

-

ECX MSR_IA32_MCG_STATUS (0x0000017A) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_MCG_STATUS_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_MCG_STATUS_REGISTER.

Example usage

- Note

- MSR_IA32_MCG_STATUS is defined as IA32_MCG_STATUS in SDM.

Definition at line 877 of file ArchitecturalMsr.h.

◆ MSR_IA32_MISC_ENABLE

| #define MSR_IA32_MISC_ENABLE 0x000001A0 |

Enable Misc. Processor Features (R/W) Allows a variety of processor functions to be enabled and disabled.

- Parameters

-

ECX MSR_IA32_MISC_ENABLE (0x000001A0) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_MISC_ENABLE_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_MISC_ENABLE_REGISTER.

Example usage

- Note

- MSR_IA32_MISC_ENABLE is defined as IA32_MISC_ENABLE in SDM.

Definition at line 1411 of file ArchitecturalMsr.h.

◆ MSR_IA32_MONITOR_FILTER_SIZE

| #define MSR_IA32_MONITOR_FILTER_SIZE 0x00000006 |

See Section 8.10.5, "Monitor/Mwait Address Range Determination.". Introduced at Display Family / Display Model 0F_03H.

- Parameters

-

ECX MSR_IA32_MONITOR_FILTER_SIZE (0x00000006) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MONITOR_FILTER_SIZE is defined as IA32_MONITOR_FILTER_SIZE in SDM.

Definition at line 74 of file ArchitecturalMsr.h.

◆ MSR_IA32_MPERF

| #define MSR_IA32_MPERF 0x000000E7 |

TSC Frequency Clock Counter (R/Write to clear). If CPUID.06H: ECX[0] = 1. C0_MCNT: C0 TSC Frequency Clock Count Increments at fixed interval (relative to TSC freq.) when the logical processor is in C0. Cleared upon overflow / wrap-around of IA32_APERF.

- Parameters

-

ECX MSR_IA32_MPERF (0x000000E7) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MPERF is defined as IA32_MPERF in SDM.

Definition at line 603 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_DEF_TYPE

| #define MSR_IA32_MTRR_DEF_TYPE 0x000002FF |

MTRRdefType (R/W). If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_DEF_TYPE (0x000002FF) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_MTRR_DEF_TYPE_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_MTRR_DEF_TYPE_REGISTER.

Example usage

- Note

- MSR_IA32_MTRR_DEF_TYPE is defined as IA32_MTRR_DEF_TYPE in SDM.

Definition at line 2622 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX16K_80000

| #define MSR_IA32_MTRR_FIX16K_80000 0x00000258 |

MTRRfix16K_80000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX16K_80000 (0x00000258) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX16K_80000 is defined as IA32_MTRR_FIX16K_80000 in SDM.

Definition at line 2249 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX16K_A0000

| #define MSR_IA32_MTRR_FIX16K_A0000 0x00000259 |

MTRRfix16K_A0000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX16K_A0000 (0x00000259) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX16K_A0000 is defined as IA32_MTRR_FIX16K_A0000 in SDM.

Definition at line 2267 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX4K_C0000

| #define MSR_IA32_MTRR_FIX4K_C0000 0x00000268 |

See Section 11.11.2.2, "Fixed Range MTRRs.". If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX4K_C0000 (0x00000268) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX4K_C0000 is defined as IA32_MTRR_FIX4K_C0000 in SDM.

Definition at line 2285 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX4K_C8000

| #define MSR_IA32_MTRR_FIX4K_C8000 0x00000269 |

MTRRfix4K_C8000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX4K_C8000 (0x00000269) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX4K_C8000 is defined as IA32_MTRR_FIX4K_C8000 in SDM.

Definition at line 2303 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX4K_D0000

| #define MSR_IA32_MTRR_FIX4K_D0000 0x0000026A |

MTRRfix4K_D0000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX4K_D0000 (0x0000026A) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX4K_D0000 is defined as IA32_MTRR_FIX4K_D0000 in SDM.

Definition at line 2321 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX4K_D8000

| #define MSR_IA32_MTRR_FIX4K_D8000 0x0000026B |

MTRRfix4K_D8000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX4K_D8000 (0x0000026B) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX4K_D8000 is defined as IA32_MTRR_FIX4K_D8000 in SDM.

Definition at line 2339 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX4K_E0000

| #define MSR_IA32_MTRR_FIX4K_E0000 0x0000026C |

MTRRfix4K_E0000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX4K_E0000 (0x0000026C) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX4K_E0000 is defined as IA32_MTRR_FIX4K_E0000 in SDM.

Definition at line 2357 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX4K_E8000

| #define MSR_IA32_MTRR_FIX4K_E8000 0x0000026D |

MTRRfix4K_E8000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX4K_E8000 (0x0000026D) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX4K_E8000 is defined as IA32_MTRR_FIX4K_E8000 in SDM.

Definition at line 2375 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX4K_F0000

| #define MSR_IA32_MTRR_FIX4K_F0000 0x0000026E |

MTRRfix4K_F0000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX4K_F0000 (0x0000026E) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX4K_F0000 is defined as IA32_MTRR_FIX4K_F0000 in SDM.

Definition at line 2393 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX4K_F8000

| #define MSR_IA32_MTRR_FIX4K_F8000 0x0000026F |

MTRRfix4K_F8000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX4K_F8000 (0x0000026F) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX4K_F8000 is defined as IA32_MTRR_FIX4K_F8000 in SDM.

Definition at line 2411 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_FIX64K_00000

| #define MSR_IA32_MTRR_FIX64K_00000 0x00000250 |

MTRRfix64K_00000. If CPUID.01H: EDX.MTRR[12] =1.

- Parameters

-

ECX MSR_IA32_MTRR_FIX64K_00000 (0x00000250) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_MTRR_FIX64K_00000 is defined as IA32_MTRR_FIX64K_00000 in SDM.

Definition at line 2231 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE0

| #define MSR_IA32_MTRR_PHYSBASE0 0x00000200 |

MTRRphysBasen. See Section 11.11.2.3, "Variable Range MTRRs". If CPUID.01H: EDX.MTRR[12] = 1 and IA32_MTRRCAP[7:0] > n.

- Parameters

-

ECX MSR_IA32_MTRR_PHYSBASEn EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_MTRR_PHYSBASE_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_MTRR_PHYSBASE_REGISTER.

Example usage

- Note

- MSR_IA32_MTRR_PHYSBASE0 is defined as IA32_MTRR_PHYSBASE0 in SDM. MSR_IA32_MTRR_PHYSBASE1 is defined as IA32_MTRR_PHYSBASE1 in SDM. MSR_IA32_MTRR_PHYSBASE2 is defined as IA32_MTRR_PHYSBASE2 in SDM. MSR_IA32_MTRR_PHYSBASE3 is defined as IA32_MTRR_PHYSBASE3 in SDM. MSR_IA32_MTRR_PHYSBASE4 is defined as IA32_MTRR_PHYSBASE4 in SDM. MSR_IA32_MTRR_PHYSBASE5 is defined as IA32_MTRR_PHYSBASE5 in SDM. MSR_IA32_MTRR_PHYSBASE6 is defined as IA32_MTRR_PHYSBASE6 in SDM. MSR_IA32_MTRR_PHYSBASE7 is defined as IA32_MTRR_PHYSBASE7 in SDM. MSR_IA32_MTRR_PHYSBASE8 is defined as IA32_MTRR_PHYSBASE8 in SDM. MSR_IA32_MTRR_PHYSBASE9 is defined as IA32_MTRR_PHYSBASE9 in SDM.

Definition at line 2094 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE1

| #define MSR_IA32_MTRR_PHYSBASE1 0x00000202 |

Definition at line 2095 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE2

| #define MSR_IA32_MTRR_PHYSBASE2 0x00000204 |

Definition at line 2096 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE3

| #define MSR_IA32_MTRR_PHYSBASE3 0x00000206 |

Definition at line 2097 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE4

| #define MSR_IA32_MTRR_PHYSBASE4 0x00000208 |

Definition at line 2098 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE5

| #define MSR_IA32_MTRR_PHYSBASE5 0x0000020A |

Definition at line 2099 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE6

| #define MSR_IA32_MTRR_PHYSBASE6 0x0000020C |

Definition at line 2100 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE7

| #define MSR_IA32_MTRR_PHYSBASE7 0x0000020E |

Definition at line 2101 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE8

| #define MSR_IA32_MTRR_PHYSBASE8 0x00000210 |

Definition at line 2102 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSBASE9

| #define MSR_IA32_MTRR_PHYSBASE9 0x00000212 |

Definition at line 2103 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK0

| #define MSR_IA32_MTRR_PHYSMASK0 0x00000201 |

MTRRphysMaskn. See Section 11.11.2.3, "Variable Range MTRRs". If CPUID.01H: EDX.MTRR[12] = 1 and IA32_MTRRCAP[7:0] > n.

- Parameters

-

ECX MSR_IA32_MTRR_PHYSMASKn EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_MTRR_PHYSMASK_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_MTRR_PHYSMASK_REGISTER.

Example usage

- Note

- MSR_IA32_MTRR_PHYSMASK0 is defined as IA32_MTRR_PHYSMASK0 in SDM. MSR_IA32_MTRR_PHYSMASK1 is defined as IA32_MTRR_PHYSMASK1 in SDM. MSR_IA32_MTRR_PHYSMASK2 is defined as IA32_MTRR_PHYSMASK2 in SDM. MSR_IA32_MTRR_PHYSMASK3 is defined as IA32_MTRR_PHYSMASK3 in SDM. MSR_IA32_MTRR_PHYSMASK4 is defined as IA32_MTRR_PHYSMASK4 in SDM. MSR_IA32_MTRR_PHYSMASK5 is defined as IA32_MTRR_PHYSMASK5 in SDM. MSR_IA32_MTRR_PHYSMASK6 is defined as IA32_MTRR_PHYSMASK6 in SDM. MSR_IA32_MTRR_PHYSMASK7 is defined as IA32_MTRR_PHYSMASK7 in SDM. MSR_IA32_MTRR_PHYSMASK8 is defined as IA32_MTRR_PHYSMASK8 in SDM. MSR_IA32_MTRR_PHYSMASK9 is defined as IA32_MTRR_PHYSMASK9 in SDM.

Definition at line 2169 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK1

| #define MSR_IA32_MTRR_PHYSMASK1 0x00000203 |

Definition at line 2170 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK2

| #define MSR_IA32_MTRR_PHYSMASK2 0x00000205 |

Definition at line 2171 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK3

| #define MSR_IA32_MTRR_PHYSMASK3 0x00000207 |

Definition at line 2172 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK4

| #define MSR_IA32_MTRR_PHYSMASK4 0x00000209 |

Definition at line 2173 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK5

| #define MSR_IA32_MTRR_PHYSMASK5 0x0000020B |

Definition at line 2174 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK6

| #define MSR_IA32_MTRR_PHYSMASK6 0x0000020D |

Definition at line 2175 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK7

| #define MSR_IA32_MTRR_PHYSMASK7 0x0000020F |

Definition at line 2176 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK8

| #define MSR_IA32_MTRR_PHYSMASK8 0x00000211 |

Definition at line 2177 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRR_PHYSMASK9

| #define MSR_IA32_MTRR_PHYSMASK9 0x00000213 |

Definition at line 2178 of file ArchitecturalMsr.h.

◆ MSR_IA32_MTRRCAP

| #define MSR_IA32_MTRRCAP 0x000000FE |

MTRR Capability (RO) Section 11.11.2.1, "IA32_MTRR_DEF_TYPE MSR.". Introduced at Display Family / Display Model 06_01H.

- Parameters

-

ECX MSR_IA32_MTRRCAP (0x000000FE) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_MTRRCAP_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_MTRRCAP_REGISTER.

Example usage

- Note

- MSR_IA32_MTRRCAP is defined as IA32_MTRRCAP in SDM.

Definition at line 644 of file ArchitecturalMsr.h.

◆ MSR_IA32_P5_MC_ADDR

| #define MSR_IA32_P5_MC_ADDR 0x00000000 |

See Section 2.22, "MSRs in Pentium Processors.". Pentium Processor (05_01H).

- Parameters

-

ECX MSR_IA32_P5_MC_ADDR (0x00000000) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_P5_MC_ADDR is defined as IA32_P5_MC_ADDR in SDM.

Definition at line 37 of file ArchitecturalMsr.h.

◆ MSR_IA32_P5_MC_TYPE

| #define MSR_IA32_P5_MC_TYPE 0x00000001 |

See Section 2.22, "MSRs in Pentium Processors.". DF_DM = 05_01H.

- Parameters

-

ECX MSR_IA32_P5_MC_TYPE (0x00000001) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_P5_MC_TYPE is defined as IA32_P5_MC_TYPE in SDM.

Definition at line 55 of file ArchitecturalMsr.h.

◆ MSR_IA32_PACKAGE_THERM_INTERRUPT

| #define MSR_IA32_PACKAGE_THERM_INTERRUPT 0x000001B2 |

Pkg Thermal Interrupt Control (R/W) Enables and disables the generation of an interrupt on temperature transitions detected with the package's thermal sensor. See Section 14.8, "Package Level Thermal Management.". If CPUID.06H: EAX[6] = 1.

- Parameters

-

ECX MSR_IA32_PACKAGE_THERM_INTERRUPT (0x000001B2) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PACKAGE_THERM_INTERRUPT_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PACKAGE_THERM_INTERRUPT_REGISTER.

Example usage

- Note

- MSR_IA32_PACKAGE_THERM_INTERRUPT is defined as IA32_PACKAGE_THERM_INTERRUPT in SDM.

Definition at line 1685 of file ArchitecturalMsr.h.

◆ MSR_IA32_PACKAGE_THERM_STATUS

| #define MSR_IA32_PACKAGE_THERM_STATUS 0x000001B1 |

Package Thermal Status Information (RO) Contains status information about the package's thermal sensor. See Section 14.8, "Package Level Thermal Management.". If CPUID.06H: EAX[6] = 1.

- Parameters

-

ECX MSR_IA32_PACKAGE_THERM_STATUS (0x000001B1) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PACKAGE_THERM_STATUS_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PACKAGE_THERM_STATUS_REGISTER.

Example usage

- Note

- MSR_IA32_PACKAGE_THERM_STATUS is defined as IA32_PACKAGE_THERM_STATUS in SDM.

Definition at line 1588 of file ArchitecturalMsr.h.

◆ MSR_IA32_PAT

| #define MSR_IA32_PAT 0x00000277 |

IA32_PAT (R/W). If CPUID.01H: EDX.MTRR[16] =1.

- Parameters

-

ECX MSR_IA32_PAT (0x00000277) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PAT_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PAT_REGISTER.

Example usage

- Note

- MSR_IA32_PAT is defined as IA32_PAT in SDM.

Definition at line 2431 of file ArchitecturalMsr.h.

◆ MSR_IA32_PEBS_ENABLE

| #define MSR_IA32_PEBS_ENABLE 0x000003F1 |

PEBS Control (R/W).

- Parameters

-

ECX MSR_IA32_PEBS_ENABLE (0x000003F1) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PEBS_ENABLE_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PEBS_ENABLE_REGISTER.

Example usage

- Note

- MSR_IA32_PEBS_ENABLE is defined as IA32_PEBS_ENABLE in SDM.

Definition at line 3338 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERF_CAPABILITIES

| #define MSR_IA32_PERF_CAPABILITIES 0x00000345 |

RO. If CPUID.01H: ECX[15] = 1.

- Parameters

-

ECX MSR_IA32_PERF_CAPABILITIES (0x00000345) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERF_CAPABILITIES_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERF_CAPABILITIES_REGISTER.

Example usage

- Note

- MSR_IA32_PERF_CAPABILITIES is defined as IA32_PERF_CAPABILITIES in SDM.

Definition at line 2733 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERF_CTL

| #define MSR_IA32_PERF_CTL 0x00000199 |

(R/W). Introduced at Display Family / Display Model 0F_03H.

- Parameters

-

ECX MSR_IA32_PERF_CTL (0x00000199) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERF_CTL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERF_CTL_REGISTER.

Example usage

- Note

- MSR_IA32_PERF_CTL is defined as IA32_PERF_CTL in SDM.

Definition at line 1101 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERF_GLOBAL_CTRL

| #define MSR_IA32_PERF_GLOBAL_CTRL 0x0000038F |

Global Performance Counter Control (R/W) Counter increments while the result of ANDing respective enable bit in this MSR with the corresponding OS or USR bits in the general-purpose or fixed counter control MSR is true. If CPUID.0AH: EAX[7:0] > 0.

- Parameters

-

ECX MSR_IA32_PERF_GLOBAL_CTRL (0x0000038F) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_CTRL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_CTRL_REGISTER.

Example usage

- Note

- MSR_IA32_PERF_GLOBAL_CTRL is defined as IA32_PERF_GLOBAL_CTRL in SDM.

Definition at line 3016 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERF_GLOBAL_INUSE

| #define MSR_IA32_PERF_GLOBAL_INUSE 0x00000392 |

Indicator of core perfmon interface is in use (RO). If CPUID.0AH: EAX[7:0] > 3.

- Parameters

-

ECX MSR_IA32_PERF_GLOBAL_INUSE (0x00000392) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_INUSE_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_INUSE_REGISTER.

Example usage

- Note

- MSR_IA32_PERF_GLOBAL_INUSE is defined as IA32_PERF_GLOBAL_INUSE in SDM.

Definition at line 3286 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERF_GLOBAL_OVF_CTRL

| #define MSR_IA32_PERF_GLOBAL_OVF_CTRL 0x00000390 |

Global Performance Counter Overflow Control (R/W). If CPUID.0AH: EAX[7:0] > 0 && CPUID.0AH: EAX[7:0] <= 3.

- Parameters

-

ECX MSR_IA32_PERF_GLOBAL_OVF_CTRL (0x00000390) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_OVF_CTRL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_OVF_CTRL_REGISTER.

Example usage

- Note

- MSR_IA32_PERF_GLOBAL_OVF_CTRL is defined as IA32_PERF_GLOBAL_OVF_CTRL in SDM.

Definition at line 3064 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERF_GLOBAL_STATUS

| #define MSR_IA32_PERF_GLOBAL_STATUS 0x0000038E |

Global Performance Counter Status (RO). If CPUID.0AH: EAX[7:0] > 0.

- Parameters

-

ECX MSR_IA32_PERF_GLOBAL_STATUS (0x0000038E) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_STATUS_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_STATUS_REGISTER.

Example usage

- Note

- MSR_IA32_PERF_GLOBAL_STATUS is defined as IA32_PERF_GLOBAL_STATUS in SDM.

Definition at line 2901 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERF_GLOBAL_STATUS_RESET

| #define MSR_IA32_PERF_GLOBAL_STATUS_RESET 0x00000390 |

Global Performance Counter Overflow Reset Control (R/W). If CPUID.0AH: EAX[7:0] > 3.

- Parameters

-

ECX MSR_IA32_PERF_GLOBAL_STATUS_RESET (0x00000390) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_STATUS_RESET_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_STATUS_RESET_REGISTER.

Example usage

- Note

- MSR_IA32_PERF_GLOBAL_STATUS_RESET is defined as IA32_PERF_GLOBAL_STATUS_RESET in SDM.

Definition at line 3132 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERF_GLOBAL_STATUS_SET

| #define MSR_IA32_PERF_GLOBAL_STATUS_SET 0x00000391 |

Global Performance Counter Overflow Set Control (R/W). If CPUID.0AH: EAX[7:0] > 3.

- Parameters

-

ECX MSR_IA32_PERF_GLOBAL_STATUS_SET (0x00000391) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER.

Example usage

- Note

- MSR_IA32_PERF_GLOBAL_STATUS_SET is defined as IA32_PERF_GLOBAL_STATUS_SET in SDM.

Definition at line 3212 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERF_STATUS

| #define MSR_IA32_PERF_STATUS 0x00000198 |

Current performance state(P-State) operating point (RO). Introduced at Display Family / Display Model 0F_03H.

- Parameters

-

ECX MSR_IA32_PERF_STATUS (0x00000198) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERF_STATUS_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERF_STATUS_REGISTER.

Example usage

- Note

- MSR_IA32_PERF_STATUS is defined as IA32_PERF_STATUS in SDM.

Definition at line 1056 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERFEVTSEL0

| #define MSR_IA32_PERFEVTSEL0 0x00000186 |

Performance Event Select Register n (R/W). If CPUID.0AH: EAX[15:8] > n.

- Parameters

-

ECX MSR_IA32_PERFEVTSELn EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PERFEVTSEL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PERFEVTSEL_REGISTER.

Example usage

- Note

- MSR_IA32_PERFEVTSEL0 is defined as IA32_PERFEVTSEL0 in SDM. MSR_IA32_PERFEVTSEL1 is defined as IA32_PERFEVTSEL1 in SDM. MSR_IA32_PERFEVTSEL2 is defined as IA32_PERFEVTSEL2 in SDM. MSR_IA32_PERFEVTSEL3 is defined as IA32_PERFEVTSEL3 in SDM.

Definition at line 959 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERFEVTSEL1

| #define MSR_IA32_PERFEVTSEL1 0x00000187 |

Definition at line 960 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERFEVTSEL2

| #define MSR_IA32_PERFEVTSEL2 0x00000188 |

Definition at line 961 of file ArchitecturalMsr.h.

◆ MSR_IA32_PERFEVTSEL3

| #define MSR_IA32_PERFEVTSEL3 0x00000189 |

Definition at line 962 of file ArchitecturalMsr.h.

◆ MSR_IA32_PKG_HDC_CTL

| #define MSR_IA32_PKG_HDC_CTL 0x00000DB0 |

Package Level Enable/disable HDC (R/W). If CPUID.06H:EAX.[13] = 1.

- Parameters

-

ECX MSR_IA32_PKG_HDC_CTL (0x00000DB0) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PKG_HDC_CTL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PKG_HDC_CTL_REGISTER.

Example usage

- Note

- MSR_IA32_PKG_HDC_CTL is defined as IA32_PKG_HDC_CTL in SDM.

Definition at line 6202 of file ArchitecturalMsr.h.

◆ MSR_IA32_PLATFORM_DCA_CAP

| #define MSR_IA32_PLATFORM_DCA_CAP 0x000001F8 |

DCA Capability (R). If CPUID.01H: ECX[18] = 1.

- Parameters

-

ECX MSR_IA32_PLATFORM_DCA_CAP (0x000001F8) EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_PLATFORM_DCA_CAP is defined as IA32_PLATFORM_DCA_CAP in SDM.

Definition at line 1971 of file ArchitecturalMsr.h.

◆ MSR_IA32_PLATFORM_ID

| #define MSR_IA32_PLATFORM_ID 0x00000017 |

Platform ID (RO) The operating system can use this MSR to determine "slot" information for the processor and the proper microcode update to load. Introduced at Display Family / Display Model 06_01H.

- Parameters

-

ECX MSR_IA32_PLATFORM_ID (0x00000017) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PLATFORM_ID_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PLATFORM_ID_REGISTER.

Example usage

- Note

- MSR_IA32_PLATFORM_ID is defined as IA32_PLATFORM_ID in SDM.

Definition at line 114 of file ArchitecturalMsr.h.

◆ MSR_IA32_PM_CTL1

| #define MSR_IA32_PM_CTL1 0x00000DB1 |

Enable/disable HWP (R/W). If CPUID.06H:EAX.[13] = 1.

- Parameters

-

ECX MSR_IA32_PM_CTL1 (0x00000DB1) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PM_CTL1_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PM_CTL1_REGISTER.

Example usage

- Note

- MSR_IA32_PM_CTL1 is defined as IA32_PM_CTL1 in SDM.

Definition at line 6249 of file ArchitecturalMsr.h.

◆ MSR_IA32_PM_ENABLE

| #define MSR_IA32_PM_ENABLE 0x00000770 |

Enable/disable HWP (R/W). If CPUID.06H:EAX.[7] = 1.

- Parameters

-

ECX MSR_IA32_PM_ENABLE (0x00000770) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PM_ENABLE_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PM_ENABLE_REGISTER.

Example usage

- Note

- MSR_IA32_PM_ENABLE is defined as IA32_PM_ENABLE in SDM.

Definition at line 4885 of file ArchitecturalMsr.h.

◆ MSR_IA32_PMC0

| #define MSR_IA32_PMC0 0x000000C1 |

General Performance Counters (R/W). MSR_IA32_PMCn is supported if CPUID.0AH: EAX[15:8] > n.

- Parameters

-

ECX MSR_IA32_PMCn EAX Lower 32-bits of MSR value. EDX Upper 32-bits of MSR value.

Example usage

- Note

- MSR_IA32_PMC0 is defined as IA32_PMC0 in SDM. MSR_IA32_PMC1 is defined as IA32_PMC1 in SDM. MSR_IA32_PMC2 is defined as IA32_PMC2 in SDM. MSR_IA32_PMC3 is defined as IA32_PMC3 in SDM. MSR_IA32_PMC4 is defined as IA32_PMC4 in SDM. MSR_IA32_PMC5 is defined as IA32_PMC5 in SDM. MSR_IA32_PMC6 is defined as IA32_PMC6 in SDM. MSR_IA32_PMC7 is defined as IA32_PMC7 in SDM.

Definition at line 574 of file ArchitecturalMsr.h.

◆ MSR_IA32_PMC1

| #define MSR_IA32_PMC1 0x000000C2 |

Definition at line 575 of file ArchitecturalMsr.h.

◆ MSR_IA32_PMC2

| #define MSR_IA32_PMC2 0x000000C3 |

Definition at line 576 of file ArchitecturalMsr.h.

◆ MSR_IA32_PMC3

| #define MSR_IA32_PMC3 0x000000C4 |

Definition at line 577 of file ArchitecturalMsr.h.

◆ MSR_IA32_PMC4

| #define MSR_IA32_PMC4 0x000000C5 |

Definition at line 578 of file ArchitecturalMsr.h.

◆ MSR_IA32_PMC5

| #define MSR_IA32_PMC5 0x000000C6 |

Definition at line 579 of file ArchitecturalMsr.h.

◆ MSR_IA32_PMC6

| #define MSR_IA32_PMC6 0x000000C7 |

Definition at line 580 of file ArchitecturalMsr.h.

◆ MSR_IA32_PMC7

| #define MSR_IA32_PMC7 0x000000C8 |

Definition at line 581 of file ArchitecturalMsr.h.

◆ MSR_IA32_PQR_ASSOC

| #define MSR_IA32_PQR_ASSOC 0x00000C8F |

Resource Association Register (R/W). If ( (CPUID.(EAX=07H, ECX=0):EBX[12] =1) or (CPUID.(EAX=07H, ECX=0):EBX[15] =1 ) ).

- Parameters

-

ECX MSR_IA32_PQR_ASSOC (0x00000C8F) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_PQR_ASSOC_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_PQR_ASSOC_REGISTER.

Example usage

- Note

- MSR_IA32_PQR_ASSOC is defined as IA32_PQR_ASSOC in SDM.

Definition at line 6055 of file ArchitecturalMsr.h.

◆ MSR_IA32_QM_CTR

| #define MSR_IA32_QM_CTR 0x00000C8E |

Monitoring Counter Register (R/O). If ( CPUID.(EAX=07H, ECX=0):EBX.[12] = 1 ).

- Parameters

-

ECX MSR_IA32_QM_CTR (0x00000C8E) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_QM_CTR_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_QM_CTR_REGISTER.

Example usage

- Note

- MSR_IA32_QM_CTR is defined as IA32_QM_CTR in SDM.

Definition at line 6001 of file ArchitecturalMsr.h.

◆ MSR_IA32_QM_EVTSEL

| #define MSR_IA32_QM_EVTSEL 0x00000C8D |

Monitoring Event Select Register (R/W). If ( CPUID.(EAX=07H, ECX=0):EBX.[12] = 1 ).

- Parameters

-

ECX MSR_IA32_QM_EVTSEL (0x00000C8D) EAX Lower 32-bits of MSR value. Described by the type MSR_IA32_QM_EVTSEL_REGISTER. EDX Upper 32-bits of MSR value. Described by the type MSR_IA32_QM_EVTSEL_REGISTER.

Example usage

- Note