#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 HighTempEnable: 1 | |

| UINT32 LowTempEnable: 1 | |

| UINT32 PROCHOT_Enable: 1 | |

| UINT32 FORCEPR_Enable: 1 | |

| UINT32 CriticalTempEnable: 1 | |

| UINT32 Reserved1: 3 | |

| UINT32 Threshold1: 7 | |

| UINT32 Threshold1Enable: 1 | |

| UINT32 Threshold2: 7 | |

| UINT32 Threshold2Enable: 1 | |

| UINT32 PowerLimitNotificationEnable: 1 | |

| UINT32 Reserved2: 7 | |

| UINT32 Reserved3: 32 | |

| } | Bits |

| UINT32 | Uint32 |

| UINT64 | Uint64 |

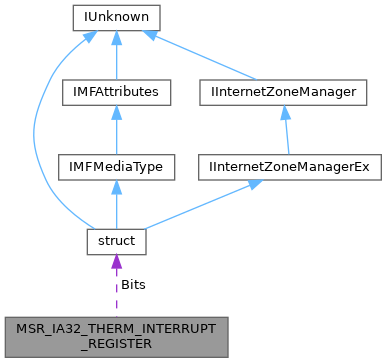

Detailed Description

MSR information returned for MSR index MSR_IA32_THERM_INTERRUPT

Definition at line 1212 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } MSR_IA32_THERM_INTERRUPT_REGISTER::Bits |

Individual bit fields

◆ CriticalTempEnable

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::CriticalTempEnable |

[Bit 4] Critical Temperature Interrupt Enable. If CPUID.01H:EDX[22] = 1.

Definition at line 1237 of file ArchitecturalMsr.h.

◆ FORCEPR_Enable

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::FORCEPR_Enable |

[Bit 3] FORCEPR# Interrupt Enable. If CPUID.01H:EDX[22] = 1.

Definition at line 1232 of file ArchitecturalMsr.h.

◆ HighTempEnable

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::HighTempEnable |

[Bit 0] High-Temperature Interrupt Enable. If CPUID.01H:EDX[22] = 1.

Definition at line 1220 of file ArchitecturalMsr.h.

◆ LowTempEnable

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::LowTempEnable |

[Bit 1] Low-Temperature Interrupt Enable. If CPUID.01H:EDX[22] = 1.

Definition at line 1224 of file ArchitecturalMsr.h.

◆ PowerLimitNotificationEnable

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::PowerLimitNotificationEnable |

[Bit 24] Power Limit Notification Enable. If CPUID.06H:EAX[4] = 1.

Definition at line 1258 of file ArchitecturalMsr.h.

◆ PROCHOT_Enable

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::PROCHOT_Enable |

[Bit 2] PROCHOT# Interrupt Enable. If CPUID.01H:EDX[22] = 1.

Definition at line 1228 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::Reserved1 |

Definition at line 1238 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::Reserved2 |

Definition at line 1259 of file ArchitecturalMsr.h.

◆ Reserved3

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::Reserved3 |

Definition at line 1260 of file ArchitecturalMsr.h.

◆ Threshold1

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::Threshold1 |

[Bits 14:8] Threshold #1 Value. If CPUID.01H:EDX[22] = 1.

Definition at line 1242 of file ArchitecturalMsr.h.

◆ Threshold1Enable

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::Threshold1Enable |

[Bit 15] Threshold #1 Interrupt Enable. If CPUID.01H:EDX[22] = 1.

Definition at line 1246 of file ArchitecturalMsr.h.

◆ Threshold2

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::Threshold2 |

[Bits 22:16] Threshold #2 Value. If CPUID.01H:EDX[22] = 1.

Definition at line 1250 of file ArchitecturalMsr.h.

◆ Threshold2Enable

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::Threshold2Enable |

[Bit 23] Threshold #2 Interrupt Enable. If CPUID.01H:EDX[22] = 1.

Definition at line 1254 of file ArchitecturalMsr.h.

◆ Uint32

| UINT32 MSR_IA32_THERM_INTERRUPT_REGISTER::Uint32 |

All bit fields as a 32-bit value

Definition at line 1265 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_THERM_INTERRUPT_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 1269 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h