#include <ArchitecturalMsr.h>

Public Attributes | |

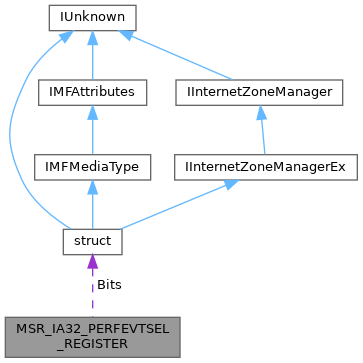

| struct { | |

| UINT32 EventSelect: 8 | |

| UINT32 UMASK: 8 | |

| UINT32 USR: 1 | |

| UINT32 OS: 1 | |

| UINT32 E: 1 | |

| UINT32 PC: 1 | |

| UINT32 INT: 1 | |

| UINT32 ANY: 1 | |

| UINT32 EN: 1 | |

| UINT32 INV: 1 | |

| UINT32 CMASK: 8 | |

| UINT32 Reserved: 32 | |

| } | Bits |

| UINT32 | Uint32 |

| UINT64 | Uint64 |

Detailed Description

MSR information returned for MSR indexes MSR_IA32_PERFEVTSEL0 to MSR_IA32_PERFEVTSEL3

Definition at line 969 of file ArchitecturalMsr.h.

Member Data Documentation

◆ ANY

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::ANY |

[Bit 21] AnyThread: When set to 1, it enables counting the associated event conditions occurring across all logical processors sharing a processor core. When set to 0, the counter only increments the associated event conditions occurring in the logical processor which programmed the MSR.

Definition at line 1010 of file ArchitecturalMsr.h.

◆

| struct { ... } MSR_IA32_PERFEVTSEL_REGISTER::Bits |

Individual bit fields

◆ CMASK

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::CMASK |

[Bits 31:24] CMASK: When CMASK is not zero, the corresponding performance counter increments each cycle if the event count is greater than or equal to the CMASK.

Definition at line 1025 of file ArchitecturalMsr.h.

◆ E

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::E |

[Bit 18] Edge: Enables edge detection if set.

Definition at line 994 of file ArchitecturalMsr.h.

◆ EN

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::EN |

[Bit 22] EN: enables the corresponding performance counter to commence counting when this bit is set.

Definition at line 1015 of file ArchitecturalMsr.h.

◆ EventSelect

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::EventSelect |

[Bits 7:0] Event Select: Selects a performance event logic unit.

Definition at line 977 of file ArchitecturalMsr.h.

◆ INT

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::INT |

[Bit 20] INT: enables interrupt on counter overflow.

Definition at line 1002 of file ArchitecturalMsr.h.

◆ INV

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::INV |

[Bit 23] INV: invert the CMASK.

Definition at line 1019 of file ArchitecturalMsr.h.

◆ OS

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::OS |

[Bit 17] OS: Counts while in privilege level is ring 0.

Definition at line 990 of file ArchitecturalMsr.h.

◆ PC

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::PC |

[Bit 19] PC: enables pin control.

Definition at line 998 of file ArchitecturalMsr.h.

◆ Reserved

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::Reserved |

Definition at line 1026 of file ArchitecturalMsr.h.

◆ Uint32

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::Uint32 |

All bit fields as a 32-bit value

Definition at line 1031 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_PERFEVTSEL_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 1035 of file ArchitecturalMsr.h.

◆ UMASK

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::UMASK |

[Bits 15:8] UMask: Qualifies the microarchitectural condition to detect on the selected event logic.

Definition at line 982 of file ArchitecturalMsr.h.

◆ USR

| UINT32 MSR_IA32_PERFEVTSEL_REGISTER::USR |

[Bit 16] USR: Counts while in privilege level is not ring 0.

Definition at line 986 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h