#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 Ovf_PMCn: 32 | |

| UINT32 Ovf_FIXED_CTRn: 23 | |

| UINT32 Trace_ToPA_PMI: 1 | |

| UINT32 Reserved2: 2 | |

| UINT32 LBR_Frz: 1 | |

| UINT32 CTR_Frz: 1 | |

| UINT32 ASCI: 1 | |

| UINT32 Ovf_Uncore: 1 | |

| UINT32 OvfBuf: 1 | |

| UINT32 Reserved3: 1 | |

| } | Bits |

| UINT64 | Uint64 |

Detailed Description

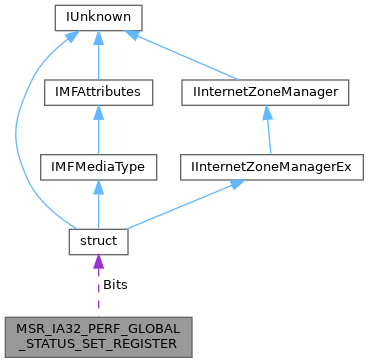

MSR information returned for MSR index MSR_IA32_PERF_GLOBAL_STATUS_SET

Definition at line 3217 of file ArchitecturalMsr.h.

Member Data Documentation

◆ ASCI

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::ASCI |

[Bit 60] Set 1 to cause ASCI = 1. If CPUID.0AH: EAX[7:0] > 3.

Definition at line 3251 of file ArchitecturalMsr.h.

◆

| struct { ... } MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::Bits |

Individual bit fields

◆ CTR_Frz

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::CTR_Frz |

[Bit 59] Set 1 to cause CTR_Frz = 1. If CPUID.0AH: EAX[7:0] > 3.

Definition at line 3247 of file ArchitecturalMsr.h.

◆ LBR_Frz

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::LBR_Frz |

[Bit 58] Set 1 to cause LBR_Frz = 1. If CPUID.0AH: EAX[7:0] > 3.

Definition at line 3243 of file ArchitecturalMsr.h.

◆ Ovf_FIXED_CTRn

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::Ovf_FIXED_CTRn |

[Bits 54:32] Set 1 to cause Ovf_FIXED_CTRn = 1. If CPUID.0AH: EAX[7:0] > n. Set bitmask. Only the first n-1 bits are valid. Bits 22:n are reserved.

Definition at line 3234 of file ArchitecturalMsr.h.

◆ Ovf_PMCn

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::Ovf_PMCn |

[Bits 31:0] Set 1 to cause Ovf_PMCn = 1. If CPUID.0AH: EAX[7:0] > n. Set bitmask. Only the first n-1 bits are valid. Bits 31:n are reserved.

Definition at line 3227 of file ArchitecturalMsr.h.

◆ Ovf_Uncore

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::Ovf_Uncore |

[Bit 61] Set 1 to cause Ovf_Uncore = 1. If CPUID.0AH: EAX[7:0] > 3.

Definition at line 3255 of file ArchitecturalMsr.h.

◆ OvfBuf

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::OvfBuf |

[Bit 62] Set 1 to cause OvfBuf = 1. If CPUID.0AH: EAX[7:0] > 3.

Definition at line 3259 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::Reserved2 |

Definition at line 3239 of file ArchitecturalMsr.h.

◆ Reserved3

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::Reserved3 |

Definition at line 3260 of file ArchitecturalMsr.h.

◆ Trace_ToPA_PMI

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::Trace_ToPA_PMI |

[Bit 55] Set 1 to cause Trace_ToPA_PMI = 1. If CPUID.0AH: EAX[7:0] > 3.

Definition at line 3238 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_PERF_GLOBAL_STATUS_SET_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 3265 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h