#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 VmxTimerRatio: 5 | |

| UINT32 VmExitEferLma: 1 | |

| UINT32 HltActivityStateSupported: 1 | |

| UINT32 ShutdownActivityStateSupported: 1 | |

| UINT32 WaitForSipiActivityStateSupported: 1 | |

| UINT32 Reserved1: 5 | |

| UINT32 ProcessorTraceSupported: 1 | |

| UINT32 SmBaseMsrSupported: 1 | |

| UINT32 NumberOfCr3TargetValues: 9 | |

| UINT32 MsrStoreListMaximum: 3 | |

| UINT32 BlockSmiSupported: 1 | |

| UINT32 VmWriteSupported: 1 | |

| UINT32 VmInjectSupported: 1 | |

| UINT32 Reserved2: 1 | |

| UINT32 MsegRevisionIdentifier: 32 | |

| } | Bits |

| UINT64 | Uint64 |

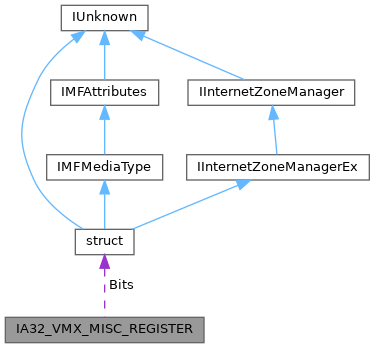

Detailed Description

MSR information returned for MSR index #IA32_VMX_MISC

Definition at line 3891 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } IA32_VMX_MISC_REGISTER::Bits |

Individual bit fields

◆ BlockSmiSupported

| UINT32 IA32_VMX_MISC_REGISTER::BlockSmiSupported |

[Bit 28] If read as 1, bit 2 of the IA32_SMM_MONITOR_CTL can be set to 1. VMXOFF unblocks SMIs unless IA32_SMM_MONITOR_CTL[bit 2] is 1 (see Section 34.14.4).

Definition at line 3960 of file ArchitecturalMsr.h.

◆ HltActivityStateSupported

| UINT32 IA32_VMX_MISC_REGISTER::HltActivityStateSupported |

[Bit 6] reports (if set) the support for activity state 1 (HLT).

Definition at line 3913 of file ArchitecturalMsr.h.

◆ MsegRevisionIdentifier

| UINT32 IA32_VMX_MISC_REGISTER::MsegRevisionIdentifier |

[Bits 63:32] Reports the 32-bit MSEG revision identifier used by the processor.

Definition at line 3978 of file ArchitecturalMsr.h.

◆ MsrStoreListMaximum

| UINT32 IA32_VMX_MISC_REGISTER::MsrStoreListMaximum |

[Bit 27:25] Bits 27:25 is used to compute the recommended maximum number of MSRs that should appear in the VM-exit MSR-store list, the VM-exit MSR-load list, or the VM-entry MSR-load list. Specifically, if the value bits 27:25 of IA32_VMX_MISC is N, then 512 * (N + 1) is the recommended maximum number of MSRs to be included in each list. If the limit is exceeded, undefined processor behavior may result (including a machine check during the VMX transition).

Definition at line 3954 of file ArchitecturalMsr.h.

◆ NumberOfCr3TargetValues

| UINT32 IA32_VMX_MISC_REGISTER::NumberOfCr3TargetValues |

[Bits 24:16] Indicate the number of CR3-target values supported by the processor. This number is a value between 0 and 256, inclusive (bit 24 is set if and only if bits 23:16 are clear).

Definition at line 3944 of file ArchitecturalMsr.h.

◆ ProcessorTraceSupported

| UINT32 IA32_VMX_MISC_REGISTER::ProcessorTraceSupported |

[Bit 14] If read as 1, Intel(R) Processor Trace (Intel PT) can be used in VMX operation. If the processor supports Intel PT but does not allow it to be used in VMX operation, execution of VMXON clears IA32_RTIT_CTL.TraceEn (see "VMXON-Enter VMX Operation" in Chapter 30); any attempt to set that bit while in VMX operation (including VMX root operation) using the WRMSR instruction causes a general-protection exception.

Definition at line 3932 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 IA32_VMX_MISC_REGISTER::Reserved1 |

Definition at line 3922 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 IA32_VMX_MISC_REGISTER::Reserved2 |

Definition at line 3973 of file ArchitecturalMsr.h.

◆ ShutdownActivityStateSupported

| UINT32 IA32_VMX_MISC_REGISTER::ShutdownActivityStateSupported |

[Bit 7] reports (if set) the support for activity state 2 (shutdown).

Definition at line 3917 of file ArchitecturalMsr.h.

◆ SmBaseMsrSupported

| UINT32 IA32_VMX_MISC_REGISTER::SmBaseMsrSupported |

[Bit 15] If read as 1, the RDMSR instruction can be used in system- management mode (SMM) to read the IA32_SMBASE MSR (MSR address 9EH). See Section 34.15.6.3.

Definition at line 3938 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 IA32_VMX_MISC_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 3983 of file ArchitecturalMsr.h.

◆ VmExitEferLma

| UINT32 IA32_VMX_MISC_REGISTER::VmExitEferLma |

[Bit 5] If bit 5 is read as 1, VM exits store the value of IA32_EFER.LMA into the "IA-32e mode guest" VM-entry control;see Section 27.2 for more details. This bit is read as 1 on any logical processor that supports the 1-setting of the "unrestricted guest" VM-execution control.

Definition at line 3909 of file ArchitecturalMsr.h.

◆ VmInjectSupported

| UINT32 IA32_VMX_MISC_REGISTER::VmInjectSupported |

[Bit 30] If read as 1, VM entry allows injection of a software interrupt, software exception, or privileged software exception with an instruction length of 0.

Definition at line 3972 of file ArchitecturalMsr.h.

◆ VmWriteSupported

| UINT32 IA32_VMX_MISC_REGISTER::VmWriteSupported |

[Bit 29] read as 1, software can use VMWRITE to write to any supported field in the VMCS; otherwise, VMWRITE cannot be used to modify VM-exit information fields.

Definition at line 3966 of file ArchitecturalMsr.h.

◆ VmxTimerRatio

| UINT32 IA32_VMX_MISC_REGISTER::VmxTimerRatio |

[Bits 4:0] Reports a value X that specifies the relationship between the rate of the VMX-preemption timer and that of the timestamp counter (TSC). Specifically, the VMX-preemption timer (if it is active) counts down by 1 every time bit X in the TSC changes due to a TSC increment.

Definition at line 3902 of file ArchitecturalMsr.h.

◆ WaitForSipiActivityStateSupported

| UINT32 IA32_VMX_MISC_REGISTER::WaitForSipiActivityStateSupported |

[Bit 8] reports (if set) the support for activity state 3 (wait-for-SIPI).

Definition at line 3921 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h