#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 Lock: 1 | |

| UINT32 EnableVmxInsideSmx: 1 | |

| UINT32 EnableVmxOutsideSmx: 1 | |

| UINT32 Reserved1: 5 | |

| UINT32 SenterLocalFunctionEnables: 7 | |

| UINT32 SenterGlobalEnable: 1 | |

| UINT32 Reserved2: 1 | |

| UINT32 SgxLaunchControlEnable: 1 | |

| UINT32 SgxEnable: 1 | |

| UINT32 Reserved3: 1 | |

| UINT32 LmceOn: 1 | |

| UINT32 Reserved4: 11 | |

| UINT32 Reserved5: 32 | |

| } | Bits |

| UINT32 | Uint32 |

| UINT64 | Uint64 |

Detailed Description

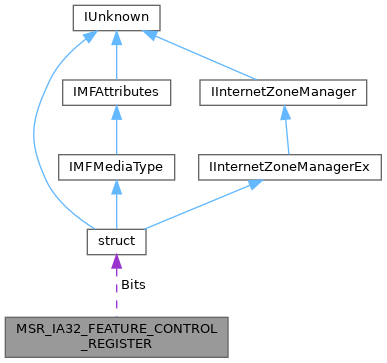

MSR information returned for MSR index MSR_IA32_FEATURE_CONTROL

Definition at line 231 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } MSR_IA32_FEATURE_CONTROL_REGISTER::Bits |

Individual bit fields

◆ EnableVmxInsideSmx

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::EnableVmxInsideSmx |

[Bit 1] Enable VMX inside SMX operation (R/WL): This bit enables a system executive to use VMX in conjunction with SMX to support Intel(R) Trusted Execution Technology. BIOS must set this bit only when the CPUID function 1 returns VMX feature flag and SMX feature flag set (ECX bits 5 and 6 respectively). If CPUID.01H:ECX[5] = 1 && CPUID.01H:ECX[6] = 1.

Definition at line 256 of file ArchitecturalMsr.h.

◆ EnableVmxOutsideSmx

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::EnableVmxOutsideSmx |

[Bit 2] Enable VMX outside SMX operation (R/WL): This bit enables VMX for system executive that do not require SMX. BIOS must set this bit only when the CPUID function 1 returns VMX feature flag set (ECX bit 5). If CPUID.01H:ECX[5] = 1.

Definition at line 263 of file ArchitecturalMsr.h.

◆ LmceOn

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::LmceOn |

[Bit 20] LMCE On (R/WL): When set, system software can program the MSRs associated with LMCE to configure delivery of some machine check exceptions to a single logical processor. If IA32_MCG_CAP[27] = 1.

Definition at line 296 of file ArchitecturalMsr.h.

◆ Lock

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::Lock |

[Bit 0] Lock bit (R/WO): (1 = locked). When set, locks this MSR from being written, writes to this bit will result in GP(0). Note: Once the Lock bit is set, the contents of this register cannot be modified. Therefore the lock bit must be set after configuring support for Intel Virtualization Technology and prior to transferring control to an option ROM or the OS. Hence, once the Lock bit is set, the entire IA32_FEATURE_CONTROL contents are preserved across RESET when PWRGOOD is not deasserted. If any one enumeration condition for defined bit field position greater than bit 0 holds.

Definition at line 247 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::Reserved1 |

Definition at line 264 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::Reserved2 |

Definition at line 278 of file ArchitecturalMsr.h.

◆ Reserved3

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::Reserved3 |

Definition at line 290 of file ArchitecturalMsr.h.

◆ Reserved4

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::Reserved4 |

Definition at line 297 of file ArchitecturalMsr.h.

◆ Reserved5

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::Reserved5 |

Definition at line 298 of file ArchitecturalMsr.h.

◆ SenterGlobalEnable

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::SenterGlobalEnable |

[Bit 15] SENTER Global Enable (R/WL): This bit must be set to enable SENTER leaf functions. This bit is supported only if CPUID.1:ECX.[bit 6] is set. If CPUID.01H:ECX[6] = 1.

Definition at line 277 of file ArchitecturalMsr.h.

◆ SenterLocalFunctionEnables

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::SenterLocalFunctionEnables |

[Bits 14:8] SENTER Local Function Enables (R/WL): When set, each bit in the field represents an enable control for a corresponding SENTER function. This bit is supported only if CPUID.1:ECX.[bit 6] is set. If CPUID.01H:ECX[6] = 1.

Definition at line 271 of file ArchitecturalMsr.h.

◆ SgxEnable

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::SgxEnable |

[Bit 18] SGX Global Enable (R/WL): This bit must be set to enable SGX leaf functions. If CPUID.(EAX=07H, ECX=0H): EBX[2] = 1.

Definition at line 289 of file ArchitecturalMsr.h.

◆ SgxLaunchControlEnable

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::SgxLaunchControlEnable |

[Bit 17] SGX Launch Control Enable (R/WL): This bit must be set to enable runtime reconfiguration of SGX Launch Control via IA32_SGXLEPUBKEYHASHn MSR. If CPUID.(EAX=07H, ECX=0H): ECX[30] = 1.

Definition at line 284 of file ArchitecturalMsr.h.

◆ Uint32

| UINT32 MSR_IA32_FEATURE_CONTROL_REGISTER::Uint32 |

All bit fields as a 32-bit value

Definition at line 303 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_FEATURE_CONTROL_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 307 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h