#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 VmcsRevisonId: 31 | |

| UINT32 MustBeZero: 1 | |

| UINT32 VmcsSize: 13 | |

| UINT32 Reserved1: 3 | |

| UINT32 VmcsAddressWidth: 1 | |

| UINT32 DualMonitor: 1 | |

| UINT32 MemoryType: 4 | |

| UINT32 InsOutsReporting: 1 | |

| UINT32 VmxControls: 1 | |

| UINT32 Reserved2: 8 | |

| } | Bits |

| UINT64 | Uint64 |

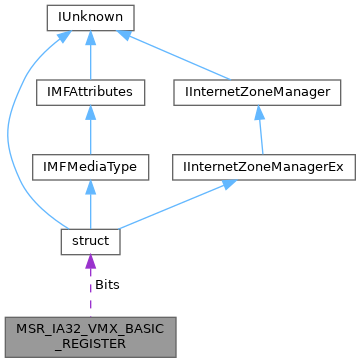

Detailed Description

MSR information returned for MSR index MSR_IA32_VMX_BASIC

Definition at line 3695 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } MSR_IA32_VMX_BASIC_REGISTER::Bits |

Individual bit fields

◆ DualMonitor

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::DualMonitor |

[Bit 49] If bit 49 is read as 1, the logical processor supports the dual-monitor treatment of system-management interrupts and system-management mode. See Section 34.15 for details of this treatment.

Definition at line 3737 of file ArchitecturalMsr.h.

◆ InsOutsReporting

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::InsOutsReporting |

[Bit 54] If bit 54 is read as 1, the processor reports information in the VM-exit instruction-information field on VM exitsdue to execution of the INS and OUTS instructions (see Section 27.2.4). This reporting is done only if this bit is read as 1.

Definition at line 3770 of file ArchitecturalMsr.h.

◆ MemoryType

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::MemoryType |

[Bit 53:50] report the memory type that should be used for the VMCS, for data structures referenced by pointers in the VMCS (I/O bitmaps, virtual-APIC page, MSR areas for VMX transitions), and for the MSEG header. If software needs to access these data structures (e.g., to modify the contents of the MSR bitmaps), it can configure the paging structures to map them into the linear-address space. If it does so, it should establish mappings that use the memory type reported bits 53:50 in this MSR.

As of this writing, all processors that support VMX operation indicate the write-back type.

If software needs to access these data structures (e.g., to modify the contents of the MSR bitmaps), it can configure the paging structures to map them into the linear-address space. If it does so, it should establish mappings that use the memory type reported in this MSR.

- Note

- Alternatively, software may map any of these regions or structures with the UC memory type. (This may be necessary for the MSEG header.) Doing so is discouraged unless necessary as it will cause the performance of software accesses to those structures to suffer.

Definition at line 3763 of file ArchitecturalMsr.h.

◆ MustBeZero

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::MustBeZero |

Definition at line 3711 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::Reserved1 |

Definition at line 3718 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::Reserved2 |

Definition at line 3780 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_VMX_BASIC_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 3785 of file ArchitecturalMsr.h.

◆ VmcsAddressWidth

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::VmcsAddressWidth |

[Bit 48] Indicates the width of the physical addresses that may be used for the VMXON region, each VMCS, and data structures referenced by pointers in a VMCS (I/O bitmaps, virtual-APIC page, MSR areas for VMX transitions). If the bit is 0, these addresses are limited to the processor's physical-address width. If the bit is 1, these addresses are limited to 32 bits. This bit is always 0 for processors that support Intel 64 architecture.

- Note

- On processors that support Intel 64 architecture, the pointer must not set bits beyond the processor's physical address width.

Definition at line 3731 of file ArchitecturalMsr.h.

◆ VmcsRevisonId

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::VmcsRevisonId |

[Bits 30:0] VMCS revision identifier used by the processor. Processors that use the same VMCS revision identifier use the same size for VMCS regions (see subsequent item on bits 44:32).

- Note

- Earlier versions of this manual specified that the VMCS revision identifier was a 32-bit field in bits 31:0 of this MSR. For all processors produced prior to this change, bit 31 of this MSR was read as 0.

Definition at line 3710 of file ArchitecturalMsr.h.

◆ VmcsSize

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::VmcsSize |

[Bit 44:32] Reports the number of bytes that software should allocate for the VMXON region and any VMCS region. It is a value greater than 0 and at most 4096(bit 44 is set if and only if bits 43:32 are clear).

Definition at line 3717 of file ArchitecturalMsr.h.

◆ VmxControls

| UINT32 MSR_IA32_VMX_BASIC_REGISTER::VmxControls |

[Bit 55] Bit 55 is read as 1 if any VMX controls that default to 1 may be cleared to 0. See Appendix A.2 for details. It also reports support for the VMX capability MSRs IA32_VMX_TRUE_PINBASED_CTLS, IA32_VMX_TRUE_PROCBASED_CTLS, IA32_VMX_TRUE_EXIT_CTLS, and IA32_VMX_TRUE_ENTRY_CTLS. See Appendix A.3.1, Appendix A.3.2, Appendix A.4, and Appendix A.5 for details.

Definition at line 3779 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h