#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 Ovf_PMC0: 1 | |

| UINT32 Ovf_PMC1: 1 | |

| UINT32 Ovf_PMC2: 1 | |

| UINT32 Ovf_PMC3: 1 | |

| UINT32 Reserved1: 28 | |

| UINT32 Ovf_FixedCtr0: 1 | |

| UINT32 Ovf_FixedCtr1: 1 | |

| UINT32 Ovf_FixedCtr2: 1 | |

| UINT32 Reserved2: 20 | |

| UINT32 Trace_ToPA_PMI: 1 | |

| UINT32 Reserved3: 2 | |

| UINT32 LBR_Frz: 1 | |

| UINT32 CTR_Frz: 1 | |

| UINT32 ASCI: 1 | |

| UINT32 Ovf_Uncore: 1 | |

| UINT32 OvfBuf: 1 | |

| UINT32 CondChgd: 1 | |

| } | Bits |

| UINT64 | Uint64 |

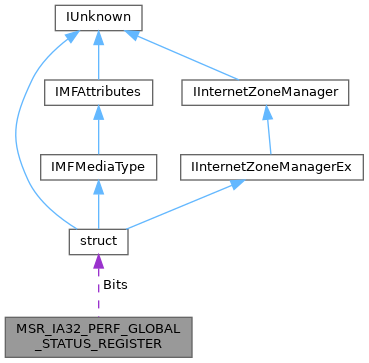

Detailed Description

MSR information returned for MSR index MSR_IA32_PERF_GLOBAL_STATUS

Definition at line 2906 of file ArchitecturalMsr.h.

Member Data Documentation

◆ ASCI

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::ASCI |

[Bit 60] ASCI: Data in the performance counters in the core PMU may include contributions from the direct or indirect operation intel SGX to protect an enclave. If CPUID.(EAX=07H, ECX=0):EBX[2] = 1.

Definition at line 2972 of file ArchitecturalMsr.h.

◆

| struct { ... } MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Bits |

Individual bit fields

◆ CondChgd

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::CondChgd |

[Bit 63] CondChgd: status bits of this register has changed. If CPUID.0AH: EAX[7:0] > 0.

Definition at line 2987 of file ArchitecturalMsr.h.

◆ CTR_Frz

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::CTR_Frz |

[Bit 59] CTR_Frz: Performance counters in the core PMU are frozen due to - IA32_DEBUGCTL.FREEZE_PERFMON_ON_ PMI=1, - one or more core PMU counters overflowed. If CPUID.0AH: EAX[7:0] > 3.

Definition at line 2966 of file ArchitecturalMsr.h.

◆ LBR_Frz

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::LBR_Frz |

[Bit 58] LBR_Frz: LBRs are frozen due to - IA32_DEBUGCTL.FREEZE_LBR_ON_PMI=1, - The LBR stack overflowed. If CPUID.0AH: EAX[7:0] > 3.

Definition at line 2960 of file ArchitecturalMsr.h.

◆ Ovf_FixedCtr0

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Ovf_FixedCtr0 |

[Bit 32] Ovf_FixedCtr0: Overflow status of IA32_FIXED_CTR0. If CPUID.0AH: EAX[7:0] > 1.

Definition at line 2936 of file ArchitecturalMsr.h.

◆ Ovf_FixedCtr1

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Ovf_FixedCtr1 |

[Bit 33] Ovf_FixedCtr1: Overflow status of IA32_FIXED_CTR1. If CPUID.0AH: EAX[7:0] > 1.

Definition at line 2941 of file ArchitecturalMsr.h.

◆ Ovf_FixedCtr2

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Ovf_FixedCtr2 |

[Bit 34] Ovf_FixedCtr2: Overflow status of IA32_FIXED_CTR2. If CPUID.0AH: EAX[7:0] > 1.

Definition at line 2946 of file ArchitecturalMsr.h.

◆ Ovf_PMC0

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Ovf_PMC0 |

[Bit 0] Ovf_PMC0: Overflow status of IA32_PMC0. If CPUID.0AH: EAX[15:8] > 0.

Definition at line 2915 of file ArchitecturalMsr.h.

◆ Ovf_PMC1

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Ovf_PMC1 |

[Bit 1] Ovf_PMC1: Overflow status of IA32_PMC1. If CPUID.0AH: EAX[15:8] > 1.

Definition at line 2920 of file ArchitecturalMsr.h.

◆ Ovf_PMC2

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Ovf_PMC2 |

[Bit 2] Ovf_PMC2: Overflow status of IA32_PMC2. If CPUID.0AH: EAX[15:8] > 2.

Definition at line 2925 of file ArchitecturalMsr.h.

◆ Ovf_PMC3

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Ovf_PMC3 |

[Bit 3] Ovf_PMC3: Overflow status of IA32_PMC3. If CPUID.0AH: EAX[15:8] > 3.

Definition at line 2930 of file ArchitecturalMsr.h.

◆ Ovf_Uncore

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Ovf_Uncore |

[Bit 61] Ovf_Uncore: Uncore counter overflow status. If CPUID.0AH: EAX[7:0] > 2.

Definition at line 2977 of file ArchitecturalMsr.h.

◆ OvfBuf

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::OvfBuf |

[Bit 62] OvfBuf: DS SAVE area Buffer overflow status. If CPUID.0AH: EAX[7:0] > 0.

Definition at line 2982 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Reserved1 |

Definition at line 2931 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Reserved2 |

Definition at line 2947 of file ArchitecturalMsr.h.

◆ Reserved3

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Reserved3 |

Definition at line 2954 of file ArchitecturalMsr.h.

◆ Trace_ToPA_PMI

| UINT32 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Trace_ToPA_PMI |

[Bit 55] Trace_ToPA_PMI: A PMI occurred due to a ToPA entry memory buffer was completely filled. If (CPUID.(EAX=07H, ECX=0):EBX[25] = 1) && IA32_RTIT_CTL.ToPA = 1.

Definition at line 2953 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_PERF_GLOBAL_STATUS_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 2992 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h