#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 EN0_OS: 1 | |

| UINT32 EN0_Usr: 1 | |

| UINT32 AnyThread0: 1 | |

| UINT32 EN0_PMI: 1 | |

| UINT32 EN1_OS: 1 | |

| UINT32 EN1_Usr: 1 | |

| UINT32 AnyThread1: 1 | |

| UINT32 EN1_PMI: 1 | |

| UINT32 EN2_OS: 1 | |

| UINT32 EN2_Usr: 1 | |

| UINT32 AnyThread2: 1 | |

| UINT32 EN2_PMI: 1 | |

| UINT32 Reserved1: 20 | |

| UINT32 Reserved2: 32 | |

| } | Bits |

| UINT32 | Uint32 |

| UINT64 | Uint64 |

Detailed Description

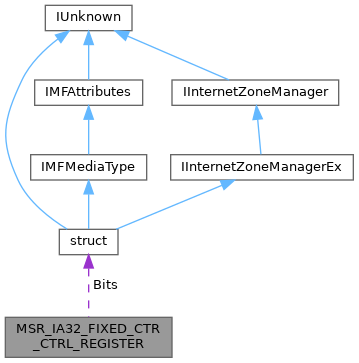

MSR information returned for MSR index MSR_IA32_FIXED_CTR_CTRL

Definition at line 2806 of file ArchitecturalMsr.h.

Member Data Documentation

◆ AnyThread0

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::AnyThread0 |

[Bit 2] AnyThread: When set to 1, it enables counting the associated event conditions occurring across all logical processors sharing a processor core. When set to 0, the counter only increments the associated event conditions occurring in the logical processor which programmed the MSR. If CPUID.0AH: EAX[7:0] > 2.

Definition at line 2826 of file ArchitecturalMsr.h.

◆ AnyThread1

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::AnyThread1 |

[Bit 6] AnyThread: When set to 1, it enables counting the associated event conditions occurring across all logical processors sharing a processor core. When set to 0, the counter only increments the associated event conditions occurring in the logical processor which programmed the MSR. If CPUID.0AH: EAX[7:0] > 2.

Definition at line 2846 of file ArchitecturalMsr.h.

◆ AnyThread2

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::AnyThread2 |

[Bit 10] AnyThread: When set to 1, it enables counting the associated event conditions occurring across all logical processors sharing a processor core. When set to 0, the counter only increments the associated event conditions occurring in the logical processor which programmed the MSR. If CPUID.0AH: EAX[7:0] > 2.

Definition at line 2866 of file ArchitecturalMsr.h.

◆

| struct { ... } MSR_IA32_FIXED_CTR_CTRL_REGISTER::Bits |

Individual bit fields

◆ EN0_OS

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::EN0_OS |

[Bit 0] EN0_OS: Enable Fixed Counter 0 to count while CPL = 0.

Definition at line 2814 of file ArchitecturalMsr.h.

◆ EN0_PMI

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::EN0_PMI |

[Bit 3] EN0_PMI: Enable PMI when fixed counter 0 overflows.

Definition at line 2830 of file ArchitecturalMsr.h.

◆ EN0_Usr

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::EN0_Usr |

[Bit 1] EN0_Usr: Enable Fixed Counter 0 to count while CPL > 0.

Definition at line 2818 of file ArchitecturalMsr.h.

◆ EN1_OS

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::EN1_OS |

[Bit 4] EN1_OS: Enable Fixed Counter 1 to count while CPL = 0.

Definition at line 2834 of file ArchitecturalMsr.h.

◆ EN1_PMI

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::EN1_PMI |

[Bit 7] EN1_PMI: Enable PMI when fixed counter 1 overflows.

Definition at line 2850 of file ArchitecturalMsr.h.

◆ EN1_Usr

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::EN1_Usr |

[Bit 5] EN1_Usr: Enable Fixed Counter 1 to count while CPL > 0.

Definition at line 2838 of file ArchitecturalMsr.h.

◆ EN2_OS

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::EN2_OS |

[Bit 8] EN2_OS: Enable Fixed Counter 2 to count while CPL = 0.

Definition at line 2854 of file ArchitecturalMsr.h.

◆ EN2_PMI

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::EN2_PMI |

[Bit 11] EN2_PMI: Enable PMI when fixed counter 2 overflows.

Definition at line 2870 of file ArchitecturalMsr.h.

◆ EN2_Usr

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::EN2_Usr |

[Bit 9] EN2_Usr: Enable Fixed Counter 2 to count while CPL > 0.

Definition at line 2858 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::Reserved1 |

Definition at line 2871 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::Reserved2 |

Definition at line 2872 of file ArchitecturalMsr.h.

◆ Uint32

| UINT32 MSR_IA32_FIXED_CTR_CTRL_REGISTER::Uint32 |

All bit fields as a 32-bit value

Definition at line 2877 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_FIXED_CTR_CTRL_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 2881 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h