#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 Reserved1: 11 | |

| UINT32 V: 1 | |

| UINT32 PhysMask: 20 | |

| UINT32 PhysMaskHi: 32 | |

| } | Bits |

| UINT64 | Uint64 |

Detailed Description

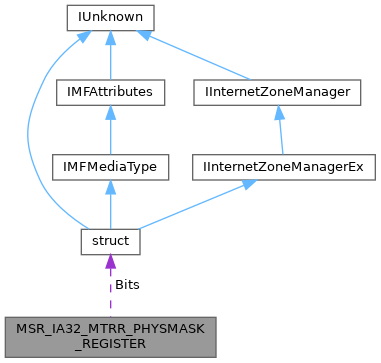

MSR information returned for MSR indexes MSR_IA32_MTRR_PHYSMASK0 to MSR_IA32_MTRR_PHYSMASK9

Definition at line 2185 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } MSR_IA32_MTRR_PHYSMASK_REGISTER::Bits |

Individual bit fields

◆ PhysMask

| UINT32 MSR_IA32_MTRR_PHYSMASK_REGISTER::PhysMask |

[Bits 31:12] PhysMask. MTRR address range mask.

Definition at line 2198 of file ArchitecturalMsr.h.

◆ PhysMaskHi

| UINT32 MSR_IA32_MTRR_PHYSMASK_REGISTER::PhysMaskHi |

[Bits MAXPHYSADDR:32] PhysMask. Upper bits of MTRR address range mask. MAXPHYADDR: The bit position indicated by MAXPHYADDR depends on the maximum physical address range supported by the processor. It is reported by CPUID leaf function 80000008H. If CPUID does not support leaf 80000008H, the processor supports 36-bit physical address size, then bit PhysMask consists of bits 35:12, and bits 63:36 are reserved.

Definition at line 2207 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_MTRR_PHYSMASK_REGISTER::Reserved1 |

Definition at line 2190 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_MTRR_PHYSMASK_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 2212 of file ArchitecturalMsr.h.

◆ V

| UINT32 MSR_IA32_MTRR_PHYSMASK_REGISTER::V |

[Bit 11] Valid Enable range mask.

Definition at line 2194 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h