#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 FastStrings: 1 | |

| UINT32 Reserved1: 2 | |

| UINT32 AutomaticThermalControlCircuit: 1 | |

| UINT32 Reserved2: 3 | |

| UINT32 PerformanceMonitoring: 1 | |

| UINT32 Reserved3: 3 | |

| UINT32 BTS: 1 | |

| UINT32 PEBS: 1 | |

| UINT32 Reserved4: 3 | |

| UINT32 EIST: 1 | |

| UINT32 Reserved5: 1 | |

| UINT32 MONITOR: 1 | |

| UINT32 Reserved6: 3 | |

| UINT32 LimitCpuidMaxval: 1 | |

| UINT32 xTPR_Message_Disable: 1 | |

| UINT32 Reserved7: 8 | |

| UINT32 Reserved8: 2 | |

| UINT32 XD: 1 | |

| UINT32 Reserved9: 29 | |

| } | Bits |

| UINT64 | Uint64 |

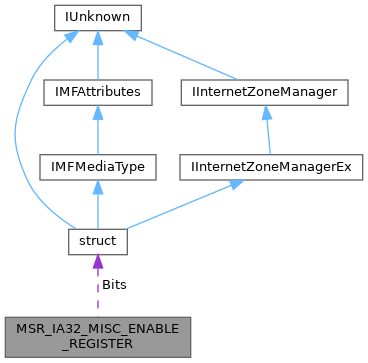

Detailed Description

MSR information returned for MSR index MSR_IA32_MISC_ENABLE

Definition at line 1416 of file ArchitecturalMsr.h.

Member Data Documentation

◆ AutomaticThermalControlCircuit

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::AutomaticThermalControlCircuit |

[Bit 3] Automatic Thermal Control Circuit Enable (R/W) 1 = Setting this bit enables the thermal control circuit (TCC) portion of the Intel Thermal Monitor feature. This allows the processor to automatically reduce power consumption in response to TCC activation. 0 = Disabled. Note: In some products clearing this bit might be ignored in critical thermal conditions, and TM1, TM2 and adaptive thermal throttling will still be activated. The default value of this field varies with product. See respective tables where default value is listed. Introduced at Display Family / Display Model 0F_0H.

Definition at line 1439 of file ArchitecturalMsr.h.

◆

| struct { ... } MSR_IA32_MISC_ENABLE_REGISTER::Bits |

Individual bit fields

◆ BTS

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::BTS |

[Bit 11] Branch Trace Storage Unavailable (RO) 1 = Processor doesn't support branch trace storage (BTS) 0 = BTS is supported. Introduced at Display Family / Display Model 0F_0H.

Definition at line 1453 of file ArchitecturalMsr.h.

◆ EIST

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::EIST |

[Bit 16] Enhanced Intel SpeedStep Technology Enable (R/W) 0= Enhanced Intel SpeedStep Technology disabled 1 = Enhanced Intel SpeedStep Technology enabled. If CPUID.01H: ECX[7] =1.

Definition at line 1466 of file ArchitecturalMsr.h.

◆ FastStrings

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::FastStrings |

[Bit 0] Fast-Strings Enable When set, the fast-strings feature (for REP MOVS and REP STORS) is enabled (default); when clear, fast-strings are disabled. Introduced at Display Family / Display Model 0F_0H.

Definition at line 1426 of file ArchitecturalMsr.h.

◆ LimitCpuidMaxval

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::LimitCpuidMaxval |

[Bit 22] Limit CPUID Maxval (R/W) When this bit is set to 1, CPUID.00H returns a maximum value in EAX[7:0] of 2. BIOS should contain a setup question that allows users to specify when the installed OS does not support CPUID functions greater than 2. Before setting this bit, BIOS must execute the CPUID.0H and examine the maximum value returned in EAX[7:0]. If the maximum value is greater than 2, this bit is supported. Otherwise, this bit is not supported. Setting this bit when the maximum value is not greater than 2 may generate a #GP exception. Setting this bit may cause unexpected behavior in software that depends on the availability of CPUID leaves greater than 2. Introduced at Display Family / Display Model 0F_03H.

Definition at line 1495 of file ArchitecturalMsr.h.

◆ MONITOR

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::MONITOR |

[Bit 18] ENABLE MONITOR FSM (R/W) When this bit is set to 0, the MONITOR feature flag is not set (CPUID.01H:ECX[bit 3] = 0). This indicates that MONITOR/MWAIT are not supported. Software attempts to execute MONITOR/MWAIT will cause #UD when this bit is 0. When this bit is set to 1 (default), MONITOR/MWAIT are supported (CPUID.01H:ECX[bit 3] = 1). If the SSE3 feature flag ECX[0] is not set (CPUID.01H:ECX[bit 0] = 0), the OS must not attempt to alter this bit. BIOS must leave it in the default state. Writing this bit when the SSE3 feature flag is set to 0 may generate a #GP exception. Introduced at Display Family / Display Model 0F_03H.

Definition at line 1480 of file ArchitecturalMsr.h.

◆ PEBS

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::PEBS |

[Bit 12] Processor Event Based Sampling (PEBS) Unavailable (RO) 1 = PEBS is not supported; 0 = PEBS is supported. Introduced at Display Family / Display Model 06_0FH.

Definition at line 1459 of file ArchitecturalMsr.h.

◆ PerformanceMonitoring

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::PerformanceMonitoring |

[Bit 7] Performance Monitoring Available (R) 1 = Performance monitoring enabled 0 = Performance monitoring disabled. Introduced at Display Family / Display Model 0F_0H.

Definition at line 1446 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::Reserved1 |

Definition at line 1427 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::Reserved2 |

Definition at line 1440 of file ArchitecturalMsr.h.

◆ Reserved3

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::Reserved3 |

Definition at line 1447 of file ArchitecturalMsr.h.

◆ Reserved4

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::Reserved4 |

Definition at line 1460 of file ArchitecturalMsr.h.

◆ Reserved5

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::Reserved5 |

Definition at line 1467 of file ArchitecturalMsr.h.

◆ Reserved6

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::Reserved6 |

Definition at line 1481 of file ArchitecturalMsr.h.

◆ Reserved7

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::Reserved7 |

Definition at line 1502 of file ArchitecturalMsr.h.

◆ Reserved8

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::Reserved8 |

Definition at line 1503 of file ArchitecturalMsr.h.

◆ Reserved9

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::Reserved9 |

Definition at line 1515 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_MISC_ENABLE_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 1520 of file ArchitecturalMsr.h.

◆ XD

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::XD |

[Bit 34] XD Bit Disable (R/W) When set to 1, the Execute Disable Bit feature (XD Bit) is disabled and the XD Bit extended feature flag will be clear (CPUID.80000001H: EDX[20]=0). When set to a 0 (default), the Execute Disable Bit feature (if available) allows the OS to enable PAE paging and take advantage of data only pages. BIOS must not alter the contents of this bit location, if XD bit is not supported. Writing this bit to 1 when the XD Bit extended feature flag is set to 0 may generate a #GP exception. if CPUID.80000001H:EDX[2 0] = 1.

Definition at line 1514 of file ArchitecturalMsr.h.

◆ xTPR_Message_Disable

| UINT32 MSR_IA32_MISC_ENABLE_REGISTER::xTPR_Message_Disable |

[Bit 23] xTPR Message Disable (R/W) When set to 1, xTPR messages are disabled. xTPR messages are optional messages that allow the processor to inform the chipset of its priority. if CPUID.01H:ECX[14] = 1.

Definition at line 1501 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h