#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 DCA_ACTIVE: 1 | |

| UINT32 TRANSACTION: 2 | |

| UINT32 DCA_TYPE: 4 | |

| UINT32 DCA_QUEUE_SIZE: 4 | |

| UINT32 Reserved1: 2 | |

| UINT32 DCA_DELAY: 4 | |

| UINT32 Reserved2: 7 | |

| UINT32 SW_BLOCK: 1 | |

| UINT32 Reserved3: 1 | |

| UINT32 HW_BLOCK: 1 | |

| UINT32 Reserved4: 5 | |

| UINT32 Reserved5: 32 | |

| } | Bits |

| UINT32 | Uint32 |

| UINT64 | Uint64 |

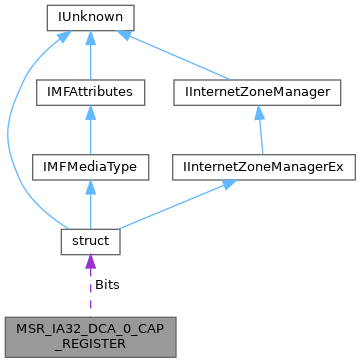

Detailed Description

MSR information returned for MSR index MSR_IA32_DCA_0_CAP

Definition at line 2014 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } MSR_IA32_DCA_0_CAP_REGISTER::Bits |

Individual bit fields

◆ DCA_ACTIVE

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::DCA_ACTIVE |

[Bit 0] DCA_ACTIVE: Set by HW when DCA is fuseenabled and no defeatures are set.

Definition at line 2023 of file ArchitecturalMsr.h.

◆ DCA_DELAY

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::DCA_DELAY |

[Bits 16:13] DCA_DELAY: Writes will update the register but have no HW side-effect.

Definition at line 2041 of file ArchitecturalMsr.h.

◆ DCA_QUEUE_SIZE

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::DCA_QUEUE_SIZE |

[Bits 10:7] DCA_QUEUE_SIZE.

Definition at line 2035 of file ArchitecturalMsr.h.

◆ DCA_TYPE

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::DCA_TYPE |

[Bits 6:3] DCA_TYPE.

Definition at line 2031 of file ArchitecturalMsr.h.

◆ HW_BLOCK

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::HW_BLOCK |

[Bit 26] HW_BLOCK: Set when DCA is blocked by HW (e.g. CR0.CD = 1).

Definition at line 2051 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::Reserved1 |

Definition at line 2036 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::Reserved2 |

Definition at line 2042 of file ArchitecturalMsr.h.

◆ Reserved3

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::Reserved3 |

Definition at line 2047 of file ArchitecturalMsr.h.

◆ Reserved4

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::Reserved4 |

Definition at line 2052 of file ArchitecturalMsr.h.

◆ Reserved5

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::Reserved5 |

Definition at line 2053 of file ArchitecturalMsr.h.

◆ SW_BLOCK

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::SW_BLOCK |

[Bit 24] SW_BLOCK: SW can request DCA block by setting this bit.

Definition at line 2046 of file ArchitecturalMsr.h.

◆ TRANSACTION

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::TRANSACTION |

[Bits 2:1] TRANSACTION.

Definition at line 2027 of file ArchitecturalMsr.h.

◆ Uint32

| UINT32 MSR_IA32_DCA_0_CAP_REGISTER::Uint32 |

All bit fields as a 32-bit value

Definition at line 2058 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_DCA_0_CAP_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 2062 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h