#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 LBR: 1 | |

| UINT32 BTF: 1 | |

| UINT32 Reserved1: 4 | |

| UINT32 TR: 1 | |

| UINT32 BTS: 1 | |

| UINT32 BTINT: 1 | |

| UINT32 BTS_OFF_OS: 1 | |

| UINT32 BTS_OFF_USR: 1 | |

| UINT32 FREEZE_LBRS_ON_PMI: 1 | |

| UINT32 FREEZE_PERFMON_ON_PMI: 1 | |

| UINT32 ENABLE_UNCORE_PMI: 1 | |

| UINT32 FREEZE_WHILE_SMM: 1 | |

| UINT32 RTM_DEBUG: 1 | |

| UINT32 Reserved2: 16 | |

| UINT32 Reserved3: 32 | |

| } | Bits |

| UINT32 | Uint32 |

| UINT64 | Uint64 |

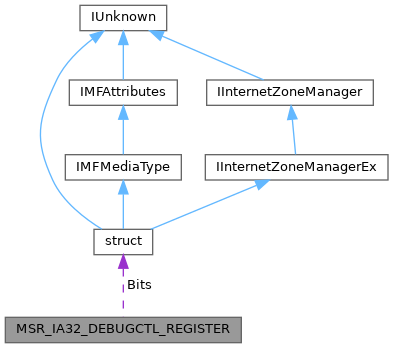

Detailed Description

MSR information returned for MSR index MSR_IA32_DEBUGCTL

Definition at line 1770 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } MSR_IA32_DEBUGCTL_REGISTER::Bits |

Individual bit fields

◆ BTF

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::BTF |

[Bit 1] BTF: Setting this bit to 1 enables the processor to treat EFLAGS.TF as single-step on branches instead of single-step on instructions. Introduced at Display Family / Display Model 06_01H.

Definition at line 1786 of file ArchitecturalMsr.h.

◆ BTINT

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::BTINT |

[Bit 8] BTINT: When clear, BTMs are logged in a BTS buffer in circular fashion. When this bit is set, an interrupt is generated by the BTS facility when the BTS buffer is full. Introduced at Display Family / Display Model 06_0EH.

Definition at line 1805 of file ArchitecturalMsr.h.

◆ BTS

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::BTS |

[Bit 7] BTS: Setting this bit enables branch trace messages (BTMs) to be logged in a BTS buffer. Introduced at Display Family / Display Model 06_0EH.

Definition at line 1798 of file ArchitecturalMsr.h.

◆ BTS_OFF_OS

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::BTS_OFF_OS |

[Bit 9] BTS_OFF_OS: When set, BTS or BTM is skipped if CPL = 0. Introduced at Display Family / Display Model 06_0FH.

Definition at line 1810 of file ArchitecturalMsr.h.

◆ BTS_OFF_USR

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::BTS_OFF_USR |

[Bit 10] BTS_OFF_USR: When set, BTS or BTM is skipped if CPL > 0. Introduced at Display Family / Display Model 06_0FH.

Definition at line 1815 of file ArchitecturalMsr.h.

◆ ENABLE_UNCORE_PMI

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::ENABLE_UNCORE_PMI |

[Bit 13] ENABLE_UNCORE_PMI: When set, enables the logical processor to receive and generate PMI on behalf of the uncore. Introduced at Display Family / Display Model 06_1AH.

Definition at line 1832 of file ArchitecturalMsr.h.

◆ FREEZE_LBRS_ON_PMI

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::FREEZE_LBRS_ON_PMI |

[Bit 11] FREEZE_LBRS_ON_PMI: When set, the LBR stack is frozen on a PMI request. If CPUID.01H: ECX[15] = 1 && CPUID.0AH: EAX[7:0] > 1.

Definition at line 1820 of file ArchitecturalMsr.h.

◆ FREEZE_PERFMON_ON_PMI

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::FREEZE_PERFMON_ON_PMI |

[Bit 12] FREEZE_PERFMON_ON_PMI: When set, each ENABLE bit of the global counter control MSR are frozen (address 38FH) on a PMI request. If CPUID.01H: ECX[15] = 1 && CPUID.0AH: EAX[7:0] > 1.

Definition at line 1826 of file ArchitecturalMsr.h.

◆ FREEZE_WHILE_SMM

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::FREEZE_WHILE_SMM |

[Bit 14] FREEZE_WHILE_SMM: When set, freezes perfmon and trace messages while in SMM. If IA32_PERF_CAPABILITIES[ 12] = 1.

Definition at line 1837 of file ArchitecturalMsr.h.

◆ LBR

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::LBR |

[Bit 0] LBR: Setting this bit to 1 enables the processor to record a running trace of the most recent branches taken by the processor in the LBR stack. Introduced at Display Family / Display Model 06_01H.

Definition at line 1780 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::Reserved1 |

Definition at line 1787 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::Reserved2 |

Definition at line 1843 of file ArchitecturalMsr.h.

◆ Reserved3

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::Reserved3 |

Definition at line 1844 of file ArchitecturalMsr.h.

◆ RTM_DEBUG

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::RTM_DEBUG |

[Bit 15] RTM_DEBUG: When set, enables DR7 debug bit on XBEGIN. If (CPUID.(EAX=07H, ECX=0):EBX[11] = 1).

Definition at line 1842 of file ArchitecturalMsr.h.

◆ TR

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::TR |

[Bit 6] TR: Setting this bit to 1 enables branch trace messages to be sent. Introduced at Display Family / Display Model 06_0EH.

Definition at line 1792 of file ArchitecturalMsr.h.

◆ Uint32

| UINT32 MSR_IA32_DEBUGCTL_REGISTER::Uint32 |

All bit fields as a 32-bit value

Definition at line 1849 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_DEBUGCTL_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 1853 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h