MSR_IA32_PERF_CTL_REGISTER Union Reference

#include <ArchitecturalMsr.h>

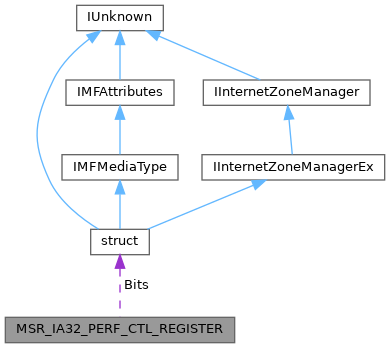

Collaboration diagram for MSR_IA32_PERF_CTL_REGISTER:

Public Attributes | |

| struct { | |

| UINT32 TargetState: 16 | |

| UINT32 Reserved1: 16 | |

| UINT32 IDA: 1 | |

| UINT32 Reserved2: 31 | |

| } | Bits |

| UINT64 | Uint64 |

Detailed Description

MSR information returned for MSR index MSR_IA32_PERF_CTL

Definition at line 1106 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } MSR_IA32_PERF_CTL_REGISTER::Bits |

Individual bit fields

◆ IDA

| UINT32 MSR_IA32_PERF_CTL_REGISTER::IDA |

[Bit 32] IDA Engage. (R/W) When set to 1: disengages IDA. 06_0FH (Mobile only).

Definition at line 1120 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_PERF_CTL_REGISTER::Reserved1 |

Definition at line 1115 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_PERF_CTL_REGISTER::Reserved2 |

Definition at line 1121 of file ArchitecturalMsr.h.

◆ TargetState

| UINT32 MSR_IA32_PERF_CTL_REGISTER::TargetState |

[Bits 15:0] Target performance State Value.

Definition at line 1114 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_PERF_CTL_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 1126 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h