#include <ArchitecturalMsr.h>

Public Attributes | |

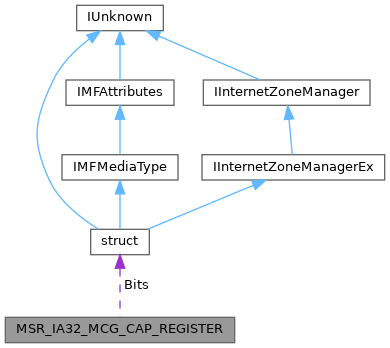

| struct { | |

| UINT32 Count: 8 | |

| UINT32 MCG_CTL_P: 1 | |

| UINT32 MCG_EXT_P: 1 | |

| UINT32 MCP_CMCI_P: 1 | |

| UINT32 MCG_TES_P: 1 | |

| UINT32 Reserved1: 4 | |

| UINT32 MCG_EXT_CNT: 8 | |

| UINT32 MCG_SER_P: 1 | |

| UINT32 Reserved2: 1 | |

| UINT32 MCG_ELOG_P: 1 | |

| UINT32 MCG_LMCE_P: 1 | |

| UINT32 Reserved3: 4 | |

| UINT32 Reserved4: 32 | |

| } | Bits |

| UINT32 | Uint32 |

| UINT64 | Uint64 |

Detailed Description

MSR information returned for MSR index MSR_IA32_MCG_CAP

Definition at line 789 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } MSR_IA32_MCG_CAP_REGISTER::Bits |

Individual bit fields

◆ Count

| UINT32 MSR_IA32_MCG_CAP_REGISTER::Count |

[Bits 7:0] Count: Number of reporting banks.

Definition at line 797 of file ArchitecturalMsr.h.

◆ MCG_CTL_P

| UINT32 MSR_IA32_MCG_CAP_REGISTER::MCG_CTL_P |

[Bit 8] MCG_CTL_P: IA32_MCG_CTL is present if this bit is set.

Definition at line 801 of file ArchitecturalMsr.h.

◆ MCG_ELOG_P

| UINT32 MSR_IA32_MCG_CAP_REGISTER::MCG_ELOG_P |

[Bit 26] MCG_ELOG_P: Indicates that the processor allows platform firmware to be invoked when an error is detected so that it may provide additional platform specific information in an ACPI format "Generic Error Data Entry" that augments the data included in machine check bank registers. Introduced at Display Family / Display Model 06_3EH.

Definition at line 837 of file ArchitecturalMsr.h.

◆ MCG_EXT_CNT

| UINT32 MSR_IA32_MCG_CAP_REGISTER::MCG_EXT_CNT |

[Bits 23:16] MCG_EXT_CNT: Number of extended machine check state registers present.

Definition at line 822 of file ArchitecturalMsr.h.

◆ MCG_EXT_P

| UINT32 MSR_IA32_MCG_CAP_REGISTER::MCG_EXT_P |

[Bit 9] MCG_EXT_P: Extended machine check state registers are present if this bit is set.

Definition at line 806 of file ArchitecturalMsr.h.

◆ MCG_LMCE_P

| UINT32 MSR_IA32_MCG_CAP_REGISTER::MCG_LMCE_P |

[Bit 27] MCG_LMCE_P: Indicates that the processor support extended state in IA32_MCG_STATUS and associated MSR necessary to configure Local Machine Check Exception (LMCE). Introduced at Display Family / Display Model 06_3EH.

Definition at line 844 of file ArchitecturalMsr.h.

◆ MCG_SER_P

| UINT32 MSR_IA32_MCG_CAP_REGISTER::MCG_SER_P |

[Bit 24] MCG_SER_P: The processor supports software error recovery if this bit is set.

Definition at line 827 of file ArchitecturalMsr.h.

◆ MCG_TES_P

| UINT32 MSR_IA32_MCG_CAP_REGISTER::MCG_TES_P |

[Bit 11] MCG_TES_P: Threshold-based error status register are present if this bit is set.

Definition at line 816 of file ArchitecturalMsr.h.

◆ MCP_CMCI_P

| UINT32 MSR_IA32_MCG_CAP_REGISTER::MCP_CMCI_P |

[Bit 10] MCP_CMCI_P: Support for corrected MC error event is present. Introduced at Display Family / Display Model 06_01H.

Definition at line 811 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_MCG_CAP_REGISTER::Reserved1 |

Definition at line 817 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_MCG_CAP_REGISTER::Reserved2 |

Definition at line 828 of file ArchitecturalMsr.h.

◆ Reserved3

| UINT32 MSR_IA32_MCG_CAP_REGISTER::Reserved3 |

Definition at line 845 of file ArchitecturalMsr.h.

◆ Reserved4

| UINT32 MSR_IA32_MCG_CAP_REGISTER::Reserved4 |

Definition at line 846 of file ArchitecturalMsr.h.

◆ Uint32

| UINT32 MSR_IA32_MCG_CAP_REGISTER::Uint32 |

All bit fields as a 32-bit value

Definition at line 851 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_MCG_CAP_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 855 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h