#include <ArchitecturalMsr.h>

Public Attributes | |

| struct { | |

| UINT32 LBR_FMT: 6 | |

| UINT32 PEBS_TRAP: 1 | |

| UINT32 PEBS_ARCH_REG: 1 | |

| UINT32 PEBS_REC_FMT: 4 | |

| UINT32 SMM_FREEZE: 1 | |

| UINT32 FW_WRITE: 1 | |

| UINT32 Reserved1: 18 | |

| UINT32 Reserved2: 32 | |

| } | Bits |

| UINT32 | Uint32 |

| UINT64 | Uint64 |

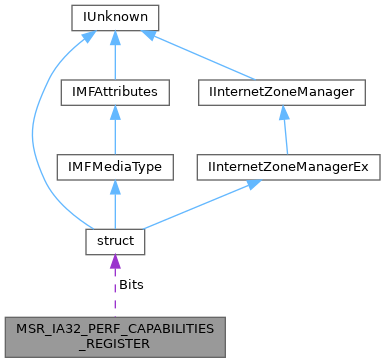

Detailed Description

MSR information returned for MSR index MSR_IA32_PERF_CAPABILITIES

Definition at line 2738 of file ArchitecturalMsr.h.

Member Data Documentation

◆

| struct { ... } MSR_IA32_PERF_CAPABILITIES_REGISTER::Bits |

Individual bit fields

◆ FW_WRITE

| UINT32 MSR_IA32_PERF_CAPABILITIES_REGISTER::FW_WRITE |

[Bit 13] 1: Full width of counter writable via IA32_A_PMCx.

Definition at line 2766 of file ArchitecturalMsr.h.

◆ LBR_FMT

| UINT32 MSR_IA32_PERF_CAPABILITIES_REGISTER::LBR_FMT |

[Bits 5:0] LBR format.

Definition at line 2746 of file ArchitecturalMsr.h.

◆ PEBS_ARCH_REG

| UINT32 MSR_IA32_PERF_CAPABILITIES_REGISTER::PEBS_ARCH_REG |

[Bit 7] PEBSSaveArchRegs.

Definition at line 2754 of file ArchitecturalMsr.h.

◆ PEBS_REC_FMT

| UINT32 MSR_IA32_PERF_CAPABILITIES_REGISTER::PEBS_REC_FMT |

[Bits 11:8] PEBS Record Format.

Definition at line 2758 of file ArchitecturalMsr.h.

◆ PEBS_TRAP

| UINT32 MSR_IA32_PERF_CAPABILITIES_REGISTER::PEBS_TRAP |

[Bit 6] PEBS Trap.

Definition at line 2750 of file ArchitecturalMsr.h.

◆ Reserved1

| UINT32 MSR_IA32_PERF_CAPABILITIES_REGISTER::Reserved1 |

Definition at line 2767 of file ArchitecturalMsr.h.

◆ Reserved2

| UINT32 MSR_IA32_PERF_CAPABILITIES_REGISTER::Reserved2 |

Definition at line 2768 of file ArchitecturalMsr.h.

◆ SMM_FREEZE

| UINT32 MSR_IA32_PERF_CAPABILITIES_REGISTER::SMM_FREEZE |

[Bit 12] 1: Freeze while SMM is supported.

Definition at line 2762 of file ArchitecturalMsr.h.

◆ Uint32

| UINT32 MSR_IA32_PERF_CAPABILITIES_REGISTER::Uint32 |

All bit fields as a 32-bit value

Definition at line 2773 of file ArchitecturalMsr.h.

◆ Uint64

| UINT64 MSR_IA32_PERF_CAPABILITIES_REGISTER::Uint64 |

All bit fields as a 64-bit value

Definition at line 2777 of file ArchitecturalMsr.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/ArchitecturalMsr.h