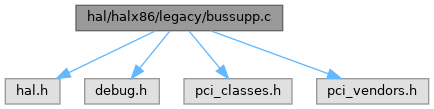

#include <hal.h>#include <debug.h>#include "pci_classes.h"#include "pci_vendors.h"

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

| #define | NEWLINE "\n" |

Variables | |

| KSPIN_LOCK | HalpPCIConfigLock |

| ULONG | HalpPciIrqMask |

| static BOOLEAN | WarningsGiven [5] |

Macro Definition Documentation

◆ NDEBUG

◆ NEWLINE

Function Documentation

◆ HalAdjustResourceList()

| NTSTATUS NTAPI HalAdjustResourceList | ( | IN PIO_RESOURCE_REQUIREMENTS_LIST * | ResourceList | ) |

Definition at line 1450 of file bussupp.c.

◆ HalAssignSlotResources()

| NTSTATUS NTAPI HalAssignSlotResources | ( | IN PUNICODE_STRING | RegistryPath, |

| IN PUNICODE_STRING | DriverClassName, | ||

| IN PDRIVER_OBJECT | DriverObject, | ||

| IN PDEVICE_OBJECT | DeviceObject, | ||

| IN INTERFACE_TYPE | BusType, | ||

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber, | ||

| IN OUT PCM_RESOURCE_LIST * | AllocatedResources | ||

| ) |

Definition at line 1477 of file bussupp.c.

◆ HalGetBusData()

| ULONG NTAPI HalGetBusData | ( | IN BUS_DATA_TYPE | BusDataType, |

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 1521 of file bussupp.c.

◆ HalGetBusDataByOffset()

| ULONG NTAPI HalGetBusDataByOffset | ( | IN BUS_DATA_TYPE | BusDataType, |

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Offset, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 1542 of file bussupp.c.

Referenced by HalGetBusData().

◆ HalGetInterruptVector()

| ULONG NTAPI HalGetInterruptVector | ( | IN INTERFACE_TYPE | InterfaceType, |

| IN ULONG | BusNumber, | ||

| IN ULONG | BusInterruptLevel, | ||

| IN ULONG | BusInterruptVector, | ||

| OUT PKIRQL | Irql, | ||

| OUT PKAFFINITY | Affinity | ||

| ) |

Definition at line 1575 of file bussupp.c.

◆ HaliFindBusAddressTranslation()

| BOOLEAN NTAPI HaliFindBusAddressTranslation | ( | IN PHYSICAL_ADDRESS | BusAddress, |

| IN OUT PULONG | AddressSpace, | ||

| OUT PPHYSICAL_ADDRESS | TranslatedAddress, | ||

| IN OUT PULONG_PTR | Context, | ||

| IN BOOLEAN | NextBus | ||

| ) |

Definition at line 1331 of file bussupp.c.

Referenced by HalpInitBusHandler().

◆ HaliTranslateBusAddress()

| BOOLEAN NTAPI HaliTranslateBusAddress | ( | IN INTERFACE_TYPE | InterfaceType, |

| IN ULONG | BusNumber, | ||

| IN PHYSICAL_ADDRESS | BusAddress, | ||

| IN OUT PULONG | AddressSpace, | ||

| OUT PPHYSICAL_ADDRESS | TranslatedAddress | ||

| ) |

Definition at line 1413 of file bussupp.c.

Referenced by HalpInitBusHandler(), and HalTranslateBusAddress().

◆ HalpAllocateAndInitPciBusHandler()

| PBUS_HANDLER NTAPI HalpAllocateAndInitPciBusHandler | ( | IN ULONG | PciType, |

| IN ULONG | BusNo, | ||

| IN BOOLEAN | TestAllocation | ||

| ) |

Definition at line 283 of file bussupp.c.

Referenced by HalpInitializePciBus().

◆ HalpAllocateBusHandler()

| PBUS_HANDLER NTAPI HalpAllocateBusHandler | ( | IN INTERFACE_TYPE | InterfaceType, |

| IN BUS_DATA_TYPE | BusDataType, | ||

| IN ULONG | BusNumber, | ||

| IN INTERFACE_TYPE | ParentBusInterfaceType, | ||

| IN ULONG | ParentBusNumber, | ||

| IN ULONG | BusSpecificData | ||

| ) |

Definition at line 110 of file bussupp.c.

Referenced by HalpAllocateAndInitPciBusHandler(), and HalpRegisterInternalBusHandlers().

◆ HalpAssignSlotResources()

| NTSTATUS NTAPI HalpAssignSlotResources | ( | IN PUNICODE_STRING | RegistryPath, |

| IN PUNICODE_STRING | DriverClassName, | ||

| IN PDRIVER_OBJECT | DriverObject, | ||

| IN PDEVICE_OBJECT | DeviceObject, | ||

| IN INTERFACE_TYPE | BusType, | ||

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber, | ||

| IN OUT PCM_RESOURCE_LIST * | AllocatedResources | ||

| ) |

Definition at line 1296 of file bussupp.c.

Referenced by HalAssignSlotResources().

◆ HalpDebugPciDumpBus()

| VOID NTAPI HalpDebugPciDumpBus | ( | IN PBUS_HANDLER | BusHandler, |

| IN PCI_SLOT_NUMBER | PciSlot, | ||

| IN ULONG | i, | ||

| IN ULONG | j, | ||

| IN ULONG | k, | ||

| IN PPCI_COMMON_CONFIG | PciData | ||

| ) |

Definition at line 794 of file bussupp.c.

Referenced by HalpInitializePciBus().

◆ HalpFixupPciSupportedRanges()

Definition at line 696 of file bussupp.c.

Referenced by HalpInitializePciBus().

◆ HalpGetChipHacks()

| NTSTATUS NTAPI HalpGetChipHacks | ( | IN USHORT | VendorId, |

| IN USHORT | DeviceId, | ||

| IN UCHAR | RevisionId, | ||

| IN PULONG | HackFlags | ||

| ) |

Definition at line 430 of file bussupp.c.

Referenced by HalpInitializePciBus().

◆ HalpGetPciBridgeConfig()

Definition at line 642 of file bussupp.c.

Referenced by HalpInitializePciBus().

◆ HalpInitBusHandlers()

Definition at line 1263 of file bussupp.c.

◆ HalpInitializePciBus()

Definition at line 1023 of file bussupp.c.

◆ HalpIsBridgeDevice()

| BOOLEAN NTAPI HalpIsBridgeDevice | ( | IN PPCI_COMMON_CONFIG | PciData | ) |

Definition at line 628 of file bussupp.c.

Referenced by HalpGetPciBridgeConfig().

◆ HalpIsIdeDevice()

| BOOLEAN NTAPI HalpIsIdeDevice | ( | IN PPCI_COMMON_CONFIG | PciData | ) |

Definition at line 575 of file bussupp.c.

Referenced by HalpInitializePciBus().

◆ HalpIsRecognizedCard()

| BOOLEAN NTAPI HalpIsRecognizedCard | ( | IN PPCI_REGISTRY_INFO_INTERNAL | PciRegistryInfo, |

| IN PPCI_COMMON_CONFIG | PciData, | ||

| IN ULONG | Flags | ||

| ) |

Definition at line 494 of file bussupp.c.

Referenced by HalpInitializePciBus().

◆ HalpIsValidPCIDevice()

| BOOLEAN NTAPI HalpIsValidPCIDevice | ( | IN PBUS_HANDLER | BusHandler, |

| IN PCI_SLOT_NUMBER | Slot | ||

| ) |

Definition at line 368 of file bussupp.c.

Referenced by HalpInitializePciBus().

◆ HalpMarkChipsetDecode() [1/2]

Definition at line 235 of file bussupp.c.

◆ HalpMarkChipsetDecode() [2/2]

Referenced by HalpInitializePciBus().

◆ HalpRegisterInternalBusHandlers()

Definition at line 159 of file bussupp.c.

Referenced by HalpInitBusHandlers().

◆ HalpRegisterKdSupportFunctions()

Definition at line 1272 of file bussupp.c.

◆ HalSetBusData()

| ULONG NTAPI HalSetBusData | ( | IN BUS_DATA_TYPE | BusDataType, |

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 1621 of file bussupp.c.

◆ HalSetBusDataByOffset()

| ULONG NTAPI HalSetBusDataByOffset | ( | IN BUS_DATA_TYPE | BusDataType, |

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Offset, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 1641 of file bussupp.c.

Referenced by HalSetBusData().

◆ HalTranslateBusAddress()

| BOOLEAN NTAPI HalTranslateBusAddress | ( | IN INTERFACE_TYPE | InterfaceType, |

| IN ULONG | BusNumber, | ||

| IN PHYSICAL_ADDRESS | BusAddress, | ||

| IN OUT PULONG | AddressSpace, | ||

| OUT PPHYSICAL_ADDRESS | TranslatedAddress | ||

| ) |

Definition at line 1674 of file bussupp.c.

Referenced by HaliFindBusAddressTranslation().

◆ ShowSize() [1/2]

Referenced by HalpDebugPciDumpBus().

◆ ShowSize() [2/2]

Variable Documentation

◆ HalpPCIConfigLock

|

extern |

Definition at line 22 of file pcibus.c.

Referenced by HalpInitializePciBus(), HalpInitializePciStubs(), HalpPCIReleaseSynchronizationType2(), HalpPCIReleaseSynchronzationType1(), HalpPCISynchronizeType1(), and HalpPCISynchronizeType2().

◆ HalpPciIrqMask

| ULONG HalpPciIrqMask |

Definition at line 104 of file bussupp.c.

Referenced by HalpInitializePciBus().

◆ WarningsGiven

|

static |

Definition at line 425 of file bussupp.c.

Referenced by HalpFixupPciSupportedRanges(), HalpGetPciBridgeConfig(), PataProcessAtapiRequest(), and PataProcessAtaRequest().