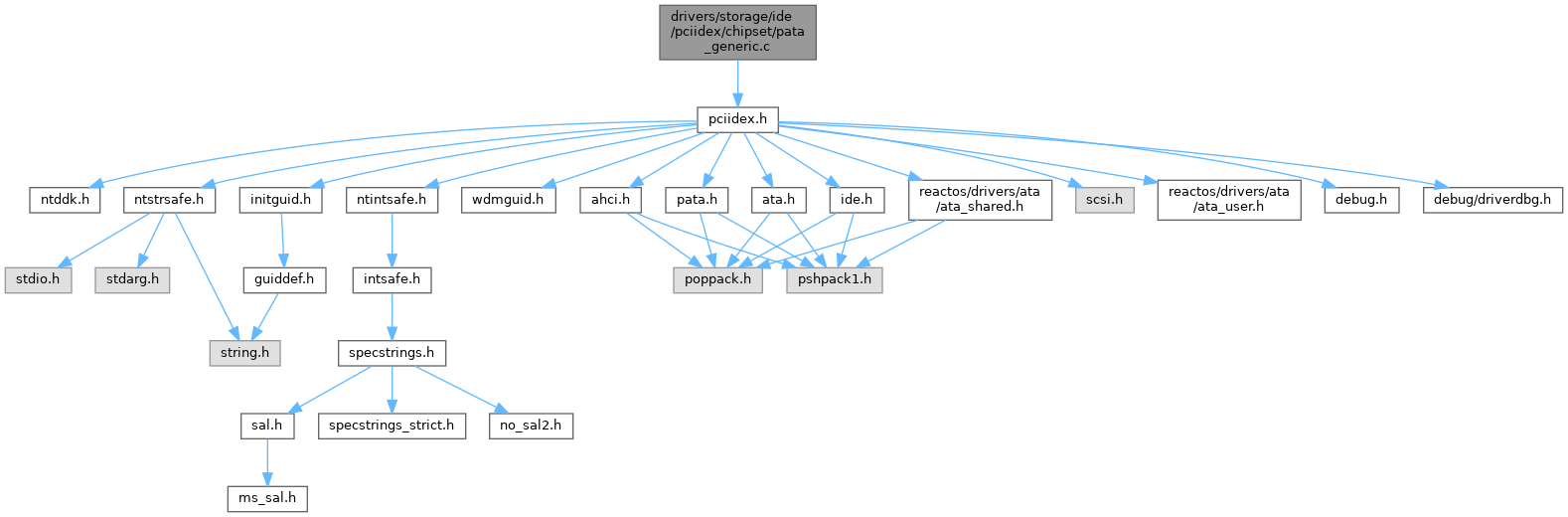

#include "pciidex.h"

Go to the source code of this file.

Variables | |

| static const ULONG | AtapModeToCycleTime [] |

| static const ATA_TIMING | AtapTimingTable [] |

Function Documentation

◆ AtaAcpiFindModeForCycleTime()

|

static |

Definition at line 202 of file pata_generic.c.

Referenced by PciIdeAcpiSetTransferMode().

◆ AtaCalculateTimings()

|

static |

Definition at line 62 of file pata_generic.c.

Referenced by AtaSelectTimings().

◆ AtaGetClocks()

Definition at line 53 of file pata_generic.c.

Referenced by AtaCalculateTimings().

◆ AtaSelectTimings()

| VOID AtaSelectTimings | ( | _In_reads_(MAX_IDE_DEVICE) PCHANNEL_DEVICE_CONFIG * | DeviceList, |

| _Out_writes_all_(MAX_IDE_DEVICE) PATA_TIMING | Timings, | ||

| _In_range_(>, 0) ULONG | ClockPeriodPs, | ||

| _In_ ULONG | Flags | ||

| ) |

Definition at line 116 of file pata_generic.c.

Referenced by AmdSetTransferMode(), CmdSetTransferMode(), Via6421SetTransferMode(), and ViaSetTransferMode().

◆ PataClaimLegacyAddressRanges()

|

static |

Definition at line 452 of file pata_generic.c.

Referenced by PciIdeParseResources().

◆ PataEnableInterrupts()

Definition at line 965 of file pata_generic.c.

Referenced by PciIdeCreateChannelData().

◆ PataReleaseLegacyAddressRanges()

|

static |

Definition at line 433 of file pata_generic.c.

Referenced by PciIdeFreeResources().

◆ PciIdeAcpiSetTransferMode()

|

static |

Definition at line 259 of file pata_generic.c.

Referenced by PciIdeGenericSetTransferMode().

◆ PciIdeAllocateMemory()

Definition at line 511 of file pata_generic.c.

Referenced by PciIdeCreateChannelData().

◆ PciIdeAssignLegacyResources()

|

static |

Definition at line 723 of file pata_generic.c.

Referenced by PciIdeParseResources().

◆ PciIdeAssignNativeResources()

|

static |

Definition at line 689 of file pata_generic.c.

Referenced by PciIdeParseResources().

◆ PciIdeAttachChannel()

Definition at line 1057 of file pata_generic.c.

◆ PciIdeBiosSetTransferMode()

|

static |

Definition at line 383 of file pata_generic.c.

Referenced by PciIdeGenericSetTransferMode().

◆ PciIdeConnectInterrupt()

Definition at line 1012 of file pata_generic.c.

Referenced by PciIdeXPdoStartDevice().

◆ PciIdeControllerInitDma()

|

static |

Definition at line 565 of file pata_generic.c.

Referenced by PciIdeGetControllerProperties().

◆ PciIdeCreateChannelData()

| NTSTATUS PciIdeCreateChannelData | ( | _In_ PATA_CONTROLLER | Controller, |

| _In_ ULONG | HwExtensionSize | ||

| ) |

Definition at line 1072 of file pata_generic.c.

Referenced by AmdGetControllerProperties(), AtiGetControllerProperties(), CmdGetControllerProperties(), IntelGetControllerProperties(), PataGetControllerProperties(), PciIdeGetControllerProperties(), PcTechGetControllerProperties(), Sil680GetControllerProperties(), SvwPataGetControllerProperties(), SvwSataGetControllerProperties(), ToshibaGetControllerProperties(), Via6421GetControllerProperties(), ViaCx700GetControllerProperties(), and ViaGetControllerProperties().

◆ PciIdeFreeMemory()

Definition at line 485 of file pata_generic.c.

Referenced by PciIdeCreateChannelData().

◆ PciIdeFreeResources()

Definition at line 877 of file pata_generic.c.

Referenced by PciIdeXPdoStopDevice().

◆ PciIdeGenericSetTransferMode()

|

static |

Definition at line 416 of file pata_generic.c.

Referenced by PciIdeCreateChannelData().

◆ PciIdeGetChannelState()

| IDE_CHANNEL_STATE PciIdeGetChannelState | ( | _In_ PATA_CONTROLLER | Controller, |

| _In_ ULONG | Channel | ||

| ) |

Definition at line 902 of file pata_generic.c.

Referenced by PciIdeXGetChannelState().

◆ PciIdeGetControllerProperties()

| NTSTATUS PciIdeGetControllerProperties | ( | _Inout_ PATA_CONTROLLER | Controller | ) |

Definition at line 1121 of file pata_generic.c.

◆ PciIdeInitTaskFileIoResources()

| VOID PciIdeInitTaskFileIoResources | ( | _In_ PCHANNEL_DATA_PATA | ChanData, |

| _In_ ULONG_PTR | CommandPortBase, | ||

| _In_ ULONG_PTR | ControlPortBase, | ||

| _In_ ULONG | CommandBlockSpare | ||

| ) |

Definition at line 663 of file pata_generic.c.

Referenced by PciIdeAssignLegacyResources(), PciIdeAssignNativeResources(), SvwSataParseResources(), and Via6421ParseResources().

◆ PciIdeIsDmaStatusValid()

Definition at line 544 of file pata_generic.c.

Referenced by PciIdeControllerInitDma().

◆ PciIdeParseResources()

| NTSTATUS PciIdeParseResources | ( | _In_ PCHANNEL_DATA_PATA | ChanData, |

| _In_ PCM_RESOURCE_LIST | ResourcesTranslated | ||

| ) |

Definition at line 849 of file pata_generic.c.

Referenced by PataGetControllerProperties(), and PciIdeXPdoStartDevice().

◆ SataSetTransferMode()

| VOID SataSetTransferMode | ( | _In_ PATA_CONTROLLER | Controller, |

| _In_ ULONG | Channel, | ||

| _In_reads_(MAX_IDE_DEVICE) PCHANNEL_DEVICE_CONFIG * | DeviceList | ||

| ) |

Definition at line 184 of file pata_generic.c.

Variable Documentation

◆ AtapModeToCycleTime

Definition at line 14 of file pata_generic.c.

Referenced by AtaAcpiFindModeForCycleTime(), and AtaCalculateTimings().

◆ AtapTimingTable

|

static |

Definition at line 29 of file pata_generic.c.

Referenced by AtaCalculateTimings().