#include "pciidex.h"

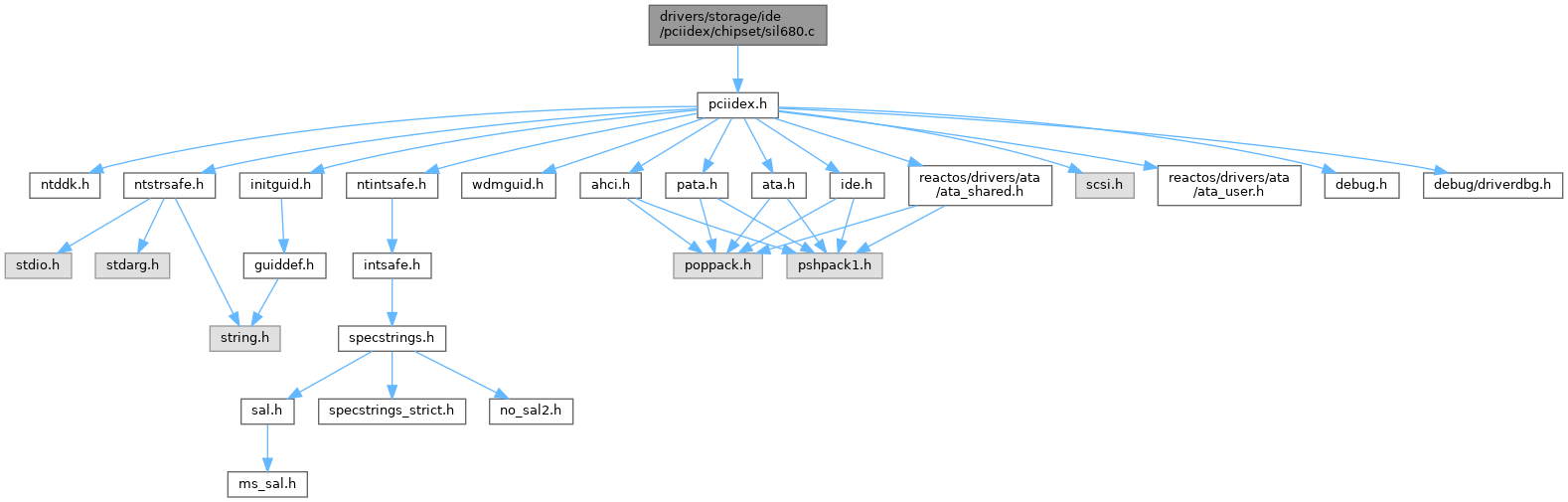

Include dependency graph for sil680.c:

Go to the source code of this file.

Macros | |

| #define | PCI_DEV_SIL0680 0x0680 |

| #define | SIL_REG_XFER_MODE(Channel) (0x80 + ((Channel) << 2)) |

| #define | SIL_REG_SYS_CFG 0x8A |

| #define | SIL_REG_CFG(Channel) (0xA0 + ((Channel) << 4)) |

| #define | SIL_REG_STATUS(Channel) (0xA1 + ((Channel) << 4)) |

| #define | SIL_REG_TF_TIM(Channel) (0xA2 + ((Channel) << 4)) |

| #define | SIL_REG_PIO_TIMING(Channel, Drive) (0xA4 + ((Channel) << 4) + ((Drive) << 1)) |

| #define | SIL_REG_DMA_TIMING(Channel, Drive) (0xA8 + ((Channel) << 4) + ((Drive) << 1)) |

| #define | SIL_REG_UDMA_TIMING(Channel, Drive) (0xAC + ((Channel) << 4) + ((Drive) << 1)) |

| #define | SIL_CFG_CABLE_80 0x00000001 |

| #define | SIL_CFG_MONITOR_IORDY 0x00000200 |

| #define | SIL_STATUS_INTR 0x08 |

| #define | SIL_CLK_MASK 0x30 |

| #define | SIL_CLK_100MHZ 0x00 |

| #define | SIL_CLK_133MHZ 0x10 |

| #define | SIL_CLK_X2 0x20 |

| #define | SIL_CLK_DISABLED 0x30 |

Functions | |

| static VOID | Sil680SetTransferMode (_In_ PATA_CONTROLLER Controller, _In_ ULONG Channel, _In_reads_(MAX_IDE_DEVICE) PCHANNEL_DEVICE_CONFIG *DeviceList) |

| static BOOLEAN | Sil680CheckInterrupt (_In_ PCHANNEL_DATA_PATA ChanData) |

| NTSTATUS | Sil680GetControllerProperties (_Inout_ PATA_CONTROLLER Controller) |

Variables | |

| static const USHORT | Sil680TaskFileTimings [] |

| static const USHORT | Sil680PioTimings [] |

| static const USHORT | Sil680MwDmaTimings [] |

| static const UCHAR | Sil680UdmaTimings [2][7] |

Macro Definition Documentation

◆ PCI_DEV_SIL0680

◆ SIL_CFG_CABLE_80

◆ SIL_CFG_MONITOR_IORDY

◆ SIL_CLK_100MHZ

◆ SIL_CLK_133MHZ

◆ SIL_CLK_DISABLED

◆ SIL_CLK_MASK

◆ SIL_CLK_X2

◆ SIL_REG_CFG

◆ SIL_REG_DMA_TIMING

◆ SIL_REG_PIO_TIMING

◆ SIL_REG_STATUS

◆ SIL_REG_SYS_CFG

◆ SIL_REG_TF_TIM

◆ SIL_REG_UDMA_TIMING

◆ SIL_REG_XFER_MODE

◆ SIL_STATUS_INTR

Function Documentation

◆ Sil680CheckInterrupt()

|

static |

Definition at line 202 of file sil680.c.

204{

205 PATA_CONTROLLER Controller = ChanData->Controller;

207

210}

FORCEINLINE UCHAR PciRead8(_In_ PATA_CONTROLLER Controller, _In_ ULONG ConfigDataOffset)

Definition: pciidex.h:847

Definition: pciidex.h:170

Referenced by Sil680GetControllerProperties().

◆ Sil680GetControllerProperties()

| NTSTATUS Sil680GetControllerProperties | ( | _Inout_ PATA_CONTROLLER | Controller | ) |

Definition at line 214 of file sil680.c.

216{

219

220 PAGED_CODE();

222

225

229

231 {

234

236 ChanData->SetTransferMode = Sil680SetTransferMode;

238

239 /* Check for 80-conductor cable */

242 {

244 ChanData->TransferModeSupported &= ~UDMA_80C_ALL;

245 }

246 }

247

249}

GLsizei GLenum const GLvoid GLsizei GLenum GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLint GLint GLint GLshort GLshort GLshort GLubyte GLubyte GLubyte GLuint GLuint GLuint GLushort GLushort GLushort GLbyte GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLfloat GLint GLint GLint GLint GLshort GLshort GLshort GLshort GLubyte GLubyte GLubyte GLubyte GLuint GLuint GLuint GLuint GLushort GLushort GLushort GLushort GLboolean const GLdouble const GLfloat const GLint const GLshort const GLbyte const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLdouble const GLfloat const GLfloat const GLint const GLint const GLshort const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort GLenum GLenum GLenum GLfloat GLenum GLint GLenum GLenum GLenum GLfloat GLenum GLenum GLint GLenum GLfloat GLenum GLint GLint GLushort GLenum GLenum GLfloat GLenum GLenum GLint GLfloat const GLubyte GLenum GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLint GLint GLsizei GLsizei GLint GLenum GLenum const GLvoid GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLenum const GLdouble GLenum GLenum const GLfloat GLenum GLenum const GLint GLsizei GLuint GLfloat GLuint GLbitfield GLfloat GLint GLuint GLboolean GLenum GLfloat GLenum GLbitfield GLenum GLfloat GLfloat GLint GLint const GLfloat GLenum GLfloat GLfloat GLint GLint GLfloat GLfloat GLint GLint const GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat const GLdouble const GLfloat const GLdouble const GLfloat GLint i

Definition: glfuncs.h:248

NTSTATUS PciIdeCreateChannelData(_In_ PATA_CONTROLLER Controller, _In_ ULONG HwExtensionSize)

Definition: pata_generic.c:1072

static BOOLEAN Sil680CheckInterrupt(_In_ PCHANNEL_DATA_PATA ChanData)

Definition: sil680.c:202

static VOID Sil680SetTransferMode(_In_ PATA_CONTROLLER Controller, _In_ ULONG Channel, _In_reads_(MAX_IDE_DEVICE) PCHANNEL_DEVICE_CONFIG *DeviceList)

Definition: sil680.c:71

Definition: pciidex.h:293

_Must_inspect_result_ _In_ WDFDEVICE _In_ PWDF_CHILD_LIST_CONFIG Config

Definition: wdfchildlist.h:476

Referenced by PciIdeGetControllerProperties().

◆ Sil680SetTransferMode()

|

static |

Definition at line 71 of file sil680.c.

75{

77 UCHAR ModeReg;

79

81 "MODE %08lX\n"

82 "CFG %08lX\n"

83 "PIO %08lX\n"

84 "DMA %08lX\n"

85 "UDMA %08lX\n",

86 Channel,

92

93 SlowestPioMode = UDMA_MODE(0);

95

97 {

99 UCHAR XferMode, SysConfig;

100

102 continue;

103

104 /* PIO timings */

107

109 MonitorIoReady = TRUE;

110

112 {

114

115 /* Try to enable the 133MHz IDE clock */

117 {

119

121 }

122

123 /* If we are unable to do so, skip UDMA6 selection */

126 {

128

131 }

132 }

133

134 /* UDMA timings */

136 {

138 USHORT UdmaTim;

139

140 XferMode = 3;

141

143 UdmaTim &= ~0x003F;

146 }

147 /* DMA timings */

149 {

151

152 XferMode = 2;

153

155 }

156 else

157 {

159 XferMode = 1;

160 else

161 XferMode = 0;

162 }

163

164 ModeReg &= ~(0x03 << (i * 4));

165 ModeReg |= XferMode << (i * 4);

166 }

167

168 /* Transfer mode */

170

172 if (MonitorIoReady)

174 else

175 Config &= ~SIL_CFG_MONITOR_IORDY;

176

177 /* Task file timings */

179 {

180 Config &= ~0xFFFF0000;

182 }

183

185

187 "MODE %08lX\n"

188 "CFG %08lX\n"

189 "PIO %08lX\n"

190 "DMA %08lX\n"

191 "UDMA %08lX\n",

192 Channel,

194 Config,

198}

FORCEINLINE VOID PciWrite16(_In_ PATA_CONTROLLER Controller, _In_ ULONG ConfigDataOffset, _In_ USHORT Value)

Definition: pciidex.h:893

FORCEINLINE VOID PciWrite8(_In_ PATA_CONTROLLER Controller, _In_ ULONG ConfigDataOffset, _In_ UCHAR Value)

Definition: pciidex.h:883

FORCEINLINE VOID PciWrite32(_In_ PATA_CONTROLLER Controller, _In_ ULONG ConfigDataOffset, _In_ ULONG Value)

Definition: pciidex.h:903

FORCEINLINE USHORT PciRead16(_In_ PATA_CONTROLLER Controller, _In_ ULONG ConfigDataOffset)

Definition: pciidex.h:859

FORCEINLINE ULONG PciRead32(_In_ PATA_CONTROLLER Controller, _In_ ULONG ConfigDataOffset)

Definition: pciidex.h:871

unsigned char _BitScanReverse(unsigned long *_Index, unsigned long _Mask)

Definition: intrin_arm.h:180

Definition: ata_shared.h:132

Referenced by Sil680GetControllerProperties().

Variable Documentation

◆ Sil680MwDmaTimings

Initial value:

=

{

0x2208,

0x10C2,

0x10C1,

}

Definition at line 53 of file sil680.c.

Referenced by Sil680SetTransferMode().

◆ Sil680PioTimings

Initial value:

=

{

0x328A,

0x2283,

0x1104,

0x10C3,

0x10C1

}

Definition at line 44 of file sil680.c.

Referenced by Sil680SetTransferMode().

◆ Sil680TaskFileTimings

Initial value:

=

{

0x328A,

0x2283,

0x1281,

0x10C3,

0x10C1

}

Definition at line 35 of file sil680.c.

Referenced by Sil680SetTransferMode().

◆ Sil680UdmaTimings

Initial value:

=

{

{ 0x0B, 0x07, 0x05, 0x04, 0x02, 0x01 },

{ 0x0F, 0x0B, 0x07, 0x05, 0x03, 0x02, 0x01 },

}

Definition at line 60 of file sil680.c.

Referenced by Sil680SetTransferMode().