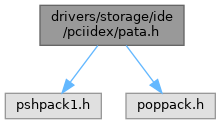

#include <pshpack1.h>#include <poppack.h>

Include dependency graph for pata.h:

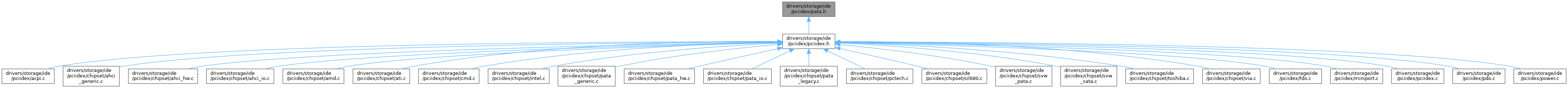

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | _PCIIDE_PRD_TABLE_ENTRY |

| struct | _ATA_TIMING |

Typedefs | |

| typedef struct _PCIIDE_PRD_TABLE_ENTRY | PCIIDE_PRD_TABLE_ENTRY |

| typedef struct _PCIIDE_PRD_TABLE_ENTRY * | PPCIIDE_PRD_TABLE_ENTRY |

| typedef USHORT | ATATIM |

| typedef struct _ATA_TIMING | ATA_TIMING |

| typedef struct _ATA_TIMING * | PATA_TIMING |

Functions | |

| C_ASSERT (CMD_FLAG_DMA_TRANSFER==(CMD_FLAG_ATAPI_PIO_TRANSFER|CMD_FLAG_ATA_PIO_TRANSFER)) | |

| C_ASSERT (CMD_FLAG_DATA_IN==REQUEST_FLAG_DATA_IN) | |

| C_ASSERT (CMD_FLAG_DATA_OUT==REQUEST_FLAG_DATA_OUT) | |

| C_ASSERT (CMD_FLAG_AWAIT_INTERRUPT==REQUEST_FLAG_POLL) | |

| FORCEINLINE ATATIM | CLAMP_TIMING (_In_ ATATIM Value, _In_ ATATIM Minimum, _In_ ATATIM Maximum) |

| FORCEINLINE VOID | ATA_SELECT_DEVICE (_In_ PCHANNEL_DATA_PATA ChanData, _In_ UCHAR DeviceNumber, _In_ UCHAR DeviceSelect) |

| FORCEINLINE UCHAR | ATA_WAIT (_In_ PCHANNEL_DATA_PATA ChanData, _In_range_(>, 0) ULONG Timeout, _In_ UCHAR Mask, _In_ UCHAR Value) |

Macro Definition Documentation

◆ ATA_IO_WAIT

| #define ATA_IO_WAIT | ( | ) | KeStallExecutionProcessor(1) |

◆ ATA_READ

| #define ATA_READ | ( | Port, | |

| Ctx, | |||

| MmioFlag | |||

| ) | AtaReadPortUchar(Port, (Ctx)->ChanInfo & CHANNEL_FLAG_##MmioFlag) |

◆ ATA_READ_BLOCK_16

◆ ATA_READ_BLOCK_32

◆ ATA_TIME_BUSY_NORMAL

◆ ATA_TIME_BUSY_POLL

◆ ATA_TIME_BUSY_RESET

| #define ATA_TIME_BUSY_RESET (10000 / PORT_TIMER_TICK_MS) |

◆ ATA_TIME_BUSY_SELECT

◆ ATA_TIME_DRQ_ASSERT

◆ ATA_TIME_DRQ_CLEAR

◆ ATA_TIME_PHASE_CHANGE

◆ ATA_TIME_RESET_SELECT

| #define ATA_TIME_RESET_SELECT (2000 / PORT_TIMER_TICK_MS) |

◆ ATA_WRITE

◆ ATA_WRITE_BLOCK_16

◆ ATA_WRITE_BLOCK_32

◆ ATA_WRITE_ULONG

◆ ATAPI_INT_REASON_AWAIT_CDB

| #define ATAPI_INT_REASON_AWAIT_CDB (IDE_STATUS_DRQ | ATAPI_INT_REASON_COD) |

◆ ATAPI_INT_REASON_COD

| #define ATAPI_INT_REASON_COD 0x01 |

◆ ATAPI_INT_REASON_DATA_IN

| #define ATAPI_INT_REASON_DATA_IN (ATAPI_INT_REASON_IO | IDE_STATUS_DRQ) |

◆ ATAPI_INT_REASON_DATA_OUT

| #define ATAPI_INT_REASON_DATA_OUT IDE_STATUS_DRQ |

◆ ATAPI_INT_REASON_IO

◆ ATAPI_INT_REASON_MASK

| #define ATAPI_INT_REASON_MASK (ATAPI_INT_REASON_IO | ATAPI_INT_REASON_COD) |

◆ ATAPI_INT_REASON_RELEASE

◆ ATAPI_INT_REASON_STATUS

| #define ATAPI_INT_REASON_STATUS (ATAPI_INT_REASON_IO | ATAPI_INT_REASON_COD) |

◆ ATAPI_INT_REASON_STATUS_NEC

| #define ATAPI_INT_REASON_STATUS_NEC 0x00 |

◆ ATAPI_INT_REASON_TAG

| #define ATAPI_INT_REASON_TAG 0xF8 |

◆ ATAPI_MAX_DRQ_DATA_BLOCK

| #define ATAPI_MAX_DRQ_DATA_BLOCK 0xFFFE |

◆ CHANNEL_PC98_MAX_DEVICES

| #define CHANNEL_PC98_MAX_DEVICES 4 |

◆ CHANNEL_PCAT_MAX_DEVICES

◆ CMD_FLAG_ATA_PIO_TRANSFER

◆ CMD_FLAG_ATAPI_PIO_TRANSFER

◆ CMD_FLAG_AWAIT_CDB

◆ CMD_FLAG_AWAIT_INTERRUPT

◆ CMD_FLAG_DATA_IN

◆ CMD_FLAG_DATA_OUT

◆ CMD_FLAG_DMA_TRANSFER

◆ CMD_FLAG_NONE

◆ CMD_FLAG_TRANSFER_MASK

◆ IDE_DC_ALWAYS

◆ IDE_DRIVE_SELECT

◆ IDE_FEATURE_DMA

◆ IDE_FEATURE_DMADIR

◆ IDE_FEATURE_PIO

◆ IDE_HIGH_ORDER_BYTE

◆ MWDMA_MODES

| #define MWDMA_MODES | ( | MinMode, | |

| MaxMode | |||

| ) | (NUM_TO_BITMAP(MWDMA_MODE((MaxMode) + 1)) & ~NUM_TO_BITMAP(MWDMA_MODE(MinMode))) |

◆ NUM_TO_BITMAP

| #define NUM_TO_BITMAP | ( | num | ) | (0xFFFFFFFF >> (RTL_BITS_OF(ULONG) - (num))) |

◆ PATA_CHANNEL_QUEUE_DEPTH

◆ PATA_CHANNEL_SLOT

| #define PATA_CHANNEL_SLOT 0 |

◆ PC98_ATA_BANK

◆ PC98_ATA_BANK_32BIT_PORT

◆ PCI_VEN_AMD

◆ PCI_VEN_ATI

◆ PCI_VEN_CAVIUM

◆ PCI_VEN_CMD

◆ PCI_VEN_INTEL

◆ PCI_VEN_NVIDIA

◆ PCI_VEN_PC_TECH

◆ PCI_VEN_SERVERWORKS

◆ PCI_VEN_TOSHIBA

◆ PCI_VEN_VIA

◆ PCIIDE_COMMAND_IO_RANGE_LENGTH

◆ PCIIDE_CONTROL_IO_BAR_OFFSET

◆ PCIIDE_CONTROL_IO_RANGE_LENGTH

◆ PCIIDE_DMA_COMMAND

◆ PCIIDE_DMA_COMMAND_READ_FROM_SYSTEM_MEMORY

◆ PCIIDE_DMA_COMMAND_START

◆ PCIIDE_DMA_COMMAND_STOP

| #define PCIIDE_DMA_COMMAND_STOP 0x00 |

◆ PCIIDE_DMA_COMMAND_WRITE_TO_SYSTEM_MEMORY

◆ PCIIDE_DMA_IO_BAR

◆ PCIIDE_DMA_IO_RANGE_LENGTH

◆ PCIIDE_DMA_PRDT_PHYSICAL_ADDRESS

◆ PCIIDE_DMA_SECONDARY_CHANNEL_OFFSET

| #define PCIIDE_DMA_SECONDARY_CHANNEL_OFFSET 8 |

◆ PCIIDE_DMA_STATUS

◆ PCIIDE_DMA_STATUS_ACTIVE

| #define PCIIDE_DMA_STATUS_ACTIVE 0x01 |

◆ PCIIDE_DMA_STATUS_DRIVE0_DMA_CAPABLE

◆ PCIIDE_DMA_STATUS_DRIVE1_DMA_CAPABLE

◆ PCIIDE_DMA_STATUS_ERROR

◆ PCIIDE_DMA_STATUS_INTERRUPT

◆ PCIIDE_DMA_STATUS_RESERVED1

◆ PCIIDE_DMA_STATUS_RESERVED2

◆ PCIIDE_DMA_STATUS_SIMPLEX

◆ PCIIDE_LEGACY_COMMAND_IO_RANGE_LENGTH

◆ PCIIDE_LEGACY_CONTROL_IO_RANGE_LENGTH

◆ PCIIDE_LEGACY_PRIMARY_COMMAND_BASE

◆ PCIIDE_LEGACY_PRIMARY_CONTROL_BASE

◆ PCIIDE_LEGACY_PRIMARY_IRQ

◆ PCIIDE_LEGACY_RESOURCE_COUNT

| #define PCIIDE_LEGACY_RESOURCE_COUNT 3 |

◆ PCIIDE_LEGACY_SECONDARY_COMMAND_BASE

◆ PCIIDE_LEGACY_SECONDARY_CONTROL_BASE

◆ PCIIDE_LEGACY_SECONDARY_IRQ

◆ PCIIDE_PRD_END_OF_TABLE

◆ PCIIDE_PRD_LENGTH_MASK

◆ PCIIDE_PRD_LIMIT

◆ PCIIDE_PROGIF_DMA_CAPABLE

◆ PCIIDE_PROGIF_PRIMARY_CHANNEL_NATIVE_MODE

| #define PCIIDE_PROGIF_PRIMARY_CHANNEL_NATIVE_MODE 0x01 |

◆ PCIIDE_PROGIF_PRIMARY_CHANNEL_NATIVE_MODE_CAPABLE

| #define PCIIDE_PROGIF_PRIMARY_CHANNEL_NATIVE_MODE_CAPABLE 0x02 |

◆ PCIIDE_PROGIF_SECONDARY_CHANNEL_NATIVE_MODE

◆ PCIIDE_PROGIF_SECONDARY_CHANNEL_NATIVE_MODE_CAPABLE

| #define PCIIDE_PROGIF_SECONDARY_CHANNEL_NATIVE_MODE_CAPABLE 0x08 |

◆ SATA_ALL

◆ SHARED_ADDR_TIMINGS

◆ SHARED_CMD_TIMINGS

◆ SHARED_DATA_TIMINGS

◆ UDMA_80C_ALL

| #define UDMA_80C_ALL (UDMA_MODE3 | UDMA_MODE4 | UDMA_MODE5 | UDMA_MODE6) |

◆ UDMA_MODES

| #define UDMA_MODES | ( | MinMode, | |

| MaxMode | |||

| ) | (NUM_TO_BITMAP(UDMA_MODE((MaxMode) + 1)) & ~NUM_TO_BITMAP(UDMA_MODE(MinMode))) |

Typedef Documentation

◆ ATA_TIMING

| typedef struct _ATA_TIMING ATA_TIMING |

◆ ATATIM

◆ PATA_TIMING

| typedef struct _ATA_TIMING * PATA_TIMING |

◆ PCIIDE_PRD_TABLE_ENTRY

Physical Region Descriptor Table Entry

◆ PPCIIDE_PRD_TABLE_ENTRY

Function Documentation

◆ ATA_SELECT_DEVICE()

| FORCEINLINE VOID ATA_SELECT_DEVICE | ( | _In_ PCHANNEL_DATA_PATA | ChanData, |

| _In_ UCHAR | DeviceNumber, | ||

| _In_ UCHAR | DeviceSelect | ||

| ) |

Definition at line 271 of file pata.h.

275{

276#if defined(_M_IX86)

277 /* NEC extension to allow 4 drives per channel */

279 (ChanData->LastAtaBankId != DeviceNumber))

280 {

281 UCHAR AtaBank;

282

283 ChanData->LastAtaBankId = DeviceNumber;

284

285 /* The 0x432 port is used to select the primary (0) or secondary (1) IDE channel */

286 AtaBank = DeviceNumber >> 1;

287

289 AtaBank |= PC98_ATA_BANK_32BIT_PORT;

290

292 }

293#endif

294

295 ATA_WRITE(ChanData->Regs.Device, DeviceSelect, ChanData, MRES_TF);

296 ATA_IO_WAIT();

297}

Referenced by PataChangeInterruptMode(), PataIsDevicePresent(), PataResetChannel(), and PataStartIo().

◆ ATA_WAIT()

| FORCEINLINE UCHAR ATA_WAIT | ( | _In_ PCHANNEL_DATA_PATA | ChanData, |

| _In_range_(>, 0) ULONG | Timeout, | ||

| _In_ UCHAR | Mask, | ||

| _In_ UCHAR | Value | ||

| ) |

Definition at line 301 of file pata.h.

306{

307 UCHAR IdeStatus;

309

311 {

312 IdeStatus = ChanData->ReadStatus(ChanData);

314 break;

315

316 if (IdeStatus == 0xFF)

317 break;

318

319 KeStallExecutionProcessor(10);

320 }

321

322 return IdeStatus;

323}

GLsizei GLenum const GLvoid GLsizei GLenum GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLint GLint GLint GLshort GLshort GLshort GLubyte GLubyte GLubyte GLuint GLuint GLuint GLushort GLushort GLushort GLbyte GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLfloat GLint GLint GLint GLint GLshort GLshort GLshort GLshort GLubyte GLubyte GLubyte GLubyte GLuint GLuint GLuint GLuint GLushort GLushort GLushort GLushort GLboolean const GLdouble const GLfloat const GLint const GLshort const GLbyte const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLdouble const GLfloat const GLfloat const GLint const GLint const GLshort const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort GLenum GLenum GLenum GLfloat GLenum GLint GLenum GLenum GLenum GLfloat GLenum GLenum GLint GLenum GLfloat GLenum GLint GLint GLushort GLenum GLenum GLfloat GLenum GLenum GLint GLfloat const GLubyte GLenum GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLint GLint GLsizei GLsizei GLint GLenum GLenum const GLvoid GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLenum const GLdouble GLenum GLenum const GLfloat GLenum GLenum const GLint GLsizei GLuint GLfloat GLuint GLbitfield GLfloat GLint GLuint GLboolean GLenum GLfloat GLenum GLbitfield GLenum GLfloat GLfloat GLint GLint const GLfloat GLenum GLfloat GLfloat GLint GLint GLfloat GLfloat GLint GLint const GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat const GLdouble const GLfloat const GLdouble const GLfloat GLint i

Definition: glfuncs.h:248

_Must_inspect_result_ _In_ WDFKEY _In_ PCUNICODE_STRING _Out_opt_ PUSHORT _Inout_opt_ PUNICODE_STRING Value

Definition: wdfregistry.h:413

Referenced by PataChangeInterruptMode(), PataIdentifyDevice(), PataPoll(), PataProcessAtapiRequest(), PataProcessAtaRequest(), and PataStartIo().

◆ C_ASSERT() [1/4]

| C_ASSERT | ( | CMD_FLAG_AWAIT_INTERRUPT | = =REQUEST_FLAG_POLL | ) |

◆ C_ASSERT() [2/4]

| C_ASSERT | ( | CMD_FLAG_DATA_IN | = =REQUEST_FLAG_DATA_IN | ) |

◆ C_ASSERT() [3/4]

| C_ASSERT | ( | CMD_FLAG_DATA_OUT | = =REQUEST_FLAG_DATA_OUT | ) |

◆ C_ASSERT() [4/4]

| C_ASSERT | ( | CMD_FLAG_DMA_TRANSFER | = =(CMD_FLAG_ATAPI_PIO_TRANSFER|CMD_FLAG_ATA_PIO_TRANSFER) | ) |