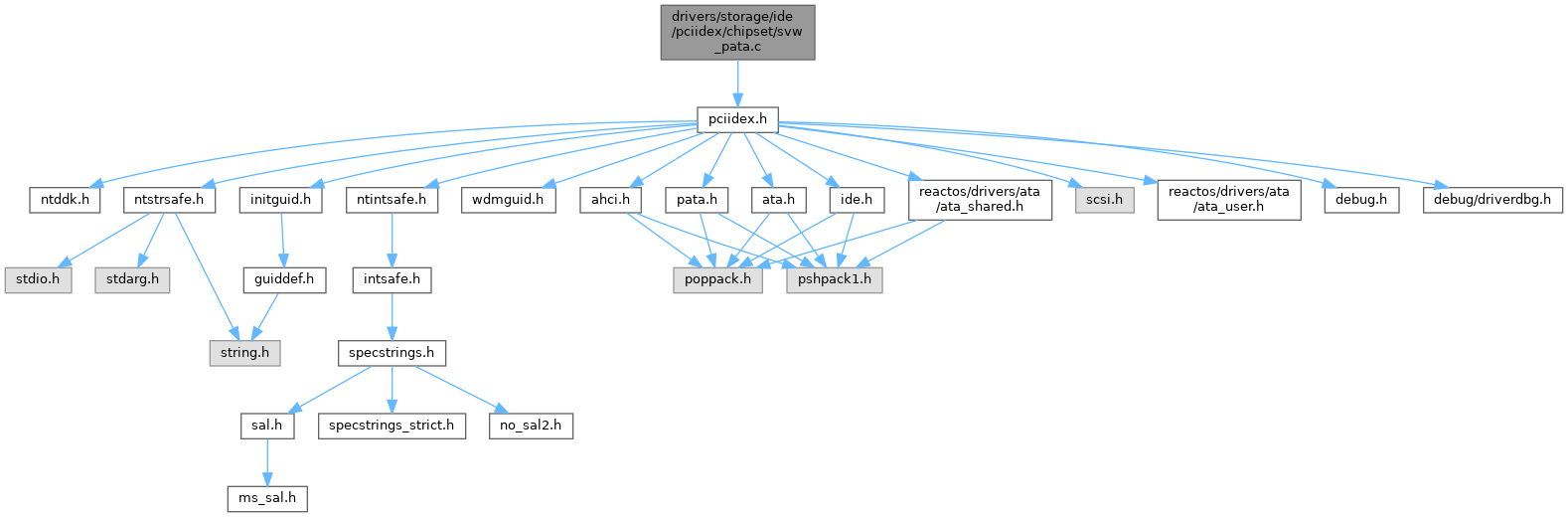

#include "pciidex.h"

Go to the source code of this file.

Macros | |

| #define | PCI_DEV_OSB4_IDE 0x0211 |

| #define | PCI_DEV_CSB5_IDE 0x0212 |

| #define | PCI_DEV_CSB6_IDE 0x0213 |

| #define | PCI_DEV_CSB6_IDE_THIRD 0x0217 |

| #define | PCI_DEV_HT1000_IDE 0x0214 |

| #define | PCI_DEV_OSB4_BRIDGE 0x0210 |

| #define | SVW_REG_PIO_TIMING 0x40 |

| #define | SVW_REG_DMA_TIMING 0x44 |

| #define | SVW_REG_PIO_MODE 0x4A |

| #define | SVW_REG_UDMA_ENABLE 0x54 |

| #define | SVW_REG_UDMA_MODE 0x56 |

| #define | SVW_REG_UDMA_CONTROL 0x5A |

| #define | SVW_UDMA_CTRL_MODE_MASK 0x03 |

| #define | SVW_UDMA_CTRL_DISABLE 0x40 |

| #define | SVW_UDMA_CTRL_MODE_UDMA4 0x02 |

| #define | SVW_UDMA_CTRL_MODE_UDMA5 0x03 |

Functions | |

| static VOID | SvwChooseDeviceSpeed (_In_ ULONG Channel, _In_ PCHANNEL_DEVICE_CONFIG Device) |

| VOID | SvwSetTransferMode (_In_ PATA_CONTROLLER Controller, _In_ ULONG Channel, _In_reads_(MAX_IDE_DEVICE) PCHANNEL_DEVICE_CONFIG *DeviceList) |

| BOOLEAN | SvwHasUdmaCable (_In_ PATA_CONTROLLER Controller, _In_ ULONG Channel) |

| static BOOLEAN | SvwOsb4PciBridgeInit (_In_ PVOID Context, _In_ ULONG BusNumber, _In_ PCI_SLOT_NUMBER PciSlot, _In_ PPCI_COMMON_HEADER PciConfig) |

| static VOID | SvwPataControllerStart (_In_ PATA_CONTROLLER Controller) |

| NTSTATUS | SvwPataGetControllerProperties (_Inout_ PATA_CONTROLLER Controller) |

Variables | |

| struct { | |

| UCHAR Value | |

| ULONG CycleTime | |

| } | SvwPioTimings [] |

| struct { | |

| UCHAR Value | |

| ULONG CycleTime | |

| } | SvwMwDmaTimings [] |

Macro Definition Documentation

◆ PCI_DEV_CSB5_IDE

| #define PCI_DEV_CSB5_IDE 0x0212 |

Definition at line 20 of file svw_pata.c.

◆ PCI_DEV_CSB6_IDE

| #define PCI_DEV_CSB6_IDE 0x0213 |

Definition at line 21 of file svw_pata.c.

◆ PCI_DEV_CSB6_IDE_THIRD

| #define PCI_DEV_CSB6_IDE_THIRD 0x0217 |

Definition at line 22 of file svw_pata.c.

◆ PCI_DEV_HT1000_IDE

| #define PCI_DEV_HT1000_IDE 0x0214 |

Definition at line 23 of file svw_pata.c.

◆ PCI_DEV_OSB4_BRIDGE

| #define PCI_DEV_OSB4_BRIDGE 0x0210 |

Definition at line 25 of file svw_pata.c.

◆ PCI_DEV_OSB4_IDE

| #define PCI_DEV_OSB4_IDE 0x0211 |

Definition at line 19 of file svw_pata.c.

◆ SVW_REG_DMA_TIMING

| #define SVW_REG_DMA_TIMING 0x44 |

Definition at line 28 of file svw_pata.c.

◆ SVW_REG_PIO_MODE

| #define SVW_REG_PIO_MODE 0x4A |

Definition at line 29 of file svw_pata.c.

◆ SVW_REG_PIO_TIMING

| #define SVW_REG_PIO_TIMING 0x40 |

Definition at line 27 of file svw_pata.c.

◆ SVW_REG_UDMA_CONTROL

| #define SVW_REG_UDMA_CONTROL 0x5A |

Definition at line 32 of file svw_pata.c.

◆ SVW_REG_UDMA_ENABLE

| #define SVW_REG_UDMA_ENABLE 0x54 |

Definition at line 30 of file svw_pata.c.

◆ SVW_REG_UDMA_MODE

| #define SVW_REG_UDMA_MODE 0x56 |

Definition at line 31 of file svw_pata.c.

◆ SVW_UDMA_CTRL_DISABLE

| #define SVW_UDMA_CTRL_DISABLE 0x40 |

Definition at line 35 of file svw_pata.c.

◆ SVW_UDMA_CTRL_MODE_MASK

| #define SVW_UDMA_CTRL_MODE_MASK 0x03 |

Definition at line 34 of file svw_pata.c.

◆ SVW_UDMA_CTRL_MODE_UDMA4

| #define SVW_UDMA_CTRL_MODE_UDMA4 0x02 |

Definition at line 37 of file svw_pata.c.

◆ SVW_UDMA_CTRL_MODE_UDMA5

| #define SVW_UDMA_CTRL_MODE_UDMA5 0x03 |

Definition at line 38 of file svw_pata.c.

Function Documentation

◆ SvwChooseDeviceSpeed()

|

static |

Definition at line 68 of file svw_pata.c.

Referenced by SvwSetTransferMode().

◆ SvwHasUdmaCable()

| BOOLEAN SvwHasUdmaCable | ( | _In_ PATA_CONTROLLER | Controller, |

| _In_ ULONG | Channel | ||

| ) |

Definition at line 213 of file svw_pata.c.

Referenced by AtiGetControllerProperties(), and SvwPataGetControllerProperties().

◆ SvwOsb4PciBridgeInit()

|

static |

Definition at line 229 of file svw_pata.c.

Referenced by SvwPataControllerStart().

◆ SvwPataControllerStart()

|

static |

Definition at line 264 of file svw_pata.c.

Referenced by SvwPataGetControllerProperties().

◆ SvwPataGetControllerProperties()

| NTSTATUS SvwPataGetControllerProperties | ( | _Inout_ PATA_CONTROLLER | Controller | ) |

Definition at line 288 of file svw_pata.c.

Referenced by PciIdeGetControllerProperties().

◆ SvwSetTransferMode()

| VOID SvwSetTransferMode | ( | _In_ PATA_CONTROLLER | Controller, |

| _In_ ULONG | Channel, | ||

| _In_reads_(MAX_IDE_DEVICE) PCHANNEL_DEVICE_CONFIG * | DeviceList | ||

| ) |

Definition at line 113 of file svw_pata.c.

Variable Documentation

◆ CycleTime

| ULONG CycleTime |

Definition at line 43 of file svw_pata.c.

Referenced by AtaTimQueryMwDmaModeSupport(), AtaTimQueryPioModeSupport(), AtaTimQuerySwDmaModeSupport(), AtaTimQueryUDmaModeSupport(), SvwChooseDeviceSpeed(), and test_query_process().

◆

| const struct { ... } SvwMwDmaTimings[] |

Referenced by SvwChooseDeviceSpeed(), and SvwSetTransferMode().

◆

| const struct { ... } SvwPioTimings[] |

Referenced by SvwChooseDeviceSpeed(), and SvwSetTransferMode().

◆ Value

Definition at line 42 of file svw_pata.c.

Referenced by SvwOsb4PciBridgeInit().