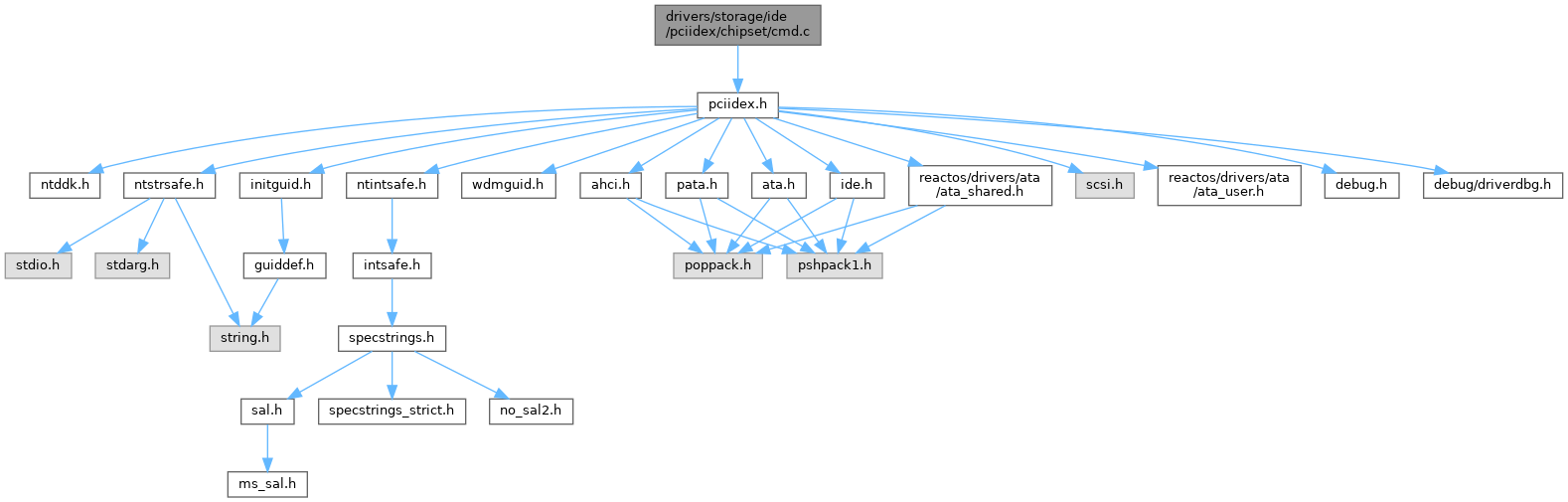

#include "pciidex.h"

Go to the source code of this file.

Classes | |

| struct | _CMD_HW_EXTENSION |

Typedefs | |

| typedef struct _CMD_HW_EXTENSION | CMD_HW_EXTENSION |

| typedef struct _CMD_HW_EXTENSION * | PCMD_HW_EXTENSION |

Functions | |

| static VOID | CmdFixRecoveryTiming (_In_ PCHANNEL_DEVICE_CONFIG Device, _Inout_ PATA_TIMING Timing, _In_ ATATIM CycleTimeClocks, _In_ ATATIM CmdActiveClocks, _In_ ATATIM CmdRecoveryClocks, _In_ ATATIM DataActiveClocks, _In_ ATATIM DataRecoveryClocks) |

| static VOID | CmdDerateTimings (_In_ PCHANNEL_DEVICE_CONFIG Device, _Inout_ PATA_TIMING Timing) |

| static UCHAR | CmdPackTimings (_In_ PATA_CONTROLLER Controller, _In_ ATATIM Active, _In_ ATATIM Recovery) |

| static VOID | CmdSetTransferMode (_In_ PATA_CONTROLLER Controller, _In_ ULONG Channel, _In_reads_(MAX_IDE_DEVICE) PCHANNEL_DEVICE_CONFIG *DeviceList) |

| static IDE_CHANNEL_STATE | CmdChannelEnabledTest (_In_ PATA_CONTROLLER Controller, _In_ ULONG Channel) |

| static BOOLEAN | CmdCheckInterruptMrdMode (_In_ PCHANNEL_DATA_PATA ChanData) |

| static BOOLEAN | CmdCheckInterruptPci (_In_ PCHANNEL_DATA_PATA ChanData) |

| static VOID | CmdControllerStart (_In_ PATA_CONTROLLER Controller) |

| NTSTATUS | CmdGetControllerProperties (_Inout_ PATA_CONTROLLER Controller) |

Variables | |

| static const UCHAR | CmdPrefetchDisable [MAX_IDE_CHANNEL][MAX_IDE_DEVICE] |

| static const ULONG | CmdPrefetchRegs [MAX_IDE_CHANNEL] |

| static const ULONG | CmdDrwTimRegs [MAX_IDE_CHANNEL][MAX_IDE_DEVICE] |

| static const ULONG | CmdArtTimRegs [MAX_IDE_CHANNEL][MAX_IDE_DEVICE] |

| static const UCHAR | CmdArtTimings [] |

| static const UCHAR | CmdUdmaTimings [6][MAX_IDE_DEVICE] |

Macro Definition Documentation

◆ CMD_ARTTIM_ART_MASK

◆ CMD_BMIDECSR_CR

◆ CMD_CFR_INTR

◆ CMD_CNTRL_CHAN_EN

◆ CMD_MRDMODE_INTR

◆ CMD_MRDMODE_INTR_CH0_BLOCK

◆ CMD_MRDMODE_INTR_CH1_BLOCK

◆ CMD_MRDMODE_READ_MULTIPLE

◆ CMD_PCI_CLOCK

◆ CMD_REG_ARTTIM0

◆ CMD_REG_ARTTIM1

◆ CMD_REG_ARTTIM23

◆ CMD_REG_BMIDECSR

◆ CMD_REG_CFR

◆ CMD_REG_CMDTIM

◆ CMD_REG_CNTRL

◆ CMD_REG_DRWTIM0

◆ CMD_REG_DRWTIM1

◆ CMD_REG_DRWTIM2

◆ CMD_REG_DRWTIM23

◆ CMD_REG_DRWTIM3

◆ CMD_REG_MRDMODE

◆ CMD_REG_UDIDETCR

◆ CMD_UDIDETCR_CLEAR

◆ CMD_UDIDETCR_EN

◆ HW_FLAGS_HAS_UDMA_REG

◆ HW_FLAGS_NEED_PIO_FIX

◆ HW_FLAGS_NO_PREFETCH

◆ HW_FLAGS_PRIMARY_ENABLED

◆ PCI_DEV_CMD0649

◆ PCI_DEV_PCI0640

◆ PCI_DEV_PCI0643

◆ PCI_DEV_PCI0646

◆ PCI_DEV_PCI0648

Typedef Documentation

◆ CMD_HW_EXTENSION

| typedef struct _CMD_HW_EXTENSION CMD_HW_EXTENSION |

◆ PCMD_HW_EXTENSION

| typedef struct _CMD_HW_EXTENSION * PCMD_HW_EXTENSION |

Function Documentation

◆ CmdChannelEnabledTest()

|

static |

Definition at line 356 of file cmd.c.

Referenced by CmdGetControllerProperties().

◆ CmdCheckInterruptMrdMode()

|

static |

Definition at line 376 of file cmd.c.

Referenced by CmdGetControllerProperties().

◆ CmdCheckInterruptPci()

|

static |

Definition at line 407 of file cmd.c.

Referenced by CmdGetControllerProperties().

◆ CmdControllerStart()

|

static |

Definition at line 424 of file cmd.c.

Referenced by CmdGetControllerProperties().

◆ CmdDerateTimings()

|

static |

Definition at line 154 of file cmd.c.

Referenced by CmdSetTransferMode().

◆ CmdFixRecoveryTiming()

|

static |

Definition at line 120 of file cmd.c.

Referenced by CmdDerateTimings().

◆ CmdGetControllerProperties()

| NTSTATUS CmdGetControllerProperties | ( | _Inout_ PATA_CONTROLLER | Controller | ) |

Definition at line 460 of file cmd.c.

Referenced by PciIdeGetControllerProperties().

◆ CmdPackTimings()

|

static |

Definition at line 194 of file cmd.c.

Referenced by CmdSetTransferMode().

◆ CmdSetTransferMode()

|

static |

Definition at line 243 of file cmd.c.

Referenced by CmdGetControllerProperties().

Variable Documentation

◆ CmdArtTimings

Definition at line 95 of file cmd.c.

Referenced by CmdSetTransferMode().

◆ CmdArtTimRegs

|

static |

◆ CmdDrwTimRegs

|

static |

◆ CmdPrefetchDisable

|

static |

Definition at line 68 of file cmd.c.

Referenced by CmdControllerStart(), and CmdSetTransferMode().

◆ CmdPrefetchRegs

|

static |

Definition at line 75 of file cmd.c.

Referenced by CmdControllerStart(), and CmdSetTransferMode().

◆ CmdUdmaTimings

|

static |

Definition at line 105 of file cmd.c.

Referenced by CmdSetTransferMode().