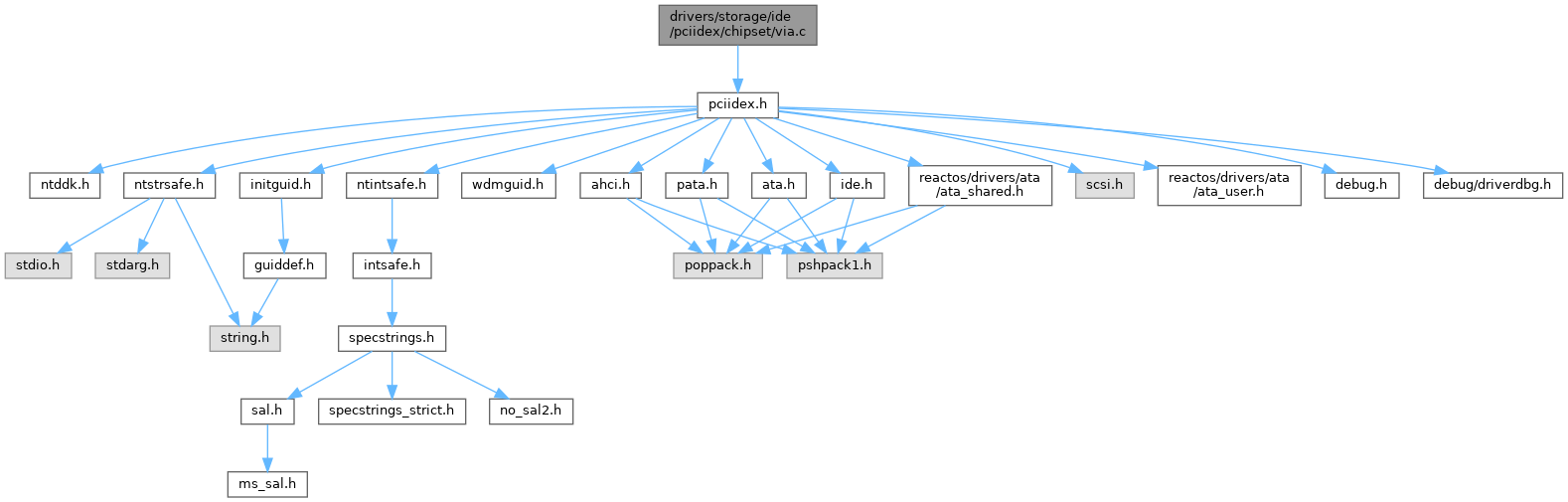

#include "pciidex.h"

Go to the source code of this file.

Variables | |

| struct { | |

| USHORT DeviceID | |

| USHORT Flags | |

| } | ViaControllerList [] |

| struct { | |

| UCHAR DefaultValue | |

| UCHAR Data [7] | |

| } | ViaUdmaTimings [] |

| static PCIIDEX_PAGED_DATA const ATA_PCI_ENABLE_BITS | ViaPataEnableBits [MAX_IDE_CHANNEL] |

| static PCIIDEX_PAGED_DATA const ATA_PCI_ENABLE_BITS | ViaCx700EnableBits [MAX_IDE_CHANNEL] |

Macro Definition Documentation

◆ GET_TYPE

◆ HW_FLAGS_CHECK_BRIDGE

◆ HW_FLAGS_HAS_UDMA_CLOCK

◆ HW_FLAGS_PCI_SCR

◆ HW_FLAGS_SINGLE_CHAN

◆ HW_FLAGS_SINGLE_PORT

◆ HW_FLAGS_TYPE_MASK

◆ PCI_DEV_BRIDGE_VT8231

◆ PCI_DEV_BRIDGE_VT8233

◆ PCI_DEV_BRIDGE_VT8233A

◆ PCI_DEV_BRIDGE_VT8233C

◆ PCI_DEV_BRIDGE_VT8235

◆ PCI_DEV_BRIDGE_VT8237

◆ PCI_DEV_BRIDGE_VT8237A

◆ PCI_DEV_BRIDGE_VT8237S

◆ PCI_DEV_BRIDGE_VT8251

◆ PCI_DEV_BRIDGE_VT8261

◆ PCI_DEV_BRIDGE_VT82C586

◆ PCI_DEV_BRIDGE_VT82C596A

◆ PCI_DEV_BRIDGE_VT82C686A

◆ PCI_DEV_CX700M2_IDE_SATA

◆ PCI_DEV_CX700M2_IDE_SATA_RAID

◆ PCI_DEV_VT6410_IDE_RAID

◆ PCI_DEV_VT6415_IDE

◆ PCI_DEV_VT6420_IDE

◆ PCI_DEV_VT6421A_RAID

◆ PCI_DEV_VT8237_SATA

◆ PCI_DEV_VT8237A_SATA

◆ PCI_DEV_VT8237A_SATA_2

◆ PCI_DEV_VT8237S_SATA

◆ PCI_DEV_VT8237S_SATA_RAID

◆ PCI_DEV_VT8251_SATA_2

◆ PCI_DEV_VT8251_SATA_AHCI

◆ PCI_DEV_VT8261_SATA

◆ PCI_DEV_VT8261_SATA_RAID

◆ PCI_DEV_VT82C576M_IDE

◆ PCI_DEV_VT82C586A_IDE

◆ PCI_DEV_VX855_IDE

◆ PCI_DEV_VX900_SATA

◆ PCI_DEV_VX900_SATA_RAID

◆ TYPE_100

◆ TYPE_133

◆ TYPE_33

◆ TYPE_66

◆ TYPE_MWDMA

◆ TYPE_SATA

◆ VIA_PCI_CLOCK

◆ VIA_REG_ADDRESS_SETUP

◆ VIA_REG_DRIVE_TIMING

◆ VIA_REG_ENABLE_CTRL

◆ VIA_REG_PORT_TIMING

◆ VIA_REG_SATA_PORT_MAP

◆ VIA_REG_SCONTROL

◆ VIA_REG_SERROR

◆ VIA_REG_SERROR_VT8237

◆ VIA_REG_SSTATUS

◆ VIA_REG_UDMA_CTRL

◆ VIA_SINGLE_CHAN_UDMA_CABLE_PRESENT

◆ VIA_UDMA_CABLE_BITS

◆ VIA_UDMA_CABLE_PRESENT

◆ VIA_UDMA_CLEAR_MASK

◆ VIA_UDMA_CLOCK_ENABLED

◆ VIA_UDMA_CLOCK_UDMA66

◆ VT6421A_FIFO_WATERMARK_64DW

◆ VT6421A_REG_SATA_CTRL

◆ VT6421A_REG_TIMING_CTRL

◆ VT6421A_REG_UDMA_CTRL

◆ VT6421A_UDMA_CABLE_PRESENT

◆ VT6421A_UDMA_SLOW

Function Documentation

◆ Via6410ControllerStart()

|

static |

Definition at line 640 of file via.c.

Referenced by ViaPataGetControllerProperties().

◆ Via6421GetControllerProperties()

|

static |

Definition at line 536 of file via.c.

Referenced by ViaGetControllerProperties().

◆ Via6421ParseResources()

|

static |

Definition at line 492 of file via.c.

Referenced by Via6421GetControllerProperties().

◆ Via6421SetTransferMode()

|

static |

Definition at line 303 of file via.c.

Referenced by Via6421GetControllerProperties().

◆ ViaClampTimings()

| VOID ViaClampTimings | ( | _Inout_ PATA_TIMING | Timing | ) |

Definition at line 165 of file via.c.

Referenced by AmdSetTransferMode(), Via6421SetTransferMode(), and ViaSetTransferMode().

◆ ViaCx700GetControllerProperties()

|

static |

Definition at line 592 of file via.c.

Referenced by ViaGetControllerProperties().

◆ ViaGetControllerProperties()

| NTSTATUS ViaGetControllerProperties | ( | _Inout_ PATA_CONTROLLER | Controller | ) |

Definition at line 859 of file via.c.

Referenced by PciIdeGetControllerProperties().

◆ ViaGetSerrOffset()

|

static |

Definition at line 344 of file via.c.

Referenced by ViaScrReadPci(), and ViaScrWritePci().

◆ ViaPataGetControllerProperties()

|

static |

Definition at line 721 of file via.c.

Referenced by ViaGetControllerProperties().

◆ ViaQuerySouthBridgeInformation()

|

static |

Definition at line 660 of file via.c.

Referenced by ViaPataGetControllerProperties().

◆ ViaSataGetControllerProperties()

|

static |

Definition at line 826 of file via.c.

Referenced by ViaGetControllerProperties().

◆ ViaSataSetTransferMode()

|

static |

Definition at line 269 of file via.c.

Referenced by Via6421GetControllerProperties().

◆ ViaScrReadIoPort()

|

static |

Definition at line 457 of file via.c.

Referenced by Via6421GetControllerProperties().

◆ ViaScrReadPci()

|

static |

Definition at line 355 of file via.c.

Referenced by ViaCx700GetControllerProperties(), and ViaSataGetControllerProperties().

◆ ViaScrWriteIoPort()

|

static |

Definition at line 474 of file via.c.

Referenced by Via6421GetControllerProperties().

◆ ViaScrWritePci()

|

static |

Definition at line 416 of file via.c.

Referenced by ViaCx700GetControllerProperties(), and ViaSataGetControllerProperties().

◆ ViaSetTransferMode()

|

static |

Definition at line 177 of file via.c.

Referenced by ViaCx700GetControllerProperties(), and ViaPataGetControllerProperties().

Variable Documentation

◆ Data

◆ DefaultValue

| UCHAR DefaultValue |

Definition at line 137 of file via.c.

Referenced by AtaGetRegistryKey(), DcConfigQueryInteger(), GetRegDWORD(), GetRegInt(), GetRegIntFromID(), and QueryInteger().

◆ DeviceID

Definition at line 112 of file via.c.

Referenced by ViaQuerySouthBridgeInformation().

◆ Flags

Definition at line 113 of file via.c.

Referenced by ViaQuerySouthBridgeInformation().

◆

| PCIIDEX_PAGED_DATA const struct { ... } ViaControllerList[] |

Referenced by ViaGetControllerProperties().

◆ ViaCx700EnableBits

|

static |

Definition at line 156 of file via.c.

Referenced by ViaCx700GetControllerProperties().

◆ ViaPataEnableBits

|

static |

Definition at line 149 of file via.c.

Referenced by ViaPataGetControllerProperties().

◆

| const struct { ... } ViaUdmaTimings[] |

Referenced by Via6421SetTransferMode(), and ViaSetTransferMode().