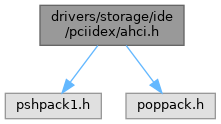

#include <pshpack1.h>#include <poppack.h>

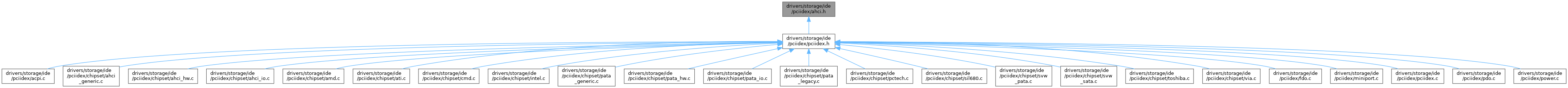

Go to the source code of this file.

Classes | |

| struct | _AHCI_FIS_HOST_TO_DEVICE |

| struct | _AHCI_FIS_PIO_SETUP |

| struct | _AHCI_FIS_DEVICE_TO_HOST |

| struct | _AHCI_FIS_SET_DEVICE_BITS |

| struct | _AHCI_RECEIVED_FIS |

| struct | _AHCI_COMMAND_HEADER |

| struct | _AHCI_COMMAND_LIST |

| struct | _AHCI_PRD_TABLE_ENTRY |

| struct | _AHCI_COMMAND_TABLE |

Functions | |

| C_ASSERT (sizeof(AHCI_FIS_HOST_TO_DEVICE)==20) | |

| C_ASSERT (sizeof(AHCI_FIS_PIO_SETUP)==20) | |

| C_ASSERT (sizeof(AHCI_FIS_DEVICE_TO_HOST)==20) | |

| C_ASSERT (sizeof(AHCI_FIS_SET_DEVICE_BITS)==8) | |

| C_ASSERT (sizeof(AHCI_RECEIVED_FIS)==256) | |

| C_ASSERT (sizeof(AHCI_COMMAND_HEADER)==32) | |

| C_ASSERT (sizeof(AHCI_PRD_TABLE_ENTRY)==16) | |

| C_ASSERT (FIELD_OFFSET(AHCI_COMMAND_TABLE, PrdTable)==128) | |

| FORCEINLINE ULONG | AHCI_HBA_READ (_In_ PVOID HbaIoBase, _In_ AHCI_HOST_BUS_ADAPTER_REGISTER Register) |

| FORCEINLINE VOID | AHCI_HBA_WRITE (_In_ PVOID HbaIoBase, _In_ AHCI_HOST_BUS_ADAPTER_REGISTER Register, _In_ ULONG Value) |

| FORCEINLINE ULONG | AHCI_PORT_READ (_In_ PVOID PortIoBase, _In_ AHCI_PORT_REGISTER Register) |

| FORCEINLINE VOID | AHCI_PORT_WRITE (_In_ PVOID PortIoBase, _In_ AHCI_PORT_REGISTER Register, _In_ ULONG Value) |

Macro Definition Documentation

◆ AHCI_BOHC_BIOS_BUSY

◆ AHCI_BOHC_BIOS_SEMAPHORE

◆ AHCI_BOHC_OS_OWNERSHIP_CHANGE

◆ AHCI_BOHC_OS_SEMAPHORE

◆ AHCI_BOHC_SMI_ON_OS_OWNERSHIP_CHANGE

◆ AHCI_CAP2_APST

◆ AHCI_CAP2_BOH

◆ AHCI_CAP2_DESO

◆ AHCI_CAP2_NVMP

◆ AHCI_CAP2_SADM

◆ AHCI_CAP2_SDS

◆ AHCI_CAP_CCCS

◆ AHCI_CAP_EMS

◆ AHCI_CAP_FBSS

◆ AHCI_CAP_ISS

◆ AHCI_CAP_NCS

◆ AHCI_CAP_NP

◆ AHCI_CAP_PMD

◆ AHCI_CAP_PSC

◆ AHCI_CAP_RSV

◆ AHCI_CAP_S64A

◆ AHCI_CAP_SAL

◆ AHCI_CAP_SALP

◆ AHCI_CAP_SAM

◆ AHCI_CAP_SCLO

◆ AHCI_CAP_SMPS

◆ AHCI_CAP_SNCQ

◆ AHCI_CAP_SPM

◆ AHCI_CAP_SSC

◆ AHCI_CAP_SSNTF

◆ AHCI_CAP_SSS

◆ AHCI_CAP_SXS

◆ AHCI_COMMAND_HEADER_ATAPI

◆ AHCI_COMMAND_HEADER_BIST

◆ AHCI_COMMAND_HEADER_CLEAR_BUSY_UPON_OK

◆ AHCI_COMMAND_HEADER_COMMAND_FIS_LENGTH

◆ AHCI_COMMAND_HEADER_PMP

◆ AHCI_COMMAND_HEADER_PMP_SHIFT

◆ AHCI_COMMAND_HEADER_PRDT_LENGTH

◆ AHCI_COMMAND_HEADER_PRDT_LENGTH_SHIFT

◆ AHCI_COMMAND_HEADER_PREFETCHABLE

◆ AHCI_COMMAND_HEADER_RESET

◆ AHCI_COMMAND_HEADER_WRITE

◆ AHCI_COMMAND_LIST_ALIGNMENT

◆ AHCI_COMMAND_TABLE_ALIGNMENT

◆ AHCI_DELAY_1_SECOND

| #define AHCI_DELAY_1_SECOND (1000 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_CLO_CLEAR

| #define AHCI_DELAY_CLO_CLEAR (10 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_CR_START_STOP

| #define AHCI_DELAY_CR_START_STOP (500 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_DET_PRESENCE

| #define AHCI_DELAY_DET_PRESENCE (40 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_DET_STABLE

| #define AHCI_DELAY_DET_STABLE (200 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_FR_START_STOP

| #define AHCI_DELAY_FR_START_STOP (500 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_INTERFACE_CHANGE

| #define AHCI_DELAY_INTERFACE_CHANGE (10 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_PMP_DET_PRESENSE

| #define AHCI_DELAY_PMP_DET_PRESENSE (100 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_PMP_DET_STABLE

| #define AHCI_DELAY_PMP_DET_STABLE (300 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_PMP_READY_DRIVE

| #define AHCI_DELAY_PMP_READY_DRIVE (400 / PORT_TIMER_TICK_MS) |

◆ AHCI_DELAY_READY_DRIVE

| #define AHCI_DELAY_READY_DRIVE (10000 / PORT_TIMER_TICK_MS) |

◆ AHCI_FBS_ACTIVE_DEV_OPT_MASK

◆ AHCI_FBS_DEV_ERROR_CLEAR

◆ AHCI_FBS_DEV_WITH_ERROR_MASK

◆ AHCI_FBS_ENABLE

◆ AHCI_FBS_ISSUE_MASK

◆ AHCI_FBS_ISSUE_SHIFT

◆ AHCI_FBS_RECEIVE_AREA_SIZE

◆ AHCI_FBS_SINGLE_DEV_ERROR

◆ AHCI_FIS_BIST_ACTIVATE

◆ AHCI_FIS_DATA

◆ AHCI_FIS_DMA_ACTIVATE_DEVICE_TO_HOST

◆ AHCI_FIS_DMA_SETUP

| #define AHCI_FIS_DMA_SETUP 0x41 |

◆ AHCI_FIS_PIO_SETUP_DEVICE_TO_HOST

◆ AHCI_FIS_REGISTER_DEVICE_TO_HOST

◆ AHCI_FIS_REGISTER_HOST_TO_DEVICE

◆ AHCI_FIS_SET_DEVICE_BITS_DEVICE_TO_HOST

◆ AHCI_GHC_AE

◆ AHCI_GHC_HR

◆ AHCI_GHC_IE

◆ AHCI_GHC_MRSM

◆ AHCI_INTERNAL_SLOT

◆ AHCI_MAX_COMMAND_SLOTS

◆ AHCI_MAX_PMP_DEVICES

◆ AHCI_MAX_PORT_DEVICES

◆ AHCI_MAX_PORTS

◆ AHCI_MAX_PRD_LENGTH

◆ AHCI_MAX_PRDT_ENTRIES

◆ AHCI_PMP_BIST

◆ AHCI_PMP_CONTROL_PORT

◆ AHCI_PMP_PMREQ

◆ AHCI_PMP_SNTF

◆ AHCI_PMP_SSC

◆ AHCI_PORT_BASE

| #define AHCI_PORT_BASE | ( | HbaIoBase, | |

| PortNumber | |||

| ) | (PULONG)((ULONG_PTR)(HbaIoBase) + (PortNumber) * 0x80 + 0x100) |

◆ AHCI_PORT_INTERRUPT_MASK

| #define AHCI_PORT_INTERRUPT_MASK |

◆ AHCI_PRD_INTERRUPT_ON_COMPLETION

◆ AHCI_PXCMD_ALPE

◆ AHCI_PXCMD_APSTE

◆ AHCI_PXCMD_ASP

◆ AHCI_PXCMD_ATAPI

◆ AHCI_PXCMD_CCS

| #define AHCI_PXCMD_CCS | ( | Value | ) | (((Value) & AHCI_PXCMD_CCS_MASK) >> AHCI_PXCMD_CCS_SHIFT) |

◆ AHCI_PXCMD_CCS_MASK

◆ AHCI_PXCMD_CCS_SHIFT

◆ AHCI_PXCMD_CLO

◆ AHCI_PXCMD_CPD

◆ AHCI_PXCMD_CPS

◆ AHCI_PXCMD_CR

◆ AHCI_PXCMD_DLAE

◆ AHCI_PXCMD_ESP

◆ AHCI_PXCMD_FBSCP

◆ AHCI_PXCMD_FR

◆ AHCI_PXCMD_FRE

◆ AHCI_PXCMD_HPCP

◆ AHCI_PXCMD_ICC_ACTIVE

◆ AHCI_PXCMD_ICC_DEVSLEEP [1/2]

◆ AHCI_PXCMD_ICC_DEVSLEEP [2/2]

◆ AHCI_PXCMD_ICC_IDLE

◆ AHCI_PXCMD_ICC_MASK

◆ AHCI_PXCMD_ICC_PARTIAL

◆ AHCI_PXCMD_ICC_SLUMBER

◆ AHCI_PXCMD_MPSP

◆ AHCI_PXCMD_MPSS

◆ AHCI_PXCMD_PMA

◆ AHCI_PXCMD_POD

◆ AHCI_PXCMD_RSV

◆ AHCI_PXCMD_ST

◆ AHCI_PXCMD_SUD

◆ AHCI_PXCTL_DET_DISABLE_SATA

◆ AHCI_PXCTL_DET_IDLE

◆ AHCI_PXCTL_DET_MASK

◆ AHCI_PXCTL_DET_RESET

◆ AHCI_PXCTL_IPM_DISABLE_ALL

◆ AHCI_PXCTL_IPM_DISABLE_DEVSLEEP

◆ AHCI_PXCTL_IPM_DISABLE_NONE

◆ AHCI_PXCTL_IPM_DISABLE_PARTIAL

◆ AHCI_PXCTL_IPM_DISABLE_SLUMBER

◆ AHCI_PXCTL_IPM_MASK

◆ AHCI_PXCTL_SPD_LIMIT_LEVEL

◆ AHCI_PXCTL_SPD_LIMIT_NONE

◆ AHCI_PXCTL_SPD_LIMIT_SATA1

◆ AHCI_PXCTL_SPD_LIMIT_SATA2

◆ AHCI_PXCTL_SPD_LIMIT_SATA3

◆ AHCI_PXCTL_SPD_MASK

◆ AHCI_PXDEVSLP_ADSE

◆ AHCI_PXDEVSLP_DETO_MASK

◆ AHCI_PXDEVSLP_DITO_MASK

◆ AHCI_PXDEVSLP_DM_MASK

◆ AHCI_PXDEVSLP_DSP

◆ AHCI_PXDEVSLP_MDAT_MASK

◆ AHCI_PXIRQ_CPDS

◆ AHCI_PXIRQ_DHRS

◆ AHCI_PXIRQ_DMPS

◆ AHCI_PXIRQ_DPS

◆ AHCI_PXIRQ_DSS

◆ AHCI_PXIRQ_FATAL_ERROR

| #define AHCI_PXIRQ_FATAL_ERROR (AHCI_PXIRQ_TFES | AHCI_PXIRQ_IFS | AHCI_PXIRQ_HBDS | AHCI_PXIRQ_HBFS) |

◆ AHCI_PXIRQ_HBDS

◆ AHCI_PXIRQ_HBFS

◆ AHCI_PXIRQ_IFS

◆ AHCI_PXIRQ_INFS

◆ AHCI_PXIRQ_IPMS

◆ AHCI_PXIRQ_OFS

◆ AHCI_PXIRQ_PCS

◆ AHCI_PXIRQ_PORT_STATUS

| #define AHCI_PXIRQ_PORT_STATUS (AHCI_PXIRQ_PCS | AHCI_PXIRQ_PRCS | AHCI_PXIRQ_DMPS) |

◆ AHCI_PXIRQ_PRCS

◆ AHCI_PXIRQ_PSS

◆ AHCI_PXIRQ_RSV1

◆ AHCI_PXIRQ_RSV2

◆ AHCI_PXIRQ_SDBS

◆ AHCI_PXIRQ_TFES

◆ AHCI_PXIRQ_UFS

◆ AHCI_PXSIG_ATAPI

◆ AHCI_PXSIG_INVALID

◆ AHCI_PXSIG_MASK

◆ AHCI_PXSIG_PMP

◆ AHCI_PXSSTS_DET_MASK

◆ AHCI_PXSSTS_DET_NO_DEVICE

◆ AHCI_PXSSTS_DET_PHY_NOT_READY

◆ AHCI_PXSSTS_DET_PHY_OFFLINE

◆ AHCI_PXSSTS_DET_PHY_OK

◆ AHCI_PXSSTS_IPM_ACTIVE

◆ AHCI_PXSSTS_IPM_DEVSLEEP

◆ AHCI_PXSSTS_IPM_MASK

◆ AHCI_PXSSTS_IPM_NO_DEVICE

◆ AHCI_PXSSTS_IPM_PARTIAL

◆ AHCI_PXSSTS_IPM_SLUMBER

◆ AHCI_PXSSTS_SPD_MASK

◆ AHCI_PXSSTS_SPD_SATA1

◆ AHCI_PXSSTS_SPD_SATA2

◆ AHCI_PXSSTS_SPD_SATA3

◆ AHCI_PXSSTS_SPD_UNKNOWN

◆ AHCI_PXTFD_ERROR_MASK

◆ AHCI_PXTFD_ERROR_SHIFT

◆ AHCI_PXTFD_STATUS_MASK

◆ AHCI_RECEIVED_FIS_ALIGNMENT

◆ AHCI_RECEIVED_FIS_FBS_ALIGNMENT

◆ AHCI_VERSION_0_95

◆ AHCI_VERSION_1_0

◆ AHCI_VERSION_1_2

◆ AHCI_VERSION_1_3_0

◆ AHCI_VERSION_1_3_1

◆ IDE_COMMAND_READ_PORT_MULTIPLIER

◆ IDE_COMMAND_WRITE_PORT_MULTIPLIER

◆ PMP_NUMBER

◆ UPDATE_COMMAND

Typedef Documentation

◆ AHCI_COMMAND_HEADER

◆ AHCI_COMMAND_LIST

◆ AHCI_COMMAND_TABLE

◆ AHCI_FIS_DEVICE_TO_HOST

◆ AHCI_FIS_HOST_TO_DEVICE

◆ AHCI_FIS_PIO_SETUP

◆ AHCI_FIS_SET_DEVICE_BITS

◆ AHCI_HOST_BUS_ADAPTER_REGISTER

◆ AHCI_PORT_MULTIPLIER_REGISTER

Port Multiplier Registers

◆ AHCI_PORT_REGISTER

◆ AHCI_PRD_TABLE_ENTRY

◆ AHCI_RECEIVED_FIS

◆ PAHCI_COMMAND_HEADER

| typedef struct _AHCI_COMMAND_HEADER * PAHCI_COMMAND_HEADER |

◆ PAHCI_COMMAND_LIST

| typedef struct _AHCI_COMMAND_LIST * PAHCI_COMMAND_LIST |

◆ PAHCI_COMMAND_TABLE

| typedef struct _AHCI_COMMAND_TABLE * PAHCI_COMMAND_TABLE |

◆ PAHCI_FIS_DEVICE_TO_HOST

◆ PAHCI_FIS_HOST_TO_DEVICE

◆ PAHCI_FIS_PIO_SETUP

| typedef struct _AHCI_FIS_PIO_SETUP * PAHCI_FIS_PIO_SETUP |

◆ PAHCI_FIS_SET_DEVICE_BITS

◆ PAHCI_PRD_TABLE_ENTRY

| typedef struct _AHCI_PRD_TABLE_ENTRY * PAHCI_PRD_TABLE_ENTRY |

◆ PAHCI_RECEIVED_FIS

| typedef struct _AHCI_RECEIVED_FIS * PAHCI_RECEIVED_FIS |

◆ SATA_SCR_REGISTER

| typedef enum _SATA_SCR_REGISTER SATA_SCR_REGISTER |

Enumeration Type Documentation

◆ _AHCI_HOST_BUS_ADAPTER_REGISTER

Definition at line 81 of file ahci.h.

◆ _AHCI_PORT_MULTIPLIER_REGISTER

Port Multiplier Registers

| Enumerator | |

|---|---|

| PmpProductId | |

| PmpRevisionInfo | |

| PmpPortInfo | |

| PmpErrorInfo | |

| PmpErrorControl | |

| PmpPhyEventCounterControl | |

| PmpCapabilities | |

| PmpFeaturesEnabled | |

Definition at line 65 of file ahci.h.

◆ _AHCI_PORT_REGISTER

Definition at line 96 of file ahci.h.

◆ _SATA_SCR_REGISTER

| Enumerator | |

|---|---|

| ATA_SSTATUS | |

| ATA_SERROR | |

| ATA_SCONTROL | |

| ATA_SACTIVE | |

| ATA_SNOTIFICATION | |

Definition at line 51 of file ahci.h.

Function Documentation

◆ AHCI_HBA_READ()

| FORCEINLINE ULONG AHCI_HBA_READ | ( | _In_ PVOID | HbaIoBase, |

| _In_ AHCI_HOST_BUS_ADAPTER_REGISTER | Register | ||

| ) |

Definition at line 529 of file ahci.h.

Referenced by AhciGetControllerProperties(), AtaAhciHbaIsr(), AtaAhciHbaRequestOsOwnership(), AtaAhciHbaStart(), AtaAhciHbaStop(), and AtaAhciIsHbaHotRemoved().

◆ AHCI_HBA_WRITE()

| FORCEINLINE VOID AHCI_HBA_WRITE | ( | _In_ PVOID | HbaIoBase, |

| _In_ AHCI_HOST_BUS_ADAPTER_REGISTER | Register, | ||

| _In_ ULONG | Value | ||

| ) |

Definition at line 538 of file ahci.h.

Referenced by AhciGetControllerProperties(), AtaAhciEnableInterrupts(), AtaAhciHbaIsr(), AtaAhciHbaRequestOsOwnership(), AtaAhciHbaStart(), AtaAhciHbaStop(), and AtaAhciPostRequestPolled().

◆ AHCI_PORT_READ()

| FORCEINLINE ULONG AHCI_PORT_READ | ( | _In_ PVOID | PortIoBase, |

| _In_ AHCI_PORT_REGISTER | Register | ||

| ) |

Definition at line 548 of file ahci.h.

Referenced by AtaAhciAtapiLedControl(), AtaAhciCreateChannelData(), AtaAhciDowngradeInterfaceSpeed(), AtaAhciEnterIdleState(), AtaAhciFbsControl(), AtaAhciHandleFatalError(), AtaAhciHandlePortStateChange(), AtaAhciIdentifyDevice(), AtaAhciPerformCommandListOverride(), AtaAhciPhyCheckConnection(), AtaAhciPhyCheckDevicePresence(), AtaAhciPhyEnterListenMode(), AtaAhciPmpDetect(), AtaAhciPollRegister(), AtaAhciPortHandleInterrupt(), AtaAhciPostRequestPolled(), AtaAhciSaveTaskFile(), AtaAhciSendComReset(), AtaAhciSpinUp(), AtaAhciStartCommandListProcess(), AtaAhciStartFisReceiveProcess(), AtaAhciStartFisReceiveProcessAndWait(), AtaAhciStopCommandListProcess(), AtaAhciStopFisReceiveProcess(), AtaAhciWaitForDeviceReady(), and AtaCtrlAbortChannel().

◆ AHCI_PORT_WRITE()

| FORCEINLINE VOID AHCI_PORT_WRITE | ( | _In_ PVOID | PortIoBase, |

| _In_ AHCI_PORT_REGISTER | Register, | ||

| _In_ ULONG | Value | ||

| ) |

Definition at line 557 of file ahci.h.

Referenced by AtaAhciAtapiLedControl(), AtaAhciCreateChannelData(), AtaAhciDowngradeInterfaceSpeed(), AtaAhciEnableInterrupts(), AtaAhciFbsControl(), AtaAhciHandleFatalError(), AtaAhciPerformCommandListOverride(), AtaAhciPhyCheckConnection(), AtaAhciPhyEnterListenMode(), AtaAhciPmpDetect(), AtaAhciPortHandleInterrupt(), AtaAhciPostRequestPolled(), AtaAhciSendComReset(), AtaAhciSetupDmaMemoryAddress(), AtaAhciSpinUp(), AtaAhciStartCommandListProcess(), AtaAhciStartFisReceiveProcess(), AtaAhciStartIo(), AtaAhciStopCommandListProcess(), AtaAhciStopFisReceiveProcess(), and AtaAhciWaitForDeviceReady().

◆ C_ASSERT() [1/8]

| C_ASSERT | ( | FIELD_OFFSET(AHCI_COMMAND_TABLE, PrdTable) | = =128 | ) |

◆ C_ASSERT() [2/8]

| C_ASSERT | ( | sizeof(AHCI_COMMAND_HEADER) | = =32 | ) |

◆ C_ASSERT() [3/8]

| C_ASSERT | ( | sizeof(AHCI_FIS_DEVICE_TO_HOST) | = =20 | ) |

◆ C_ASSERT() [4/8]

| C_ASSERT | ( | sizeof(AHCI_FIS_HOST_TO_DEVICE) | = =20 | ) |

◆ C_ASSERT() [5/8]

| C_ASSERT | ( | sizeof(AHCI_FIS_PIO_SETUP) | = =20 | ) |

◆ C_ASSERT() [6/8]

| C_ASSERT | ( | sizeof(AHCI_FIS_SET_DEVICE_BITS) | = =8 | ) |

◆ C_ASSERT() [7/8]

| C_ASSERT | ( | sizeof(AHCI_PRD_TABLE_ENTRY) | = =16 | ) |

◆ C_ASSERT() [8/8]

| C_ASSERT | ( | sizeof(AHCI_RECEIVED_FIS) | = =256 | ) |