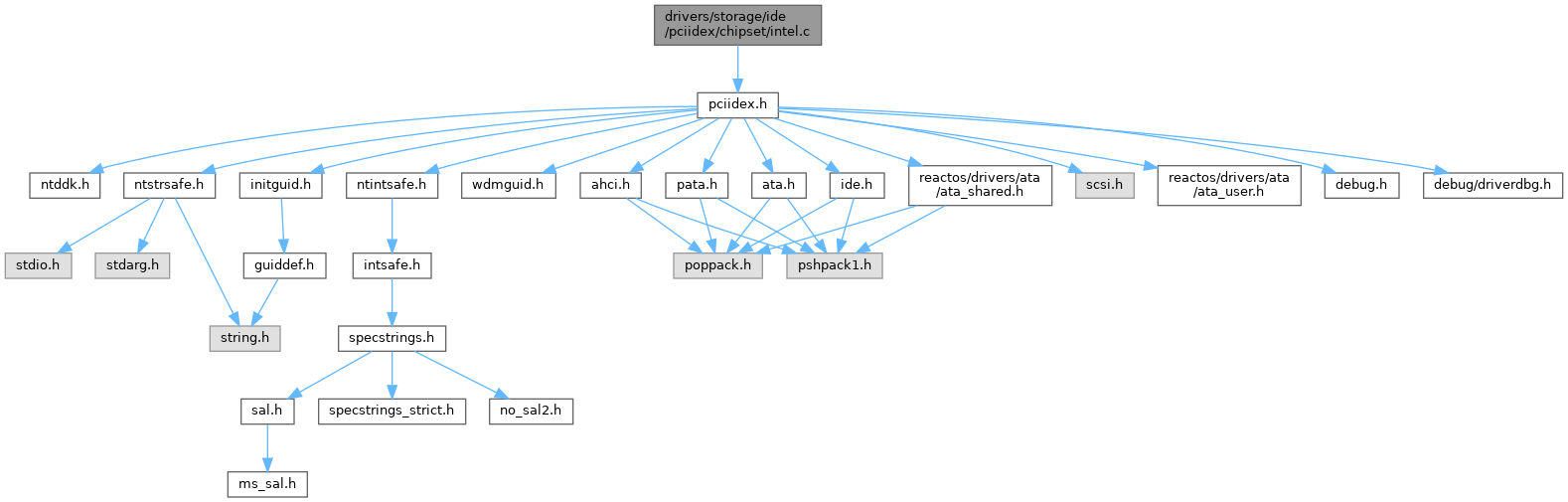

#include "pciidex.h"

Go to the source code of this file.

Classes | |

| struct | _INTEL_CONTROLLER_INFO |

| struct | _INTEL_HW_EXTENSION |

Typedefs | |

| typedef struct _INTEL_CONTROLLER_INFO | INTEL_CONTROLLER_INFO |

| typedef struct _INTEL_CONTROLLER_INFO * | PINTEL_CONTROLLER_INFO |

| typedef struct _INTEL_HW_EXTENSION | INTEL_HW_EXTENSION |

| typedef struct _INTEL_HW_EXTENSION * | PINTEL_HW_EXTENSION |

Variables | |

| static PCIIDEX_PAGED_DATA const INTEL_CONTROLLER_INFO | IntelControllerList [] |

| static PCIIDEX_PAGED_DATA const ATA_PCI_ENABLE_BITS | IntelPiixEnableBits [MAX_IDE_CHANNEL] |

| static PCIIDEX_PAGED_DATA const ATA_PCI_ENABLE_BITS | IntelMpiixEnableBits [MAX_IDE_CHANNEL] |

| static const UCHAR | IntelClockSettings [5][2] |

| static const ULONG | IntelTimingModeToCycleTime [5] |

| static const UCHAR | IntelModeSettings [] |

| static const UCHAR | IntelUdmaSettings [] |

| static const ULONG | IntelDmaModeToTimingMode [] |

Macro Definition Documentation

◆ BRIDGE_450KX_REV_B0

◆ BRIDGE_450NX_REV_B0

◆ BRIDGE_450NX_REV_B1

◆ BRIDGE_450NX_REV_C0

◆ HW_FLAGS_DISABLE_DMA

◆ HW_FLAGS_HAS_CFG_REG

◆ HW_FLAGS_HAS_UDMA_REG

◆ HW_FLAGS_TYPE_MASK

◆ MPIIX_REG_IDETIM

◆ PCI_DEV_ATOM_C2000_1

◆ PCI_DEV_ATOM_C2000_2

◆ PCI_DEV_ATOM_C2000_3

◆ PCI_DEV_ATOM_C2000_4

◆ PCI_DEV_ATOM_E3800_1

◆ PCI_DEV_ATOM_E3800_2

◆ PCI_DEV_BRIDGE_450KX

◆ PCI_DEV_BRIDGE_450NX

◆ PCI_DEV_C_ICH_82801E

◆ PCI_DEV_EP80579

◆ PCI_DEV_ESB2_63XXESB

◆ PCI_DEV_ICH0_82801AB

◆ PCI_DEV_ICH10_82801JD_1

◆ PCI_DEV_ICH10_82801JD_2

◆ PCI_DEV_ICH10_82801JI_1

◆ PCI_DEV_ICH10_82801JI_2

◆ PCI_DEV_ICH2_82801BA

◆ PCI_DEV_ICH2_82801BAM

◆ PCI_DEV_ICH3_M_82801CAM

◆ PCI_DEV_ICH3_S_82801CA

◆ PCI_DEV_ICH4_82801DB

◆ PCI_DEV_ICH4_L_82801DBL

◆ PCI_DEV_ICH4_M_82801DBM

◆ PCI_DEV_ICH5_6300ESB_IDE

◆ PCI_DEV_ICH5_6300ESB_RAID

◆ PCI_DEV_ICH5_6300ESB_SATA

◆ PCI_DEV_ICH5_82801EB_IDE

◆ PCI_DEV_ICH5_82801EB_SATA

◆ PCI_DEV_ICH5_R_82801ER

◆ PCI_DEV_ICH6_82801FB_IDE

◆ PCI_DEV_ICH6_82801FB_SATA

◆ PCI_DEV_ICH6_M_82801FBM

◆ PCI_DEV_ICH6_R_82801FB

◆ PCI_DEV_ICH7_6321ESB

◆ PCI_DEV_ICH7_82801G

◆ PCI_DEV_ICH7_82801GB

◆ PCI_DEV_ICH7_M_82801GBM

◆ PCI_DEV_ICH8_82801H

◆ PCI_DEV_ICH8_M_82801HBM

◆ PCI_DEV_ICH8_M_82801HM

◆ PCI_DEV_ICH8_R_82801HR

◆ PCI_DEV_ICH9_82801I

◆ PCI_DEV_ICH9_M_82801IBM_1

◆ PCI_DEV_ICH9_M_82801IBM_2

◆ PCI_DEV_ICH9_M_82801IBM_3

◆ PCI_DEV_ICH9_R_82801IR_1

◆ PCI_DEV_ICH9_R_82801IR_2

◆ PCI_DEV_ICH_82801AA

◆ PCI_DEV_MPIIX_82371MX

◆ PCI_DEV_PCH_5SERIES_1

◆ PCI_DEV_PCH_5SERIES_2

◆ PCI_DEV_PCH_5SERIES_3

◆ PCI_DEV_PCH_5SERIES_4

◆ PCI_DEV_PCH_5SERIES_5

◆ PCI_DEV_PCH_5SERIES_6

◆ PCI_DEV_PCH_6SERIES_1

◆ PCI_DEV_PCH_6SERIES_2

◆ PCI_DEV_PCH_6SERIES_3

◆ PCI_DEV_PCH_6SERIES_4

◆ PCI_DEV_PCH_7SERIES_1

◆ PCI_DEV_PCH_7SERIES_2

◆ PCI_DEV_PCH_7SERIES_3

◆ PCI_DEV_PCH_7SERIES_4

◆ PCI_DEV_PCH_8900_1

◆ PCI_DEV_PCH_8900_2

◆ PCI_DEV_PCH_8SERIES_1

◆ PCI_DEV_PCH_8SERIES_2

◆ PCI_DEV_PCH_8SERIES_3

◆ PCI_DEV_PCH_8SERIES_4

◆ PCI_DEV_PCH_8SERIES_5

◆ PCI_DEV_PCH_8SERIES_6

◆ PCI_DEV_PCH_8SERIES_7

◆ PCI_DEV_PCH_8SERIES_8

◆ PCI_DEV_PCH_9SERIES_1

◆ PCI_DEV_PCH_9SERIES_2

◆ PCI_DEV_PCH_9SERIES_3

◆ PCI_DEV_PCH_9SERIES_4

◆ PCI_DEV_PCH_X79_1

◆ PCI_DEV_PCH_X79_2

◆ PCI_DEV_PCH_X99_1

◆ PCI_DEV_PCH_X99_2

◆ PCI_DEV_PCH_X99_3

◆ PCI_DEV_PCH_X99_4

◆ PCI_DEV_PIIX3_82371SB

◆ PCI_DEV_PIIX4_82371AB

◆ PCI_DEV_PIIX4E_82372FB

◆ PCI_DEV_PIIX4E_82443MX

◆ PCI_DEV_PIIX4E_82451NX

◆ PCI_DEV_PIIX_82371FB

◆ PCI_DEV_SCH_ATOM_Z5XX

◆ PIIX_CONFIG_CLOCK_UDMA100

◆ PIIX_CONFIG_CLOCK_UDMA66

◆ PIIX_CONFIG_CR

◆ PIIX_CONFIG_KEEP_MASK

◆ PIIX_CONFIG_WR_PING_PONG

◆ PIIX_IDETIM_DTE

◆ PIIX_IDETIM_IDE

◆ PIIX_IDETIM_IE

◆ PIIX_IDETIM_ISP

◆ PIIX_IDETIM_ISP_MASK

◆ PIIX_IDETIM_PPE

◆ PIIX_IDETIM_RCT

◆ PIIX_IDETIM_RCT_MASK

◆ PIIX_IDETIM_RSV_MASK

◆ PIIX_IDETIM_SECONDARY

◆ PIIX_IDETIM_SETTINGS

◆ PIIX_IDETIM_SITRE

◆ PIIX_IDETIM_TIME

◆ PIIX_REG_CONFIG

◆ PIIX_REG_IDETIM

◆ PIIX_REG_SIDETIM

◆ PIIX_REG_UDMACTL

◆ PIIX_REG_UDMATIM

◆ PIIX_SIDETIM_ISP

◆ PIIX_SIDETIM_ISPRCT_MASK

◆ PIIX_SIDETIM_RCT

◆ PIIX_UDMACTL_EN

◆ PIIX_UDMACTL_EN_MASK

◆ PIIX_UDMATIM_CT

◆ PIIX_UDMATIM_CT_MASK

◆ PXB_CONFIG_BUF_RESTREAM

◆ PXB_CONFIG_PCI_BUS_LOCK

◆ PXB_REG_CONFIG

◆ SCH_DTIM_MDM

◆ SCH_DTIM_MDM_MASK

◆ SCH_DTIM_PM

◆ SCH_DTIM_PM_MASK

◆ SCH_DTIM_PPE

◆ SCH_DTIM_UDM

◆ SCH_DTIM_UDM_MASK

◆ SCH_DTIM_USD

◆ SCH_REG_DTIM

◆ TYPE_ICH

| #define TYPE_ICH (4 | HW_FLAGS_HAS_UDMA_REG | HW_FLAGS_HAS_CFG_REG) |

◆ TYPE_MPIIX

◆ TYPE_PIIX

◆ TYPE_PIIX3

◆ TYPE_PIIX4

| #define TYPE_PIIX4 (3 | HW_FLAGS_HAS_UDMA_REG) |

◆ TYPE_SATA

◆ TYPE_SCH

Typedef Documentation

◆ INTEL_CONTROLLER_INFO

◆ INTEL_HW_EXTENSION

◆ PINTEL_CONTROLLER_INFO

◆ PINTEL_HW_EXTENSION

| typedef struct _INTEL_HW_EXTENSION * PINTEL_HW_EXTENSION |

Function Documentation

◆ IntelGetControllerProperties()

| NTSTATUS IntelGetControllerProperties | ( | _Inout_ PATA_CONTROLLER | Controller | ) |

Definition at line 969 of file intel.c.

Referenced by PciIdeGetControllerProperties().

◆ IntelInitChannel()

|

static |

Definition at line 836 of file intel.c.

Referenced by IntelGetControllerProperties().

◆ IntelPciBridgeErrataMatch()

|

static |

Definition at line 772 of file intel.c.

Referenced by IntelGetControllerProperties().

◆ IntelPiixChooseDeviceSpeed()

|

static |

Definition at line 433 of file intel.c.

Referenced by IntelPiixLegacySetTransferMode(), and IntelPiixSetTransferMode().

◆ IntelPiixLegacyComputeIdeTiming()

|

static |

◆ IntelPiixLegacyPrepareIo()

|

static |

Definition at line 662 of file intel.c.

Referenced by IntelInitChannel().

◆ IntelPiixLegacySetTransferMode()

|

static |

Definition at line 729 of file intel.c.

Referenced by IntelInitChannel().

◆ IntelPiixSetTransferMode()

|

static |

Definition at line 488 of file intel.c.

Referenced by IntelInitChannel().

◆ IntelSchSetTransferMode()

|

static |

Definition at line 622 of file intel.c.

Referenced by IntelInitChannel().

Variable Documentation

◆ IntelClockSettings

Definition at line 379 of file intel.c.

Referenced by IntelPiixLegacyComputeIdeTiming(), and IntelPiixSetTransferMode().

◆ IntelControllerList

|

static |

Definition at line 273 of file intel.c.

Referenced by IntelGetControllerProperties().

◆ IntelDmaModeToTimingMode

Definition at line 418 of file intel.c.

Referenced by IntelPiixChooseDeviceSpeed(), IntelPiixLegacyComputeIdeTiming(), and IntelPiixSetTransferMode().

◆ IntelModeSettings

Definition at line 399 of file intel.c.

Referenced by IntelPiixLegacyComputeIdeTiming(), and IntelPiixSetTransferMode().

◆ IntelMpiixEnableBits

|

static |

Definition at line 373 of file intel.c.

Referenced by IntelGetControllerProperties().

◆ IntelPiixEnableBits

|

static |

Definition at line 366 of file intel.c.

Referenced by IntelGetControllerProperties().

◆ IntelTimingModeToCycleTime

- See also

- IntelClockSettings

Definition at line 390 of file intel.c.

Referenced by IntelPiixChooseDeviceSpeed().

◆ IntelUdmaSettings

Definition at line 408 of file intel.c.

Referenced by IntelPiixSetTransferMode().