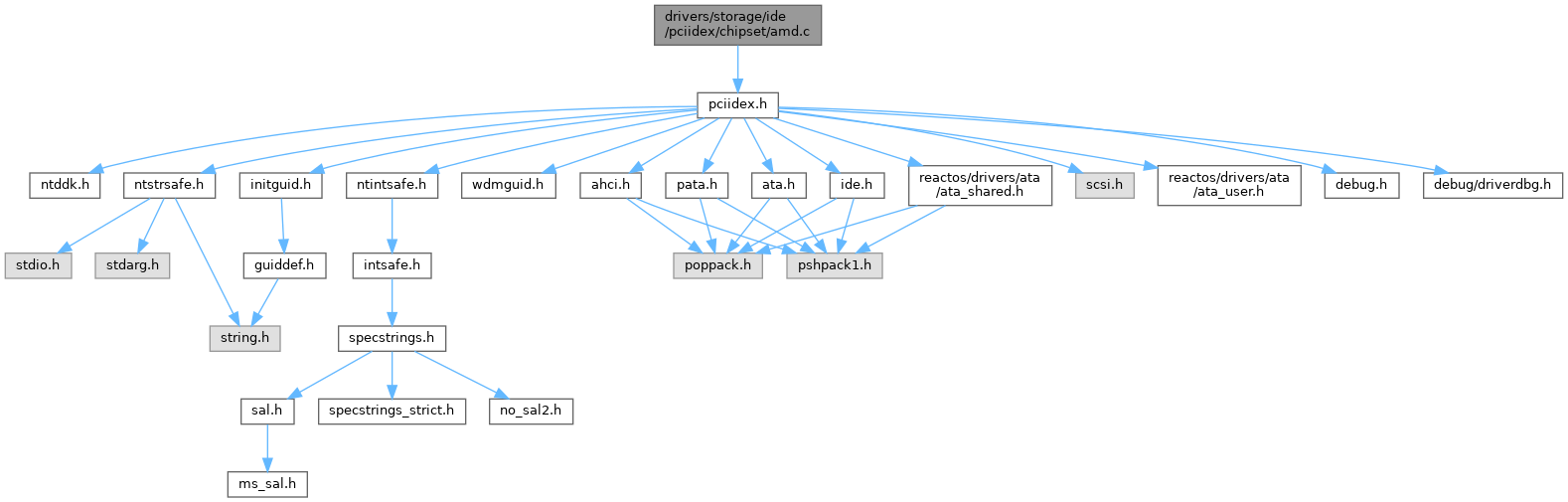

#include "pciidex.h"

Go to the source code of this file.

Functions | |

| static ULONG | AmdGetPciConfigIoBase (_In_ PATA_CONTROLLER Controller) |

| static VOID | AmdEnablePostedWriteBuffer (_In_ PATA_CONTROLLER Controller, _In_ PCHANNEL_DATA_PATA ChanData, _In_ ULONG Channel, _In_reads_(MAX_IDE_DEVICE) PCHANNEL_DEVICE_CONFIG *DeviceList, _In_ ULONG IoBase) |

| static VOID | AmdSetTransferMode (_In_ PATA_CONTROLLER Controller, _In_ ULONG Channel, _In_reads_(MAX_IDE_DEVICE) PCHANNEL_DEVICE_CONFIG *DeviceList) |

| static VOID | AmdControllerStart (_In_ PATA_CONTROLLER Controller) |

| static BOOLEAN | NvHasUdmaCable (_In_ USHORT UdmaTimReg, _In_ ULONG Drive) |

| NTSTATUS | AmdGetControllerProperties (_Inout_ PATA_CONTROLLER Controller) |

Variables | |

| struct { | |

| USHORT VendorID | |

| USHORT DeviceID | |

| USHORT Flags | |

| } | AmdControllerList [] |

| static const UCHAR | AmdUdmaSettings [] |

| static const ULONG | AmdTimingControlShift [MAX_IDE_CHANNEL][MAX_IDE_DEVICE] |

| static const ULONG | AmdAddressSetupShift [MAX_IDE_CHANNEL][MAX_IDE_DEVICE] |

| static const ULONG | AmdPortTimShift [MAX_IDE_CHANNEL] |

| static PCIIDEX_PAGED_DATA const ATA_PCI_ENABLE_BITS | AmdEnableBits [MAX_IDE_CHANNEL] |

| static PCIIDEX_PAGED_DATA const ATA_PCI_ENABLE_BITS | NvEnableBits [MAX_IDE_CHANNEL] |

Macro Definition Documentation

◆ AMD_CONFIG_BASE

◆ AMD_CONFIG_CR

◆ AMD_CONFIG_PREFETCH

◆ AMD_PCI_CLOCK

◆ AMD_REG_ADDRESS_SETUP

◆ AMD_REG_CONFIG_CR

◆ AMD_REG_CONFIG_PREFETCH

◆ AMD_REG_TIMING_CTRL

◆ AMD_REG_UDMA

◆ AMD_UDMA_CTRL

◆ AMD_UDMA_EN

◆ AMD_UDMA_TIME

◆ HW_FLAGS_CHECK_SYSBOARD

◆ HW_FLAGS_NO_PREFETCH

◆ HW_FLAGS_SATA

◆ HW_FLAGS_UDMA4

◆ HW_FLAGS_UDMA5

◆ NV_CONFIG_BASE

◆ PCI_DEV_AMD_756

◆ PCI_DEV_AMD_766

◆ PCI_DEV_AMD_768

◆ PCI_DEV_AMD_8111

◆ PCI_DEV_AMD_CS5536

◆ PCI_DEV_AMD_CS5536_2

◆ PCI_DEV_CK804_IDE

◆ PCI_DEV_CK804_SATA

◆ PCI_DEV_CK804_SATA_2

◆ PCI_DEV_MCP04_IDE

◆ PCI_DEV_MCP04_SATA

◆ PCI_DEV_MCP04_SATA_2

◆ PCI_DEV_MCP51_IDE

◆ PCI_DEV_MCP51_SATA

◆ PCI_DEV_MCP51_SATA_2

◆ PCI_DEV_MCP55_IDE

◆ PCI_DEV_MCP55_SATA

◆ PCI_DEV_MCP55_SATA_2

◆ PCI_DEV_MCP61_IDE

◆ PCI_DEV_MCP61_SATA

◆ PCI_DEV_MCP61_SATA_2

◆ PCI_DEV_MCP61_SATA_3

◆ PCI_DEV_MCP65_IDE

◆ PCI_DEV_MCP67_IDE

◆ PCI_DEV_MCP73_IDE

◆ PCI_DEV_MCP77_IDE

◆ PCI_DEV_MCP89_SATA

◆ PCI_DEV_NFORCE2_IDE

◆ PCI_DEV_NFORCE2_IDE_2

◆ PCI_DEV_NFORCE2_SATA

◆ PCI_DEV_NFORCE3_IDE

◆ PCI_DEV_NFORCE3_IDE_2

◆ PCI_DEV_NFORCE3_SATA

◆ PCI_DEV_NFORCE3_SATA_2

◆ PCI_DEV_NFORCE_IDE

◆ PCI_SUBSYSTEM_AMD_SERENADE

Function Documentation

◆ AmdControllerStart()

|

static |

Definition at line 297 of file amd.c.

Referenced by AmdGetControllerProperties().

◆ AmdEnablePostedWriteBuffer()

|

static |

Definition at line 181 of file amd.c.

Referenced by AmdSetTransferMode().

◆ AmdGetControllerProperties()

| NTSTATUS AmdGetControllerProperties | ( | _Inout_ PATA_CONTROLLER | Controller | ) |

Definition at line 329 of file amd.c.

Referenced by PciIdeGetControllerProperties().

◆ AmdGetPciConfigIoBase()

|

static |

◆ AmdSetTransferMode()

|

static |

Definition at line 217 of file amd.c.

Referenced by AmdGetControllerProperties().

◆ NvHasUdmaCable()

Definition at line 313 of file amd.c.

Referenced by AmdGetControllerProperties().

Variable Documentation

◆ AmdAddressSetupShift

|

static |

Definition at line 140 of file amd.c.

Referenced by AmdSetTransferMode().

◆

| PCIIDEX_PAGED_DATA const struct { ... } AmdControllerList[] |

Referenced by AmdGetControllerProperties().

◆ AmdEnableBits

|

static |

Definition at line 153 of file amd.c.

Referenced by AmdGetControllerProperties().

◆ AmdPortTimShift

|

static |

Definition at line 146 of file amd.c.

Referenced by AmdSetTransferMode().

◆ AmdTimingControlShift

|

static |

Definition at line 134 of file amd.c.

Referenced by AmdSetTransferMode().

◆ AmdUdmaSettings

Definition at line 123 of file amd.c.

Referenced by AmdSetTransferMode().

◆ DeviceID

◆ Flags

◆ NvEnableBits

|

static |

Definition at line 160 of file amd.c.

Referenced by AmdGetControllerProperties().