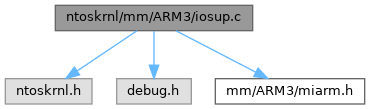

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

| #define | MODULE_INVOLVED_IN_ARM3 |

Variables | |

| MI_PFN_CACHE_ATTRIBUTE | MiPlatformCacheAttributes [2][MmMaximumCacheType] |

Macro Definition Documentation

◆ MODULE_INVOLVED_IN_ARM3

◆ NDEBUG

Function Documentation

◆ MmIsIoSpaceActive()

◆ MmMapIoSpace()

| PVOID NTAPI MmMapIoSpace | ( | IN PHYSICAL_ADDRESS | PhysicalAddress, |

| IN SIZE_T | NumberOfBytes, | ||

| IN MEMORY_CACHING_TYPE | CacheType | ||

| ) |

Definition at line 47 of file iosup.c.

Referenced by AcpiOsMapMemory(), AtaCtrlPciMapBar(), AtaLegacyTranslateBusAddress(), ConfigCallback(), Fdo_EvtDevicePrepareHardware(), HalpAcpiGetTableFromBios(), HalpAcpiTableCacheInit(), IntVideoPortMapMemory(), MiFindContiguousMemory(), MmMapVideoDisplay(), NdisMMapIoSpace(), NdisMRegisterIoPortRange(), OutTableData(), PciGetAcpiTable(), RamdiskMapPages(), ScrResetScreen(), ScrSetFont(), ScsiPortGetDeviceBase(), StorPortGetDeviceBase(), StreamClassStartDevice(), TestPhysicalMemorySection(), USBPORT_ParseResources(), and VidInitialize().

◆ MmMapVideoDisplay()

| PVOID NTAPI MmMapVideoDisplay | ( | IN PHYSICAL_ADDRESS | PhysicalAddress, |

| IN SIZE_T | NumberOfBytes, | ||

| IN MEMORY_CACHING_TYPE | CacheType | ||

| ) |

Definition at line 243 of file iosup.c.

◆ MmUnmapIoSpace()

Definition at line 193 of file iosup.c.

Referenced by AcpiOsUnmapMemory(), AtaLegacyDetectChannel(), Fdo_EvtDeviceReleaseHardware(), FdoRemoveAdapter(), HalpAcpiGetTable(), HalpAcpiGetTableFromBios(), HalpAcpiTableCacheInit(), IntVideoPortUnmapMemory(), MiFreeContiguousMemory(), MmUnmapVideoDisplay(), NdisMDeregisterIoPortRange(), NdisMUnmapIoSpace(), OutTableData(), PciGetAcpiTable(), PciIdeXFdoFreeResources(), RamdiskUnmapPages(), ScrResetScreen(), ScrSetFont(), ScsiPortFreeDeviceBase(), StreamClassReleaseResources(), StreamClassStartDevice(), TestPhysicalMemorySection(), and VidInitialize().

◆ MmUnmapVideoDisplay()

Definition at line 260 of file iosup.c.

Variable Documentation

◆ MiPlatformCacheAttributes

| MI_PFN_CACHE_ATTRIBUTE MiPlatformCacheAttributes[2][MmMaximumCacheType] |

Definition at line 27 of file iosup.c.

Referenced by MiAllocateContiguousMemory(), MiMapLockedPagesInUserSpace(), MmAllocateNonCachedMemory(), MmAllocatePagesForMdlEx(), MmMapIoSpace(), MmMapLockedPagesSpecifyCache(), and MmMapLockedPagesWithReservedMapping().