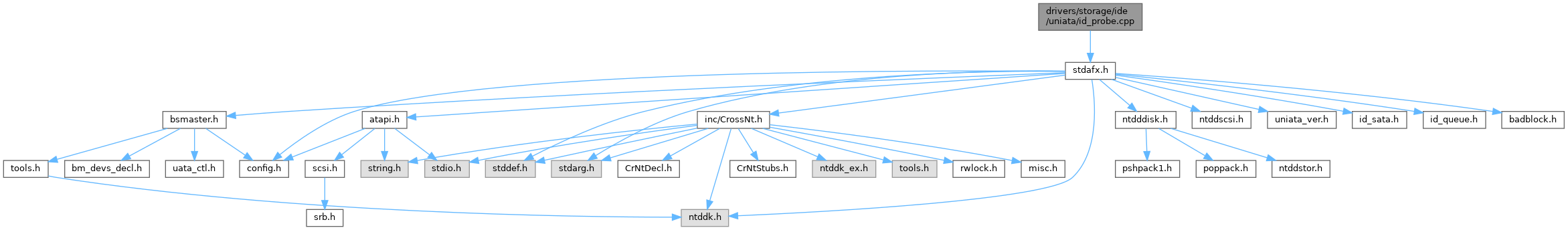

#include "stdafx.h"

Go to the source code of this file.

Variables | |

| PBUSMASTER_CONTROLLER_INFORMATION | BMList = NULL |

| ULONG | BMListLen = 0 |

| ULONG | IsaCount = 0 |

| ULONG | MCACount = 0 |

| BOOLEAN | FirstMasterOk = FALSE |

| BOOLEAN | AtdiskPrimaryClaimed = FALSE |

| BOOLEAN | AtdiskSecondaryClaimed = FALSE |

| UCHAR | pciBuffer [256] |

| ULONG | maxPciBus = 16 |

| PDRIVER_OBJECT | SavedDriverObject = NULL |

| static CONST ULONG | StdIsaPorts [] = {IO_WD1, IO_WD1 + ATA_ALTOFFSET, IO_WD2, IO_WD2 + ATA_ALTOFFSET, 0, 0} |

Function Documentation

◆ AtapiCheckIOInterference()

| BOOLEAN NTAPI AtapiCheckIOInterference | ( | IN PPORT_CONFIGURATION_INFORMATION | ConfigInfo, |

| ULONG | portBase | ||

| ) |

Definition at line 2203 of file id_probe.cpp.

Referenced by AtapiFindIsaController().

◆ AtapiDoNothing()

Definition at line 86 of file id_probe.cpp.

◆ AtapiFindDev()

| ULONG NTAPI AtapiFindDev | ( | IN PVOID | HwDeviceExtension, |

| IN BUS_DATA_TYPE | BusDataType, | ||

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber, | ||

| IN ULONG | dev_id, | ||

| IN ULONG | RevID | ||

| ) |

Definition at line 871 of file id_probe.cpp.

◆ AtapiFindIsaController()

| ULONG NTAPI AtapiFindIsaController | ( | IN PVOID | HwDeviceExtension, |

| IN PVOID | Context, | ||

| IN PVOID | BusInformation, | ||

| IN PCHAR | ArgumentString, | ||

| IN OUT PPORT_CONFIGURATION_INFORMATION | ConfigInfo, | ||

| OUT PBOOLEAN | Again | ||

| ) |

Definition at line 2243 of file id_probe.cpp.

Referenced by DriverEntry().

◆ AtapiFindListedDev()

| ULONG NTAPI AtapiFindListedDev | ( | IN PBUSMASTER_CONTROLLER_INFORMATION_BASE | BusMasterAdapters, |

| IN ULONG | lim, | ||

| IN PVOID | HwDeviceExtension, | ||

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber, | ||

| OUT PCI_SLOT_NUMBER * | _slotData | ||

| ) |

Definition at line 780 of file id_probe.cpp.

◆ AtapiGetIoRange()

| ULONGIO_PTR NTAPI AtapiGetIoRange | ( | IN PVOID | HwDeviceExtension, |

| IN PPORT_CONFIGURATION_INFORMATION | ConfigInfo, | ||

| IN PPCI_COMMON_CONFIG | pciData, | ||

| IN ULONG | SystemIoBusNumber, | ||

| IN ULONG | rid, | ||

| IN ULONG | offset, | ||

| IN ULONG | length | ||

| ) |

Definition at line 153 of file id_probe.cpp.

Referenced by UniataAhciDetect(), UniataChipDetect(), and UniataFindBusMasterController().

◆ AtapiReadArgumentString()

| ULONG NTAPI AtapiReadArgumentString | ( | IN PVOID | HwDeviceExtension, |

| IN PVOID | Context, | ||

| IN PVOID | BusInformation, | ||

| IN PCHAR | ArgumentString, | ||

| IN OUT PPORT_CONFIGURATION_INFORMATION | ConfigInfo, | ||

| OUT PBOOLEAN | Again | ||

| ) |

Definition at line 2754 of file id_probe.cpp.

Referenced by DriverEntry().

◆ CheckDevice()

| ULONG NTAPI CheckDevice | ( | IN PVOID | HwDeviceExtension, |

| IN ULONG | lChannel, | ||

| IN ULONG | deviceNumber, | ||

| IN BOOLEAN | ResetDev | ||

| ) |

Definition at line 2897 of file id_probe.cpp.

Referenced by AtapiResetController__(), AtapiSendCommand(), AtapiStartIo__(), FindDevices(), IdeSendCommand(), and UniataSataEvent().

◆ FindDevices()

Definition at line 3184 of file id_probe.cpp.

◆ ScsiPortGetBusDataByOffset()

| ULONG NTAPI ScsiPortGetBusDataByOffset | ( | IN PVOID | HwDeviceExtension, |

| IN BUS_DATA_TYPE | BusDataType, | ||

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber, | ||

| IN PVOID | Buffer, | ||

| IN ULONG | Offset, | ||

| IN ULONG | Length | ||

| ) |

Definition at line 741 of file id_probe.cpp.

◆ UniataAnybodyHome()

| ULONG NTAPI UniataAnybodyHome | ( | IN PVOID | HwDeviceExtension, |

| IN ULONG | lChannel, | ||

| IN ULONG | deviceNumber | ||

| ) |

Definition at line 2778 of file id_probe.cpp.

Referenced by AtapiResetController__(), AtapiStartIo__(), CheckDevice(), and IdeSendCommand().

◆ UniataCheckPCISubclass()

Definition at line 256 of file id_probe.cpp.

Referenced by UniataEnumBusMasterController__(), and UniataFindBusMasterController().

◆ UniataClaimLegacyPCIIDE()

Definition at line 1939 of file id_probe.cpp.

Referenced by DriverEntry().

◆ UniataConnectIntr2()

ForceSimplex

Definition at line 2050 of file id_probe.cpp.

Referenced by AtapiAdapterControl().

◆ UniataDisconnectIntr2()

Definition at line 2172 of file id_probe.cpp.

Referenced by AtapiAdapterControl().

◆ UniataEnableIoPCI()

| USHORT NTAPI UniataEnableIoPCI | ( | IN ULONG | busNumber, |

| IN ULONG | slotNumber, | ||

| IN OUT PPCI_COMMON_CONFIG | pciData | ||

| ) |

Definition at line 95 of file id_probe.cpp.

Referenced by AtapiChipInit(), UniataEnumBusMasterController__(), and UniataFindBusMasterController().

◆ UniataEnumBusMasterController()

Definition at line 245 of file id_probe.cpp.

Referenced by DriverEntry().

◆ UniataEnumBusMasterController__()

Definition at line 299 of file id_probe.cpp.

Referenced by UniataEnumBusMasterController().

◆ UniataFindBusMasterController()

| ULONG NTAPI UniataFindBusMasterController | ( | IN PVOID | HwDeviceExtension, |

| IN PVOID | Context, | ||

| IN PVOID | BusInformation, | ||

| IN PCHAR | ArgumentString, | ||

| IN OUT PPORT_CONFIGURATION_INFORMATION | ConfigInfo, | ||

| OUT PBOOLEAN | Again | ||

| ) |

Definition at line 988 of file id_probe.cpp.

Referenced by DriverEntry(), UniataFindCompatBusMasterController1(), and UniataFindCompatBusMasterController2().

◆ UniataFindCompatBusMasterController1()

| ULONG NTAPI UniataFindCompatBusMasterController1 | ( | IN PVOID | HwDeviceExtension, |

| IN PVOID | Context, | ||

| IN PVOID | BusInformation, | ||

| IN PCHAR | ArgumentString, | ||

| IN OUT PPORT_CONFIGURATION_INFORMATION | ConfigInfo, | ||

| OUT PBOOLEAN | Again | ||

| ) |

Definition at line 924 of file id_probe.cpp.

Referenced by DriverEntry().

◆ UniataFindCompatBusMasterController2()

| ULONG NTAPI UniataFindCompatBusMasterController2 | ( | IN PVOID | HwDeviceExtension, |

| IN PVOID | Context, | ||

| IN PVOID | BusInformation, | ||

| IN PCHAR | ArgumentString, | ||

| IN OUT PPORT_CONFIGURATION_INFORMATION | ConfigInfo, | ||

| OUT PBOOLEAN | Again | ||

| ) |

Definition at line 945 of file id_probe.cpp.

Referenced by DriverEntry().

Variable Documentation

◆ AtdiskPrimaryClaimed

Definition at line 61 of file id_probe.cpp.

Referenced by AtapiCheckIOInterference(), and UniataFindBusMasterController().

◆ AtdiskSecondaryClaimed

Definition at line 62 of file id_probe.cpp.

Referenced by AtapiCheckIOInterference(), and UniataFindBusMasterController().

◆ BMList

| PBUSMASTER_CONTROLLER_INFORMATION BMList = NULL |

Definition at line 53 of file id_probe.cpp.

Referenced by AtapiAdapterControl(), AtapiHwInitialize(), AtapiInterrupt2(), AtapiStartIo__(), DriverEntry(), UniataChipDetectChannels(), UniataClaimLegacyPCIIDE(), UniataConnectIntr2(), UniataDisconnectIntr2(), UniataEnumBusMasterController__(), and UniataFindBusMasterController().

◆ BMListLen

| ULONG BMListLen = 0 |

Definition at line 54 of file id_probe.cpp.

Referenced by AtapiRegCheckDevValue(), DriverEntry(), UniataEnumBusMasterController__(), and UniataFindBusMasterController().

◆ FirstMasterOk

Definition at line 58 of file id_probe.cpp.

Referenced by UniataFindBusMasterController().

◆ IsaCount

| ULONG IsaCount = 0 |

Definition at line 55 of file id_probe.cpp.

Referenced by AtapiFindIsaController(), and AtapiRegCheckDevValue().

◆ maxPciBus

| ULONG maxPciBus = 16 |

Definition at line 67 of file id_probe.cpp.

Referenced by AtapiFindListedDev(), and UniataEnumBusMasterController__().

◆ MCACount

| ULONG MCACount = 0 |

Definition at line 56 of file id_probe.cpp.

Referenced by AtapiFindIsaController().

◆ pciBuffer

| UCHAR pciBuffer[256] |

Definition at line 66 of file id_probe.cpp.

Referenced by AtapiFindController(), and FindBrokenController().

◆ SavedDriverObject

| PDRIVER_OBJECT SavedDriverObject = NULL |

Definition at line 69 of file id_probe.cpp.

Referenced by DriverEntry(), UniataClaimLegacyPCIIDE(), and UniataConnectIntr2().

◆ StdIsaPorts

|

static |

Definition at line 291 of file id_probe.cpp.

Referenced by UniataEnumBusMasterController__().