actbl1.h File Reference

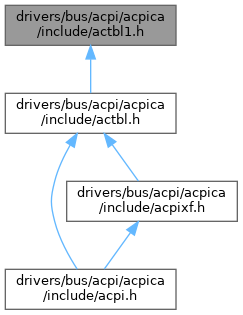

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macro Definition Documentation

◆ ACPI_ASF_SMBUS_PROTOCOLS

◆ ACPI_BERT_CORRECTABLE

◆ ACPI_BERT_ERROR_ENTRY_COUNT

◆ ACPI_BERT_MULTIPLE_CORRECTABLE

◆ ACPI_BERT_MULTIPLE_UNCORRECTABLE

◆ ACPI_BERT_UNCORRECTABLE

◆ ACPI_BGRT_DISPLAYED

◆ ACPI_BGRT_ORIENTATION_OFFSET

◆ ACPI_CDAT_DSIS_MEM_ATTACHED

◆ ACPI_CEDT_CFMWS_ARITHMETIC_MODULO

◆ ACPI_CEDT_CFMWS_ARITHMETIC_XOR

◆ ACPI_CEDT_CFMWS_RESTRICT_FIXED

◆ ACPI_CEDT_CFMWS_RESTRICT_PMEM

◆ ACPI_CEDT_CFMWS_RESTRICT_TYPE2

◆ ACPI_CEDT_CFMWS_RESTRICT_TYPE3

◆ ACPI_CEDT_CFMWS_RESTRICT_VOLATILE

◆ ACPI_CEDT_CHBS_LENGTH_CXL11

◆ ACPI_CEDT_CHBS_LENGTH_CXL20

◆ ACPI_CEDT_CHBS_VERSION_CXL11

◆ ACPI_CEDT_CHBS_VERSION_CXL20

◆ ACPI_CEDT_DSMAS_NON_VOLATILE

◆ ACPI_CEDT_RDPAS_BUS_MASK

◆ ACPI_CEDT_RDPAS_DEVICE_MASK

◆ ACPI_CEDT_RDPAS_FUNCTION_MASK

◆ ACPI_CEDT_RDPAS_PROTOCOL_CACHEMEM

◆ ACPI_CEDT_RDPAS_PROTOCOL_IO

◆ ACPI_CSRT_DMA_CHANNEL

◆ ACPI_CSRT_DMA_CONTROLLER

◆ ACPI_CSRT_TIMER

◆ ACPI_CSRT_TYPE_DMA

◆ ACPI_CSRT_TYPE_INTERRUPT

◆ ACPI_CSRT_TYPE_TIMER

◆ ACPI_CSRT_XRUPT_CONTROLLER

◆ ACPI_CSRT_XRUPT_LINE

◆ ACPI_DBG2_1394_PORT

◆ ACPI_DBG2_1394_STANDARD

◆ ACPI_DBG2_16550_COMPATIBLE

◆ ACPI_DBG2_16550_NVIDIA

◆ ACPI_DBG2_16550_SUBSET

◆ ACPI_DBG2_16550_WITH_GAS

◆ ACPI_DBG2_APM88XXXX

◆ ACPI_DBG2_ARM_DCC

◆ ACPI_DBG2_ARM_PL011

◆ ACPI_DBG2_ARM_SBSA_32BIT

◆ ACPI_DBG2_ARM_SBSA_GENERIC

◆ ACPI_DBG2_BCM2835

◆ ACPI_DBG2_IMX6

◆ ACPI_DBG2_INTEL_LPSS

◆ ACPI_DBG2_INTEL_USIF

◆ ACPI_DBG2_MAX311XE_SPI

◆ ACPI_DBG2_MSM8974

◆ ACPI_DBG2_MSM8X60

◆ ACPI_DBG2_NET_PORT

◆ ACPI_DBG2_SAM5250

◆ ACPI_DBG2_SDM845_1_8432MHZ

◆ ACPI_DBG2_SDM845_7_372MHZ

◆ ACPI_DBG2_SERIAL_PORT

◆ ACPI_DBG2_TI_OMAP

◆ ACPI_DBG2_USB_EHCI

◆ ACPI_DBG2_USB_PORT

◆ ACPI_DBG2_USB_XHCI

◆ ACPI_DMAR_ALL_PORTS

◆ ACPI_DMAR_ALLOW_ALL

◆ ACPI_DMAR_INCLUDE_ALL

◆ ACPI_DMAR_INTR_REMAP

◆ ACPI_DMAR_X2APIC_MODE

◆ ACPI_DMAR_X2APIC_OPT_OUT

◆ ACPI_DRTM_ACCESS_ALLOWED

◆ ACPI_DRTM_AUTHORITY_ORDER

◆ ACPI_DRTM_ENABLE_GAP_CODE

◆ ACPI_DRTM_INCOMPLETE_MEASUREMENTS

◆ ACPI_EINJ_MEMORY_CORRECTABLE

◆ ACPI_EINJ_MEMORY_FATAL

◆ ACPI_EINJ_MEMORY_UNCORRECTABLE

◆ ACPI_EINJ_PCIX_CORRECTABLE

◆ ACPI_EINJ_PCIX_FATAL

◆ ACPI_EINJ_PCIX_UNCORRECTABLE

◆ ACPI_EINJ_PLATFORM_CORRECTABLE

◆ ACPI_EINJ_PLATFORM_FATAL

◆ ACPI_EINJ_PLATFORM_UNCORRECTABLE

◆ ACPI_EINJ_PRESERVE

◆ ACPI_EINJ_PROCESSOR_CORRECTABLE

◆ ACPI_EINJ_PROCESSOR_FATAL

◆ ACPI_EINJ_PROCESSOR_UNCORRECTABLE

◆ ACPI_EINJ_VENDOR_DEFINED

◆ ACPI_ERST_PRESERVE

◆ ACPI_GTDT_ALWAYS_ON

◆ ACPI_GTDT_GT_ALWAYS_ON

◆ ACPI_GTDT_GT_IRQ_MODE

◆ ACPI_GTDT_GT_IRQ_POLARITY

◆ ACPI_GTDT_GT_IS_SECURE_TIMER

◆ ACPI_GTDT_INTERRUPT_MODE

◆ ACPI_GTDT_INTERRUPT_POLARITY

◆ ACPI_GTDT_WATCHDOG_IRQ_MODE

◆ ACPI_GTDT_WATCHDOG_IRQ_POLARITY

◆ ACPI_GTDT_WATCHDOG_SECURE

◆ ACPI_HEST_BUS

◆ ACPI_HEST_CORRECTABLE

◆ ACPI_HEST_ERR_THRESHOLD_VALUE

◆ ACPI_HEST_ERR_THRESHOLD_WINDOW

◆ ACPI_HEST_ERROR_ENTRY_COUNT

◆ ACPI_HEST_FIRMWARE_FIRST

◆ ACPI_HEST_GEN_ERROR_CORRECTED

◆ ACPI_HEST_GEN_ERROR_FATAL

◆ ACPI_HEST_GEN_ERROR_NONE

◆ ACPI_HEST_GEN_ERROR_RECOVERABLE

◆ ACPI_HEST_GEN_VALID_FRU_ID

◆ ACPI_HEST_GEN_VALID_FRU_STRING

◆ ACPI_HEST_GEN_VALID_TIMESTAMP

◆ ACPI_HEST_GHES_ASSIST

◆ ACPI_HEST_GLOBAL

◆ ACPI_HEST_MULTIPLE_CORRECTABLE

◆ ACPI_HEST_MULTIPLE_UNCORRECTABLE

◆ ACPI_HEST_POLL_INTERVAL

◆ ACPI_HEST_POLL_THRESHOLD_VALUE

◆ ACPI_HEST_POLL_THRESHOLD_WINDOW

◆ ACPI_HEST_SEGMENT

◆ ACPI_HEST_TYPE

◆ ACPI_HEST_UNCORRECTABLE

◆ ACPI_HMAT_1ST_LEVEL_CACHE

◆ ACPI_HMAT_2ND_LEVEL_CACHE

◆ ACPI_HMAT_3RD_LEVEL_CACHE

◆ ACPI_HMAT_ACCESS_BANDWIDTH

◆ ACPI_HMAT_ACCESS_LATENCY

◆ ACPI_HMAT_CA_COMPLEX_CACHE_INDEXING

◆ ACPI_HMAT_CA_DIRECT_MAPPED

◆ ACPI_HMAT_CA_NONE

◆ ACPI_HMAT_CACHE_ASSOCIATIVITY

◆ ACPI_HMAT_CACHE_LEVEL

◆ ACPI_HMAT_CACHE_LINE_SIZE

◆ ACPI_HMAT_CP_NONE

◆ ACPI_HMAT_CP_WB

◆ ACPI_HMAT_CP_WT

◆ ACPI_HMAT_INITIATOR_PD_VALID

◆ ACPI_HMAT_MEMORY

◆ ACPI_HMAT_MEMORY_HIERARCHY

◆ ACPI_HMAT_MINIMUM_XFER_SIZE

◆ ACPI_HMAT_NON_SEQUENTIAL_XFERS

◆ ACPI_HMAT_READ_BANDWIDTH

◆ ACPI_HMAT_READ_LATENCY

◆ ACPI_HMAT_TOTAL_CACHE_LEVEL

◆ ACPI_HMAT_WRITE_BANDWIDTH

◆ ACPI_HMAT_WRITE_LATENCY

◆ ACPI_HMAT_WRITE_POLICY

◆ ACPI_HPET_PAGE_PROTECT_MASK

◆ ACPI_SIG_AEST

◆ ACPI_SIG_ASF

◆ ACPI_SIG_BERT

◆ ACPI_SIG_BGRT

◆ ACPI_SIG_BOOT

◆ ACPI_SIG_CEDT

◆ ACPI_SIG_CPEP

◆ ACPI_SIG_CSRT

◆ ACPI_SIG_DBG2

◆ ACPI_SIG_DBGP

◆ ACPI_SIG_DMAR

◆ ACPI_SIG_DRTM

◆ ACPI_SIG_ECDT

◆ ACPI_SIG_EINJ

◆ ACPI_SIG_ERST

◆ ACPI_SIG_FPDT

◆ ACPI_SIG_GTDT

| #define ACPI_SIG_GTDT "GTDT" /* Generic Timer Description Table */ |

◆ ACPI_SIG_HEST

◆ ACPI_SIG_HMAT

| #define ACPI_SIG_HMAT "HMAT" /* Heterogeneous Memory Attributes Table */ |

◆ ACPI_SIG_HPET

◆ ACPI_SIG_IBFT

◆ ACPI_SIG_MATR

◆ ACPI_SIG_MSCT

◆ ACPI_SIG_MSDM

◆ ACPI_SIG_PCCS

◆ ACPI_SIG_S3PT

Typedef Documentation

◆ ACPI_ASF_ADDRESS

| typedef struct acpi_asf_address ACPI_ASF_ADDRESS |

◆ ACPI_ASF_ALERT

| typedef struct acpi_asf_alert ACPI_ASF_ALERT |

◆ ACPI_ASF_ALERT_DATA

◆ ACPI_ASF_CONTROL_DATA

◆ ACPI_ASF_HEADER

| typedef struct acpi_asf_header ACPI_ASF_HEADER |

◆ ACPI_ASF_INFO

| typedef struct acpi_asf_info ACPI_ASF_INFO |

◆ ACPI_ASF_REMOTE

| typedef struct acpi_asf_remote ACPI_ASF_REMOTE |

◆ ACPI_ASF_RMCP

| typedef struct acpi_asf_rmcp ACPI_ASF_RMCP |

◆ ACPI_BERT_REGION

| typedef struct acpi_bert_region ACPI_BERT_REGION |

◆ ACPI_CDAT_DSEMTS

| typedef struct acpi_cdat_dsemts ACPI_CDAT_DSEMTS |

◆ ACPI_CDAT_DSIS

| typedef struct acpi_cdat_dsis ACPI_CDAT_DSIS |

◆ ACPI_CDAT_DSLBIS

| typedef struct acpi_cdat_dslbis ACPI_CDAT_DSLBIS |

◆ ACPI_CDAT_DSMAS

| typedef struct acpi_cadt_dsmas ACPI_CDAT_DSMAS |

◆ ACPI_CDAT_DSMSCIS

| typedef struct acpi_cdat_dsmscis ACPI_CDAT_DSMSCIS |

◆ ACPI_CDAT_HEADER

| typedef struct acpi_cdat_header ACPI_CDAT_HEADER |

◆ ACPI_CDAT_SSLBE

| typedef struct acpi_cdat_sslbe ACPI_CDAT_SSLBE |

◆ ACPI_CDAT_SSLBIS

| typedef struct acpi_cdat_sslbis ACPI_CDAT_SSLBIS |

◆ ACPI_CEDT_CFMWS

| typedef struct acpi_cedt_cfmws ACPI_CEDT_CFMWS |

◆ ACPI_CEDT_CFMWS_TARGET_ELEMENT

◆ ACPI_CEDT_CHBS

| typedef struct acpi_cedt_chbs ACPI_CEDT_CHBS |

◆ ACPI_CEDT_HEADER

| typedef struct acpi_cedt_header ACPI_CEDT_HEADER |

◆ ACPI_CPEP_POLLING

| typedef struct acpi_cpep_polling ACPI_CPEP_POLLING |

◆ ACPI_CSRT_DESCRIPTOR

◆ ACPI_CSRT_GROUP

| typedef struct acpi_csrt_group ACPI_CSRT_GROUP |

◆ ACPI_CSRT_SHARED_INFO

◆ ACPI_DBG2_DEVICE

| typedef struct acpi_dbg2_device ACPI_DBG2_DEVICE |

◆ ACPI_DBG2_HEADER

| typedef struct acpi_dbg2_header ACPI_DBG2_HEADER |

◆ ACPI_DMAR_ANDD

| typedef struct acpi_dmar_andd ACPI_DMAR_ANDD |

◆ ACPI_DMAR_ATSR

| typedef struct acpi_dmar_atsr ACPI_DMAR_ATSR |

◆ ACPI_DMAR_DEVICE_SCOPE

◆ ACPI_DMAR_HARDWARE_UNIT

◆ ACPI_DMAR_HEADER

| typedef struct acpi_dmar_header ACPI_DMAR_HEADER |

◆ ACPI_DMAR_PCI_PATH

◆ ACPI_DMAR_RESERVED_MEMORY

◆ ACPI_DMAR_RHSA

| typedef struct acpi_dmar_rhsa ACPI_DMAR_RHSA |

◆ ACPI_DMAR_SATC

| typedef struct acpi_dmar_satc ACPI_DMAR_SATC |

◆ ACPI_DRTM_DPS_ID

| typedef struct acpi_drtm_dps_id ACPI_DRTM_DPS_ID |

◆ ACPI_DRTM_RESOURCE

◆ ACPI_DRTM_RESOURCE_LIST

◆ ACPI_DRTM_VTABLE_LIST

◆ ACPI_EINJ_ENTRY

| typedef struct acpi_einj_entry ACPI_EINJ_ENTRY |

◆ ACPI_EINJ_ERROR_TYPE_WITH_ADDR

◆ ACPI_EINJ_TRIGGER

| typedef struct acpi_einj_trigger ACPI_EINJ_TRIGGER |

◆ ACPI_EINJ_VENDOR

| typedef struct acpi_einj_vendor ACPI_EINJ_VENDOR |

◆ ACPI_ERST_ENTRY

| typedef struct acpi_erst_entry ACPI_ERST_ENTRY |

◆ ACPI_ERST_INFO

| typedef struct acpi_erst_info ACPI_ERST_INFO |

◆ ACPI_FPDT_BOOT

| typedef struct acpi_fpdt_boot ACPI_FPDT_BOOT |

◆ ACPI_FPDT_BOOT_POINTER

◆ ACPI_FPDT_HEADER

| typedef struct acpi_fpdt_header ACPI_FPDT_HEADER |

◆ ACPI_FPDT_S3PT_POINTER

◆ ACPI_GTDT_EL2

| typedef struct acpi_gtdt_el2 ACPI_GTDT_EL2 |

◆ ACPI_GTDT_HEADER

| typedef struct acpi_gtdt_header ACPI_GTDT_HEADER |

◆ ACPI_GTDT_TIMER_BLOCK

◆ ACPI_GTDT_TIMER_ENTRY

◆ ACPI_GTDT_WATCHDOG

◆ ACPI_HEST_AER

| typedef struct acpi_hest_aer ACPI_HEST_AER |

◆ ACPI_HEST_AER_BRIDGE

◆ ACPI_HEST_AER_COMMON

◆ ACPI_HEST_AER_ROOT

◆ ACPI_HEST_GENERIC

| typedef struct acpi_hest_generic ACPI_HEST_GENERIC |

◆ ACPI_HEST_GENERIC_DATA

◆ ACPI_HEST_GENERIC_DATA_V300

◆ ACPI_HEST_GENERIC_STATUS

◆ ACPI_HEST_GENERIC_V2

◆ ACPI_HEST_HEADER

| typedef struct acpi_hest_header ACPI_HEST_HEADER |

◆ ACPI_HEST_IA_CORRECTED

◆ ACPI_HEST_IA_DEFERRED_CHECK

◆ ACPI_HEST_IA_ERROR_BANK

◆ ACPI_HEST_IA_MACHINE_CHECK

◆ ACPI_HEST_IA_NMI

| typedef struct acpi_hest_ia_nmi ACPI_HEST_IA_NMI |

◆ ACPI_HEST_NOTIFY

| typedef struct acpi_hest_notify ACPI_HEST_NOTIFY |

◆ ACPI_HMAT_CACHE

| typedef struct acpi_hmat_cache ACPI_HMAT_CACHE |

◆ ACPI_HMAT_LOCALITY

◆ ACPI_HMAT_PROXIMITY_DOMAIN

◆ ACPI_HMAT_STRUCTURE

◆ ACPI_IBFT_CONTROL

| typedef struct acpi_ibft_control ACPI_IBFT_CONTROL |

◆ ACPI_IBFT_HEADER

| typedef struct acpi_ibft_header ACPI_IBFT_HEADER |

◆ ACPI_IBFT_INITIATOR

◆ ACPI_IBFT_NIC

| typedef struct acpi_ibft_nic ACPI_IBFT_NIC |

◆ ACPI_IBFT_TARGET

| typedef struct acpi_ibft_target ACPI_IBFT_TARGET |

◆ ACPI_S3PT_RESUME

| typedef struct acpi_s3pt_resume ACPI_S3PT_RESUME |

◆ ACPI_S3PT_SUSPEND

| typedef struct acpi_s3pt_suspend ACPI_S3PT_SUSPEND |

◆ ACPI_SUBTABLE_HEADER

◆ ACPI_TABLE_ASF

| typedef struct acpi_table_asf ACPI_TABLE_ASF |

◆ ACPI_TABLE_BERT

| typedef struct acpi_table_bert ACPI_TABLE_BERT |

◆ ACPI_TABLE_BGRT

| typedef struct acpi_table_bgrt ACPI_TABLE_BGRT |

◆ ACPI_TABLE_BOOT

| typedef struct acpi_table_boot ACPI_TABLE_BOOT |

◆ ACPI_TABLE_CDAT

| typedef struct acpi_table_cdat ACPI_TABLE_CDAT |

◆ ACPI_TABLE_CEDT

| typedef struct acpi_table_cedt ACPI_TABLE_CEDT |

◆ ACPI_TABLE_CPEP

| typedef struct acpi_table_cpep ACPI_TABLE_CPEP |

◆ ACPI_TABLE_CSRT

| typedef struct acpi_table_csrt ACPI_TABLE_CSRT |

◆ ACPI_TABLE_DBG2

| typedef struct acpi_table_dbg2 ACPI_TABLE_DBG2 |

◆ ACPI_TABLE_DBGP

| typedef struct acpi_table_dbgp ACPI_TABLE_DBGP |

◆ ACPI_TABLE_DMAR

| typedef struct acpi_table_dmar ACPI_TABLE_DMAR |

◆ ACPI_TABLE_DRTM

| typedef struct acpi_table_drtm ACPI_TABLE_DRTM |

◆ ACPI_TABLE_ECDT

| typedef struct acpi_table_ecdt ACPI_TABLE_ECDT |

◆ ACPI_TABLE_EINJ

| typedef struct acpi_table_einj ACPI_TABLE_EINJ |

◆ ACPI_TABLE_ERST

| typedef struct acpi_table_erst ACPI_TABLE_ERST |

◆ ACPI_TABLE_FPDT

| typedef struct acpi_table_fpdt ACPI_TABLE_FPDT |

◆ ACPI_TABLE_GTDT

| typedef struct acpi_table_gtdt ACPI_TABLE_GTDT |

◆ ACPI_TABLE_HEST

| typedef struct acpi_table_hest ACPI_TABLE_HEST |

◆ ACPI_TABLE_HMAT

| typedef struct acpi_table_hmat ACPI_TABLE_HMAT |

◆ ACPI_TABLE_HPET

| typedef struct acpi_table_hpet ACPI_TABLE_HPET |

◆ ACPI_TABLE_IBFT

| typedef struct acpi_table_ibft ACPI_TABLE_IBFT |

◆ ACPI_TABLE_S3PT

| typedef struct acpi_table_s3pt ACPI_TABLE_S3PT |

◆ ACPI_WHEA_HEADER

| typedef struct acpi_whea_header ACPI_WHEA_HEADER |

Enumeration Type Documentation

◆ AcpiAsfType

| Enumerator | |

|---|---|

| ACPI_ASF_TYPE_INFO | |

| ACPI_ASF_TYPE_ALERT | |

| ACPI_ASF_TYPE_CONTROL | |

| ACPI_ASF_TYPE_BOOT | |

| ACPI_ASF_TYPE_ADDRESS | |

| ACPI_ASF_TYPE_RESERVED | |

Definition at line 183 of file actbl1.h.

184{

185 ACPI_ASF_TYPE_INFO = 0,

186 ACPI_ASF_TYPE_ALERT = 1,

187 ACPI_ASF_TYPE_CONTROL = 2,

188 ACPI_ASF_TYPE_BOOT = 3,

189 ACPI_ASF_TYPE_ADDRESS = 4,

190 ACPI_ASF_TYPE_RESERVED = 5

191};

◆ AcpiBertErrorSeverity

| Enumerator | |

|---|---|

| ACPI_BERT_ERROR_CORRECTABLE | |

| ACPI_BERT_ERROR_FATAL | |

| ACPI_BERT_ERROR_CORRECTED | |

| ACPI_BERT_ERROR_NONE | |

| ACPI_BERT_ERROR_RESERVED | |

Definition at line 332 of file actbl1.h.

333{

334 ACPI_BERT_ERROR_CORRECTABLE = 0,

335 ACPI_BERT_ERROR_FATAL = 1,

336 ACPI_BERT_ERROR_CORRECTED = 2,

337 ACPI_BERT_ERROR_NONE = 3,

339};

◆ AcpiCdatType

| Enumerator | |

|---|---|

| ACPI_CDAT_TYPE_DSMAS | |

| ACPI_CDAT_TYPE_DSLBIS | |

| ACPI_CDAT_TYPE_DSMSCIS | |

| ACPI_CDAT_TYPE_DSIS | |

| ACPI_CDAT_TYPE_DSEMTS | |

| ACPI_CDAT_TYPE_SSLBIS | |

| ACPI_CDAT_TYPE_RESERVED | |

Definition at line 424 of file actbl1.h.

425{

426 ACPI_CDAT_TYPE_DSMAS = 0,

427 ACPI_CDAT_TYPE_DSLBIS = 1,

428 ACPI_CDAT_TYPE_DSMSCIS = 2,

429 ACPI_CDAT_TYPE_DSIS = 3,

430 ACPI_CDAT_TYPE_DSEMTS = 4,

431 ACPI_CDAT_TYPE_SSLBIS = 5,

433};

◆ AcpiCedtType

| Enumerator | |

|---|---|

| ACPI_CEDT_TYPE_CHBS | |

| ACPI_CEDT_TYPE_CFMWS | |

| ACPI_CEDT_TYPE_CXIMS | |

| ACPI_CEDT_TYPE_RDPAS | |

| ACPI_CEDT_TYPE_RESERVED | |

Definition at line 559 of file actbl1.h.

560{

561 ACPI_CEDT_TYPE_CHBS = 0,

562 ACPI_CEDT_TYPE_CFMWS = 1,

563 ACPI_CEDT_TYPE_CXIMS = 2,

564 ACPI_CEDT_TYPE_RDPAS = 3,

565 ACPI_CEDT_TYPE_RESERVED = 4,

566};

◆ AcpiDmarScopeType

Definition at line 942 of file actbl1.h.

943{

944 ACPI_DMAR_SCOPE_TYPE_NOT_USED = 0,

945 ACPI_DMAR_SCOPE_TYPE_ENDPOINT = 1,

946 ACPI_DMAR_SCOPE_TYPE_BRIDGE = 2,

947 ACPI_DMAR_SCOPE_TYPE_IOAPIC = 3,

948 ACPI_DMAR_SCOPE_TYPE_HPET = 4,

949 ACPI_DMAR_SCOPE_TYPE_NAMESPACE = 5,

951};

◆ AcpiDmarType

| Enumerator | |

|---|---|

| ACPI_DMAR_TYPE_HARDWARE_UNIT | |

| ACPI_DMAR_TYPE_RESERVED_MEMORY | |

| ACPI_DMAR_TYPE_ROOT_ATS | |

| ACPI_DMAR_TYPE_HARDWARE_AFFINITY | |

| ACPI_DMAR_TYPE_NAMESPACE | |

| ACPI_DMAR_TYPE_SATC | |

| ACPI_DMAR_TYPE_RESERVED | |

Definition at line 916 of file actbl1.h.

917{

918 ACPI_DMAR_TYPE_HARDWARE_UNIT = 0,

919 ACPI_DMAR_TYPE_RESERVED_MEMORY = 1,

920 ACPI_DMAR_TYPE_ROOT_ATS = 2,

921 ACPI_DMAR_TYPE_HARDWARE_AFFINITY = 3,

922 ACPI_DMAR_TYPE_NAMESPACE = 4,

923 ACPI_DMAR_TYPE_SATC = 5,

925};

◆ AcpiEinjActions

Definition at line 1171 of file actbl1.h.

1172{

1173 ACPI_EINJ_BEGIN_OPERATION = 0,

1174 ACPI_EINJ_GET_TRIGGER_TABLE = 1,

1175 ACPI_EINJ_SET_ERROR_TYPE = 2,

1176 ACPI_EINJ_GET_ERROR_TYPE = 3,

1177 ACPI_EINJ_END_OPERATION = 4,

1178 ACPI_EINJ_EXECUTE_OPERATION = 5,

1179 ACPI_EINJ_CHECK_BUSY_STATUS = 6,

1180 ACPI_EINJ_GET_COMMAND_STATUS = 7,

1181 ACPI_EINJ_SET_ERROR_TYPE_WITH_ADDRESS = 8,

1182 ACPI_EINJ_GET_EXECUTE_TIMINGS = 9,

1185};

@ ACPI_EINJ_SET_ERROR_TYPE_WITH_ADDRESS

Definition: actbl1.h:1181

◆ AcpiEinjCommandStatus

| Enumerator | |

|---|---|

| ACPI_EINJ_SUCCESS | |

| ACPI_EINJ_FAILURE | |

| ACPI_EINJ_INVALID_ACCESS | |

| ACPI_EINJ_STATUS_RESERVED | |

Definition at line 1237 of file actbl1.h.

1238{

1239 ACPI_EINJ_SUCCESS = 0,

1240 ACPI_EINJ_FAILURE = 1,

1241 ACPI_EINJ_INVALID_ACCESS = 2,

1243};

◆ AcpiEinjInstructions

| Enumerator | |

|---|---|

| ACPI_EINJ_READ_REGISTER | |

| ACPI_EINJ_READ_REGISTER_VALUE | |

| ACPI_EINJ_WRITE_REGISTER | |

| ACPI_EINJ_WRITE_REGISTER_VALUE | |

| ACPI_EINJ_NOOP | |

| ACPI_EINJ_FLUSH_CACHELINE | |

| ACPI_EINJ_INSTRUCTION_RESERVED | |

Definition at line 1189 of file actbl1.h.

1190{

1191 ACPI_EINJ_READ_REGISTER = 0,

1192 ACPI_EINJ_READ_REGISTER_VALUE = 1,

1193 ACPI_EINJ_WRITE_REGISTER = 2,

1194 ACPI_EINJ_WRITE_REGISTER_VALUE = 3,

1195 ACPI_EINJ_NOOP = 4,

1196 ACPI_EINJ_FLUSH_CACHELINE = 5,

1198};

◆ AcpiErstActions

Definition at line 1294 of file actbl1.h.

1295{

1296 ACPI_ERST_BEGIN_WRITE = 0,

1297 ACPI_ERST_BEGIN_READ = 1,

1298 ACPI_ERST_BEGIN_CLEAR = 2,

1299 ACPI_ERST_END = 3,

1300 ACPI_ERST_SET_RECORD_OFFSET = 4,

1301 ACPI_ERST_EXECUTE_OPERATION = 5,

1302 ACPI_ERST_CHECK_BUSY_STATUS = 6,

1303 ACPI_ERST_GET_COMMAND_STATUS = 7,

1304 ACPI_ERST_GET_RECORD_ID = 8,

1305 ACPI_ERST_SET_RECORD_ID = 9,

1306 ACPI_ERST_GET_RECORD_COUNT = 10,

1307 ACPI_ERST_BEGIN_DUMMY_WRIITE = 11,

1308 ACPI_ERST_NOT_USED = 12,

1309 ACPI_ERST_GET_ERROR_RANGE = 13,

1310 ACPI_ERST_GET_ERROR_LENGTH = 14,

1311 ACPI_ERST_GET_ERROR_ATTRIBUTES = 15,

1312 ACPI_ERST_EXECUTE_TIMINGS = 16,

1314};

◆ AcpiErstCommandStatus

| Enumerator | |

|---|---|

| ACPI_ERST_SUCCESS | |

| ACPI_ERST_NO_SPACE | |

| ACPI_ERST_NOT_AVAILABLE | |

| ACPI_ERST_FAILURE | |

| ACPI_ERST_RECORD_EMPTY | |

| ACPI_ERST_NOT_FOUND | |

| ACPI_ERST_STATUS_RESERVED | |

Definition at line 1344 of file actbl1.h.

1345{

1346 ACPI_ERST_SUCCESS = 0,

1347 ACPI_ERST_NO_SPACE = 1,

1348 ACPI_ERST_NOT_AVAILABLE = 2,

1349 ACPI_ERST_FAILURE = 3,

1350 ACPI_ERST_RECORD_EMPTY = 4,

1351 ACPI_ERST_NOT_FOUND = 5,

1353};

◆ AcpiErstInstructions

Definition at line 1318 of file actbl1.h.

1319{

1320 ACPI_ERST_READ_REGISTER = 0,

1321 ACPI_ERST_READ_REGISTER_VALUE = 1,

1322 ACPI_ERST_WRITE_REGISTER = 2,

1323 ACPI_ERST_WRITE_REGISTER_VALUE = 3,

1324 ACPI_ERST_NOOP = 4,

1325 ACPI_ERST_LOAD_VAR1 = 5,

1326 ACPI_ERST_LOAD_VAR2 = 6,

1327 ACPI_ERST_STORE_VAR1 = 7,

1328 ACPI_ERST_ADD = 8,

1329 ACPI_ERST_SUBTRACT = 9,

1330 ACPI_ERST_ADD_VALUE = 10,

1331 ACPI_ERST_SUBTRACT_VALUE = 11,

1332 ACPI_ERST_STALL = 12,

1333 ACPI_ERST_STALL_WHILE_TRUE = 13,

1334 ACPI_ERST_SKIP_NEXT_IF_TRUE = 14,

1335 ACPI_ERST_GOTO = 15,

1336 ACPI_ERST_SET_SRC_ADDRESS_BASE = 16,

1337 ACPI_ERST_SET_DST_ADDRESS_BASE = 17,

1338 ACPI_ERST_MOVE_DATA = 18,

1340};

◆ AcpiFpdtType

| Enumerator | |

|---|---|

| ACPI_FPDT_TYPE_BOOT | |

| ACPI_FPDT_TYPE_S3PERF | |

◆ AcpiGtdtType

| Enumerator | |

|---|---|

| ACPI_GTDT_TYPE_TIMER_BLOCK | |

| ACPI_GTDT_TYPE_WATCHDOG | |

| ACPI_GTDT_TYPE_RESERVED | |

◆ AcpiHestNotifyTypes

Definition at line 1725 of file actbl1.h.

1726{

1727 ACPI_HEST_NOTIFY_POLLED = 0,

1728 ACPI_HEST_NOTIFY_EXTERNAL = 1,

1729 ACPI_HEST_NOTIFY_LOCAL = 2,

1730 ACPI_HEST_NOTIFY_SCI = 3,

1731 ACPI_HEST_NOTIFY_NMI = 4,

1740};

◆ AcpiHestTypes

Definition at line 1630 of file actbl1.h.

1631{

1632 ACPI_HEST_TYPE_IA32_CHECK = 0,

1633 ACPI_HEST_TYPE_IA32_CORRECTED_CHECK = 1,

1634 ACPI_HEST_TYPE_IA32_NMI = 2,

1635 ACPI_HEST_TYPE_NOT_USED3 = 3,

1636 ACPI_HEST_TYPE_NOT_USED4 = 4,

1637 ACPI_HEST_TYPE_NOT_USED5 = 5,

1638 ACPI_HEST_TYPE_AER_ROOT_PORT = 6,

1639 ACPI_HEST_TYPE_AER_ENDPOINT = 7,

1640 ACPI_HEST_TYPE_AER_BRIDGE = 8,

1641 ACPI_HEST_TYPE_GENERIC_ERROR = 9,

1642 ACPI_HEST_TYPE_GENERIC_ERROR_V2 = 10,

1643 ACPI_HEST_TYPE_IA32_DEFERRED_CHECK = 11,

1645};

◆ AcpiHmatType

◆ AcpiHpetPageProtect

| Enumerator | |

|---|---|

| ACPI_HPET_NO_PAGE_PROTECT | |

| ACPI_HPET_PAGE_PROTECT4 | |

| ACPI_HPET_PAGE_PROTECT64 | |

Definition at line 2121 of file actbl1.h.

2122{

2123 ACPI_HPET_NO_PAGE_PROTECT = 0,

2124 ACPI_HPET_PAGE_PROTECT4 = 1,

2125 ACPI_HPET_PAGE_PROTECT64 = 2

2126};

◆ AcpiIbftType

| Enumerator | |

|---|---|

| ACPI_IBFT_TYPE_NOT_USED | |

| ACPI_IBFT_TYPE_CONTROL | |

| ACPI_IBFT_TYPE_INITIATOR | |

| ACPI_IBFT_TYPE_NIC | |

| ACPI_IBFT_TYPE_TARGET | |

| ACPI_IBFT_TYPE_EXTENSIONS | |

| ACPI_IBFT_TYPE_RESERVED | |

Definition at line 2164 of file actbl1.h.

2165{

2166 ACPI_IBFT_TYPE_NOT_USED = 0,

2167 ACPI_IBFT_TYPE_CONTROL = 1,

2168 ACPI_IBFT_TYPE_INITIATOR = 2,

2169 ACPI_IBFT_TYPE_NIC = 3,

2170 ACPI_IBFT_TYPE_TARGET = 4,

2171 ACPI_IBFT_TYPE_EXTENSIONS = 5,

2173};

◆ AcpiS3ptType

| Enumerator | |

|---|---|

| ACPI_S3PT_TYPE_RESUME | |

| ACPI_S3PT_TYPE_SUSPEND | |

| ACPI_FPDT_BOOT_PERFORMANCE | |

Definition at line 1443 of file actbl1.h.

1444{

1445 ACPI_S3PT_TYPE_RESUME = 0,

1446 ACPI_S3PT_TYPE_SUSPEND = 1,

1447 ACPI_FPDT_BOOT_PERFORMANCE = 2

1448};