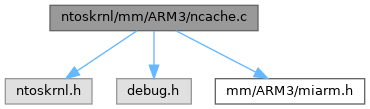

Include dependency graph for ncache.c:

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

| #define | MODULE_INVOLVED_IN_ARM3 |

Functions | |

| PVOID NTAPI | MmAllocateNonCachedMemory (IN SIZE_T NumberOfBytes) |

| VOID NTAPI | MmFreeNonCachedMemory (IN PVOID BaseAddress, IN SIZE_T NumberOfBytes) |

Macro Definition Documentation

◆ MODULE_INVOLVED_IN_ARM3

◆ NDEBUG

Function Documentation

◆ MmAllocateNonCachedMemory()

Definition at line 25 of file ncache.c.

26{

27 PFN_COUNT PageCount, MdlPageCount;

28 PFN_NUMBER PageFrameIndex;

30 MI_PFN_CACHE_ATTRIBUTE CacheAttribute;

33 PPFN_NUMBER MdlPages;

34 PMMPTE PointerPte;

36

37 //

38 // Get the page count

39 //

42

43 //

44 // Use the MDL allocator for simplicity, so setup the parameters

45 //

46 LowAddress.QuadPart = 0;

50

51 //

52 // Now call the MDL allocator

53 //

55 HighAddress,

56 SkipBytes,

57 NumberOfBytes,

58 CacheAttribute,

59 0);

61

62 //

63 // Get the MDL VA and check how many pages we got (could be partial)

64 //

67 if (PageCount != MdlPageCount)

68 {

69 //

70 // Unlike MDLs, partial isn't okay for a noncached allocation, so fail

71 //

72 ASSERT(PageCount > MdlPageCount);

76 }

77

78 //

79 // Allocate system PTEs for the base address

80 // We use an extra page to store the actual MDL pointer for the free later

81 //

83 if (!PointerPte)

84 {

85 //

86 // Out of memory...

87 //

91 }

92

93 //

94 // Store the MDL pointer

95 //

97

98 //

99 // Okay, now see what range we got

100 //

102

103 //

104 // This is our array of pages

105 //

107

108 //

109 // Setup the template PTE

110 //

112

113 //

114 // Now check what kind of caching we should use

115 //

116 switch (CacheAttribute)

117 {

119

120 //

121 // Disable caching

122 //

125 break;

126

128

129 //

130 // Enable write combining

131 //

134 break;

135

136 default:

137 //

138 // Nothing to do

139 //

140 break;

141 }

142

143 //

144 // Now loop the MDL pages

145 //

146 do

147 {

148 //

149 // Get the PFN

150 //

151 PageFrameIndex = *MdlPages++;

152

153 //

154 // Set the PFN in the page and write it

155 //

158 } while (--PageCount);

159

160 //

161 // Return the base address

162 //

164

165}

Definition: nsiface.idl:2307

MI_PFN_CACHE_ATTRIBUTE MiPlatformCacheAttributes[2][MmMaximumCacheType]

Definition: iosup.c:27

PMDL NTAPI MiAllocatePagesForMdl(IN PHYSICAL_ADDRESS LowAddress, IN PHYSICAL_ADDRESS HighAddress, IN PHYSICAL_ADDRESS SkipBytes, IN SIZE_T TotalBytes, IN MI_PFN_CACHE_ATTRIBUTE CacheAttribute, IN ULONG Flags)

Definition: freelist.c:182

enum _MI_PFN_CACHE_ATTRIBUTE MI_PFN_CACHE_ATTRIBUTE

PMMPTE NTAPI MiReserveSystemPtes(IN ULONG NumberOfPtes, IN MMSYSTEM_PTE_POOL_TYPE SystemPtePoolType)

Definition: syspte.c:246

FORCEINLINE VOID MI_WRITE_VALID_PTE(IN PMMPTE PointerPte, IN MMPTE TempPte)

Definition: miarm.h:967

_In_ HANDLE _Outptr_result_bytebuffer_ ViewSize _Pre_valid_ PVOID * BaseAddress

Definition: mmfuncs.h:404

Definition: mmtypes.h:212

Definition: typedefs.h:103

_Must_inspect_result_ typedef _In_ PHYSICAL_ADDRESS _Inout_ PLARGE_INTEGER NumberOfBytes

Definition: iotypes.h:1036

#define BYTES_TO_PAGES(Size)

#define ADDRESS_AND_SIZE_TO_SPAN_PAGES(_Va, _Size)

_Must_inspect_result_ _In_ PHYSICAL_ADDRESS _In_ PHYSICAL_ADDRESS SkipBytes

Definition: mmfuncs.h:227

Referenced by NdisAllocateMemory(), and TestMessageHandler().

◆ MmFreeNonCachedMemory()

Definition at line 172 of file ncache.c.

174{

176 PMMPTE PointerPte;

177 PFN_COUNT PageCount;

178

179 //

180 // Sanity checks

181 //

184

185 //

186 // Get the page count

187 //

189

190 //

191 // Get the first PTE

192 //

194

195 //

196 // Remember this is where we store the shadow MDL pointer

197 //

199

200 //

201 // Kill the MDL (and underlying pages)

202 //

205

206 //

207 // Now free the system PTEs for the underlying VA

208 //

210}

VOID NTAPI MiReleaseSystemPtes(IN PMMPTE StartingPte, IN ULONG NumberOfPtes, IN MMSYSTEM_PTE_POOL_TYPE SystemPtePoolType)

Definition: syspte.c:264

#define PAGE_ALIGN(Va)

Referenced by NdisFreeMemory(), and TestCleanEverything().