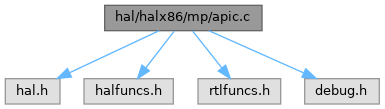

#include <hal.h>#include <halfuncs.h>#include <rtlfuncs.h>#include <debug.h>

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

| #define | BIOS_AREA 0x0 |

| #define | COMMON_AREA 0x2000 |

| #define | HZ (100) |

| #define | APIC_DIVISOR (16) |

| #define | CMOS_READ(address) |

| #define | CMOS_WRITE(address, value) |

Functions | |

| ULONG | Read8254Timer (VOID) |

| VOID | WaitFor8254Wraparound (VOID) |

| VOID | MpsTimerInterrupt (VOID) |

| VOID | MpsErrorInterrupt (VOID) |

| VOID | MpsSpuriousInterrupt (VOID) |

| VOID | MpsIpiInterrupt (VOID) |

| ULONG | APICGetMaxLVT (VOID) |

| VOID | APICClear (VOID) |

| VOID | EnableApicMode (VOID) |

| __inline VOID | DisableSMPMode (VOID) |

| VOID | DumpESR (VOID) |

| VOID | APICDisable (VOID) |

| static VOID | APICDumpBit (ULONG base) |

| VOID | APICDump (VOID) |

| BOOLEAN | VerifyLocalAPIC (VOID) |

| VOID | APICSetup (VOID) |

| VOID | MpsErrorHandler (VOID) |

| VOID | MpsSpuriousHandler (VOID) |

| VOID | MpsIRQTrapFrameToTrapFrame (PKIRQ_TRAPFRAME IrqTrapFrame, PKTRAP_FRAME TrapFrame) |

| VOID | MpsTimerHandler (ULONG Vector, PKIRQ_TRAPFRAME Trapframe) |

| VOID | APICSetupLVTT (ULONG ClockTicks) |

| VOID | APICCalibrateTimer (ULONG CPU) |

| VOID | SetInterruptGate (ULONG index, ULONG_PTR address) |

| VOID | HaliInitBSP (VOID) |

| VOID FASTCALL DECLSPEC_NORETURN | HalpApcInterruptHandler (IN PKTRAP_FRAME TrapFrame) |

Variables | |

| ULONG | CPUCount |

| ULONG | BootCPU |

| ULONG | OnlineCPUs |

| CPU_INFO | CPUMap [MAX_CPU] |

| PULONG | APICBase = (PULONG)APIC_DEFAULT_BASE |

| ULONG | APICMode |

| ULONG | lastregr [MAX_CPU] |

| ULONG | lastvalr [MAX_CPU] |

| ULONG | lastregw [MAX_CPU] |

| ULONG | lastvalw [MAX_CPU] |

| CHAR * | APstart |

| CHAR * | APend |

| ULONG_PTR | KernelBase |

Macro Definition Documentation

◆ APIC_DIVISOR

◆ BIOS_AREA

◆ CMOS_READ

◆ CMOS_WRITE

◆ COMMON_AREA

◆ HZ

◆ NDEBUG

Function Documentation

◆ APICCalibrateTimer()

Definition at line 794 of file apic.c.

Referenced by HaliInitBSP(), and HalInitializeProcessor().

◆ APICClear()

Definition at line 111 of file apic.c.

Referenced by APICDisable(), and EnableApicMode().

◆ APICDisable()

◆ APICDump()

Definition at line 245 of file apic.c.

Referenced by MpsErrorHandler(), and MpsSpuriousHandler().

◆ APICDumpBit()

Definition at line 225 of file apic.c.

Referenced by APICDump().

◆ APICGetMaxLVT()

Definition at line 99 of file apic.c.

Referenced by APICClear(), APICDump(), APICSetup(), DumpESR(), and VerifyLocalAPIC().

◆ APICSetup()

Definition at line 482 of file apic.c.

Referenced by HaliInitBSP(), and HalInitializeProcessor().

◆ APICSetupLVTT()

Definition at line 770 of file apic.c.

Referenced by APICCalibrateTimer().

◆ DisableSMPMode()

◆ DumpESR()

◆ EnableApicMode()

Definition at line 174 of file apic.c.

Referenced by HaliInitBSP().

◆ HaliInitBSP()

Definition at line 886 of file apic.c.

Referenced by HalInitializeProcessor().

◆ HalpApcInterruptHandler()

| VOID FASTCALL DECLSPEC_NORETURN HalpApcInterruptHandler | ( | IN PKTRAP_FRAME | TrapFrame | ) |

Definition at line 1115 of file apic.c.

◆ MpsErrorHandler()

Definition at line 634 of file apic.c.

◆ MpsErrorInterrupt()

Referenced by HaliInitBSP().

◆ MpsIpiInterrupt()

Referenced by HaliInitBSP().

◆ MpsIRQTrapFrameToTrapFrame()

| VOID MpsIRQTrapFrameToTrapFrame | ( | PKIRQ_TRAPFRAME | IrqTrapFrame, |

| PKTRAP_FRAME | TrapFrame | ||

| ) |

Definition at line 708 of file apic.c.

Referenced by MpsTimerHandler().

◆ MpsSpuriousHandler()

◆ MpsSpuriousInterrupt()

Referenced by HaliInitBSP().

◆ MpsTimerHandler()

| VOID MpsTimerHandler | ( | ULONG | Vector, |

| PKIRQ_TRAPFRAME | Trapframe | ||

| ) |

Definition at line 733 of file apic.c.

◆ MpsTimerInterrupt()

Referenced by HaliInitBSP().

◆ Read8254Timer()

◆ SetInterruptGate()

Definition at line 849 of file apic.c.

Referenced by HaliInitBSP().

◆ VerifyLocalAPIC()

Definition at line 350 of file apic.c.

Referenced by HaliInitBSP().

◆ WaitFor8254Wraparound()

Variable Documentation

◆ APend

| CHAR * APend |

Definition at line 70 of file apic.c.

Referenced by HaliInitBSP().

◆ APICBase

Definition at line 47 of file apic.c.

Referenced by HaliInitBSP().

◆ APICMode

| ULONG APICMode |

Definition at line 49 of file apic.c.

Referenced by APICSetup(), HaliGetSmpConfig(), and HaliInitBSP().

◆ APstart

|

extern |

Referenced by HaliInitBSP().

◆ BootCPU

| ULONG BootCPU |

Definition at line 38 of file apic.c.

Referenced by APICSetup(), HaliInitBSP(), and HaliMPProcessorInfo().

◆ CPUCount

| ULONG CPUCount |

Definition at line 37 of file apic.c.

Referenced by HalAllProcessorsStarted(), HaliMPProcessorInfo(), and HalStartNextProcessor().

◆ CPUMap

| CPU_INFO CPUMap[MAX_CPU] |

Definition at line 40 of file apic.c.

Referenced by APICCalibrateTimer(), APICSetup(), HaliMPProcessorInfo(), and HalInitializeProcessor().

◆ KernelBase

|

extern |

Definition at line 20 of file halinit_mp.c.

Referenced by HalpInitPhase0(), and LoadWindowsCore().

◆ lastregr

| ULONG lastregr[MAX_CPU] |

Definition at line 52 of file apic.c.

Referenced by APICDump().

◆ lastregw

| ULONG lastregw[MAX_CPU] |

Definition at line 54 of file apic.c.

Referenced by APICDump().

◆ lastvalr

| ULONG lastvalr[MAX_CPU] |

Definition at line 53 of file apic.c.

Referenced by APICDump().

◆ lastvalw

| ULONG lastvalw[MAX_CPU] |

Definition at line 55 of file apic.c.

Referenced by APICDump().

◆ OnlineCPUs

| ULONG OnlineCPUs |

Definition at line 39 of file apic.c.

Referenced by HalAllProcessorsStarted(), HalInitializeProcessor(), and HalStartNextProcessor().