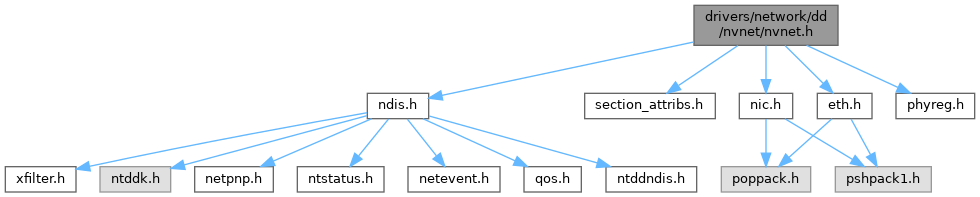

#include <ndis.h>#include <section_attribs.h>#include "eth.h"#include "nic.h"#include "phyreg.h"

Go to the source code of this file.

Classes | |

| union | _NVNET_OFFLOAD |

| struct | _NVNET_STATISTICS |

| struct | _NVNET_WAKE_FRAME |

| struct | _NVNET_TX_BUFFER_DATA |

| struct | _NVNET_TX_BUFFER |

| union | _NVNET_TBD |

| struct | _NVNET_TCB |

| union | _NV_RBD |

| struct | _NVNET_RBD |

| struct | _NVNET_SEND |

| struct | _NVNET_RECEIVE |

| struct | _NVNET_ADAPTER |

Enumerations | |

| enum | _NVNET_OPTIMIZATION_MODE { NV_OPTIMIZATION_MODE_DYNAMIC = 0 , NV_OPTIMIZATION_MODE_CPU , NV_OPTIMIZATION_MODE_THROUGHPUT } |

| enum | _NVNET_FLOW_CONTROL_MODE { NV_FLOW_CONTROL_DISABLE = 0 , NV_FLOW_CONTROL_AUTO , NV_FLOW_CONTROL_RX , NV_FLOW_CONTROL_TX , NV_FLOW_CONTROL_RX_TX } |

Macro Definition Documentation

◆ NO_KERNEL_LIST_ENTRY_CHECKS

◆ NV_ACTIVE

◆ NV_FORCE_FULL_DUPLEX

◆ NV_FORCE_SPEED_AND_DUPLEX

◆ NV_GIGABIT_PHY

◆ NV_IMPLICIT_ENTRIES

| #define NV_IMPLICIT_ENTRIES | ( | Length | ) | (((Length - (NV_MAXIMUM_SG_SIZE + 1)) >> NV_TX2_TSO_MAX_SHIFT) + 1) |

◆ NV_MAC_IN_USE

◆ NV_PACKET_PRIORITY

◆ NV_SEND_CHECKSUM

◆ NV_SEND_ERRATA_PRESENT

◆ NV_SEND_LARGE_SEND

◆ NV_TCB_CHECKSUM_IP

◆ NV_TCB_CHECKSUM_TCP

◆ NV_TCB_CHECKSUM_UDP

◆ NV_TCB_COALESCE

◆ NV_TCB_LARGE_SEND

◆ NV_UNIT_SEMAPHORE_ACQUIRED

◆ NV_USE_SOFT_MAC_ADDRESS

◆ NV_USER_SPEED_100

◆ NV_VLAN_TAGGING

◆ NVNET_ALIGNMENT

◆ NVNET_FRAGMENTATION_THRESHOLD

◆ NVNET_IM_MAX_IDLE

◆ NVNET_IM_THRESHOLD

◆ NVNET_MAXIMUM_FRAME_SIZE

◆ NVNET_MAXIMUM_FRAME_SIZE_JUMBO

◆ NVNET_MAXIMUM_LSO_FRAME_SIZE

◆ NVNET_MAXIMUM_VLAN_ID

◆ NVNET_MEDIA_DETECTION_INTERVAL

◆ NVNET_MINIMUM_LSO_SEGMENT_COUNT

◆ NVNET_MULTICAST_LIST_SIZE

◆ NVNET_PACKET_FILTERS

| #define NVNET_PACKET_FILTERS |

◆ NVNET_RECEIVE_BUFFER_SIZE

◆ NVNET_RECEIVE_DESCRIPTORS

◆ NVNET_RECEIVE_PROCESSING_LIMIT

◆ NVNET_TAG

◆ NVNET_TRANSMIT_BLOCKS

◆ NVNET_TRANSMIT_BUFFERS

◆ NVNET_TRANSMIT_DESCRIPTORS

◆ NVNET_TRANSMIT_HANG_THRESHOLD

◆ NvNetApplyInterruptMask

| #define NvNetApplyInterruptMask | ( | Adapter | ) | NV_WRITE(Adapter, NvRegIrqMask, (Adapter)->InterruptMask); |

◆ NvNetDisableInterrupts

| #define NvNetDisableInterrupts | ( | Adapter | ) | NV_WRITE(Adapter, NvRegIrqMask, 0); |

◆ NvNetLogError

| #define NvNetLogError | ( | Adapter, | |

| ErrorCode | |||

| ) | NdisWriteErrorLogEntry((Adapter)->AdapterHandle, ErrorCode, 1, __LINE__) |

◆ PACKET_ENTRY

| #define PACKET_ENTRY | ( | Packet | ) | ((PLIST_ENTRY)(&(Packet)->MiniportReserved[0])) |

Typedef Documentation

◆ NV_RBD

◆ NVNET_ADAPTER

| typedef struct _NVNET_ADAPTER NVNET_ADAPTER |

◆ NVNET_FLOW_CONTROL_MODE

◆ NVNET_OFFLOAD

| typedef union _NVNET_OFFLOAD NVNET_OFFLOAD |

◆ NVNET_OPTIMIZATION_MODE

◆ NVNET_PROCESS_RECEIVE

| typedef ULONG() NVNET_PROCESS_RECEIVE(_In_ PNVNET_ADAPTER Adapter, _In_ ULONG TotalRxProcessed) |

◆ NVNET_PROCESS_TRANSMIT

| typedef ULONG() NVNET_PROCESS_TRANSMIT(_In_ PNVNET_ADAPTER Adapter, _Inout_ PLIST_ENTRY SendReadyList) |

◆ NVNET_RBD

| typedef struct _NVNET_RBD NVNET_RBD |

◆ NVNET_RECEIVE

| typedef struct _NVNET_RECEIVE NVNET_RECEIVE |

◆ NVNET_SEND

| typedef struct _NVNET_SEND NVNET_SEND |

◆ NVNET_STATISTICS

| typedef struct _NVNET_STATISTICS NVNET_STATISTICS |

◆ NVNET_TBD

| typedef union _NVNET_TBD NVNET_TBD |

◆ NVNET_TCB

| typedef struct _NVNET_TCB NVNET_TCB |

◆ NVNET_TRANSMIT_PACKET

| typedef VOID() NVNET_TRANSMIT_PACKET(_In_ PNVNET_ADAPTER Adapter, _In_ PNVNET_TCB Tcb, _In_ PSCATTER_GATHER_LIST SgList) |

◆ NVNET_TX_BUFFER

| typedef struct _NVNET_TX_BUFFER NVNET_TX_BUFFER |

◆ NVNET_TX_BUFFER_DATA

◆ NVNET_WAKE_FRAME

| typedef struct _NVNET_WAKE_FRAME NVNET_WAKE_FRAME |

◆ PNVNET_ADAPTER

| typedef struct _NVNET_ADAPTER * PNVNET_ADAPTER |

◆ PNVNET_OFFLOAD

| typedef union _NVNET_OFFLOAD * PNVNET_OFFLOAD |

◆ PNVNET_PROCESS_RECEIVE

◆ PNVNET_PROCESS_TRANSMIT

◆ PNVNET_RBD

| typedef struct _NVNET_RBD * PNVNET_RBD |

◆ PNVNET_RECEIVE

| typedef struct _NVNET_RECEIVE * PNVNET_RECEIVE |

◆ PNVNET_SEND

| typedef struct _NVNET_SEND * PNVNET_SEND |

◆ PNVNET_STATISTICS

| typedef struct _NVNET_STATISTICS * PNVNET_STATISTICS |

◆ PNVNET_TCB

| typedef struct _NVNET_TCB * PNVNET_TCB |

◆ PNVNET_TRANSMIT_PACKET

◆ PNVNET_TX_BUFFER

| typedef struct _NVNET_TX_BUFFER * PNVNET_TX_BUFFER |

◆ PNVNET_TX_BUFFER_DATA

| typedef struct _NVNET_TX_BUFFER_DATA * PNVNET_TX_BUFFER_DATA |

◆ PNVNET_WAKE_FRAME

| typedef struct _NVNET_WAKE_FRAME * PNVNET_WAKE_FRAME |

Enumeration Type Documentation

◆ _NVNET_FLOW_CONTROL_MODE

| Enumerator | |

|---|---|

| NV_FLOW_CONTROL_DISABLE | |

| NV_FLOW_CONTROL_AUTO | |

| NV_FLOW_CONTROL_RX | |

| NV_FLOW_CONTROL_TX | |

| NV_FLOW_CONTROL_RX_TX | |

◆ _NVNET_OPTIMIZATION_MODE

| Enumerator | |

|---|---|

| NV_OPTIMIZATION_MODE_DYNAMIC | |

| NV_OPTIMIZATION_MODE_CPU | |

| NV_OPTIMIZATION_MODE_THROUGHPUT | |

Function Documentation

◆ MiiRead()

| BOOLEAN MiiRead | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ ULONG | PhyAddress, | ||

| _In_ ULONG | RegAddress, | ||

| _Out_ PULONG | Data | ||

| ) |

Definition at line 62 of file phy.c.

◆ MiiWrite()

| BOOLEAN MiiWrite | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ ULONG | PhyAddress, | ||

| _In_ ULONG | RegAddress, | ||

| _In_ ULONG | Data | ||

| ) |

◆ MiniportHandleInterrupt()

| VOID NTAPI MiniportHandleInterrupt | ( | _In_ NDIS_HANDLE | MiniportAdapterContext | ) |

Definition at line 449 of file interrupt.c.

◆ MiniportInitialize()

| NDIS_STATUS NTAPI MiniportInitialize | ( | _Out_ PNDIS_STATUS | OpenErrorStatus, |

| _Out_ PUINT | SelectedMediumIndex, | ||

| _In_ PNDIS_MEDIUM | MediumArray, | ||

| _In_ UINT | MediumArraySize, | ||

| _In_ NDIS_HANDLE | MiniportAdapterHandle, | ||

| _In_ NDIS_HANDLE | WrapperConfigurationContext | ||

| ) |

Definition at line 700 of file init.c.

◆ MiniportISR()

| VOID NTAPI MiniportISR | ( | _Out_ PBOOLEAN | InterruptRecognized, |

| _Out_ PBOOLEAN | QueueMiniportHandleInterrupt, | ||

| _In_ NDIS_HANDLE | MiniportAdapterContext | ||

| ) |

Definition at line 518 of file interrupt.c.

◆ MiniportQueryInformation()

| NDIS_STATUS NTAPI MiniportQueryInformation | ( | _In_ NDIS_HANDLE | MiniportAdapterContext, |

| _In_ NDIS_OID | Oid, | ||

| _In_ PVOID | InformationBuffer, | ||

| _In_ ULONG | InformationBufferLength, | ||

| _Out_ PULONG | BytesWritten, | ||

| _Out_ PULONG | BytesNeeded | ||

| ) |

Definition at line 974 of file requests.c.

◆ MiniportSend()

| NDIS_STATUS NTAPI MiniportSend | ( | _In_ NDIS_HANDLE | MiniportAdapterContext, |

| _In_ PNDIS_PACKET | Packet, | ||

| _In_ UINT | Flags | ||

| ) |

Definition at line 49 of file send.c.

◆ MiniportSetInformation()

| NDIS_STATUS NTAPI MiniportSetInformation | ( | _In_ NDIS_HANDLE | MiniportAdapterContext, |

| _In_ NDIS_OID | Oid, | ||

| _In_ PVOID | InformationBuffer, | ||

| _In_ ULONG | InformationBufferLength, | ||

| _Out_ PULONG | BytesRead, | ||

| _Out_ PULONG | BytesNeeded | ||

| ) |

Definition at line 1289 of file requests.c.

◆ NV_NEXT_TBD_32()

| FORCEINLINE NVNET_TBD NV_NEXT_TBD_32 | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ NVNET_TBD | Tbd | ||

| ) |

Definition at line 622 of file nvnet.h.

Referenced by NvNetTransmitPacket32().

◆ NV_NEXT_TBD_64()

| FORCEINLINE NVNET_TBD NV_NEXT_TBD_64 | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ NVNET_TBD | Tbd | ||

| ) |

Definition at line 634 of file nvnet.h.

Referenced by NvNetTransmitPacket64().

◆ NV_NEXT_TCB()

| FORCEINLINE PNVNET_TCB NV_NEXT_TCB | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ PNVNET_TCB | Tcb | ||

| ) |

Definition at line 610 of file nvnet.h.

Referenced by NvNetFlushTransmitQueue(), NvNetSendPacket(), NvNetSendPacketLargeSend(), ProcessTransmitDescriptors32(), ProcessTransmitDescriptors64(), and ProcessTransmitDescriptorsLegacy().

◆ NV_READ()

| FORCEINLINE ULONG NV_READ | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ NVNET_REGISTER | Register | ||

| ) |

Definition at line 656 of file nvnet.h.

Referenced by HandleLinkStateChange(), MiiRead(), MiiWrite(), MiniportHalt(), MiniportISR(), NvNetApplyPacketFilter(), NvNetBackoffReseed(), NvNetClearStatisticsCounters(), NvNetGetPermanentMacAddress(), NvNetIdleTransmitter(), NvNetInitNIC(), NvNetInitPhaseSynchronized(), NvNetPhyInit(), NvNetReadStatistics(), NvNetResetMac(), NvNetSetPowerState(), NvNetSetSpeedAndDuplex(), NvNetStartReceiver(), NvNetStartTransmitter(), NvNetStopReceiver(), NvNetStopTransmitter(), NvNetToggleClockPowerGating(), NvNetUpdatePauseFrame(), PhyInit(), PhyInitRealtek8211c(), SidebandUnitAcquireSemaphore(), SidebandUnitGetVersion(), and SidebandUnitReleaseSemaphore().

◆ NV_RELEASE_TCB()

| FORCEINLINE VOID NV_RELEASE_TCB | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ PNVNET_TCB | Tcb | ||

| ) |

Definition at line 590 of file nvnet.h.

Referenced by NvNetFlushTransmitQueue(), ProcessTransmitDescriptors32(), ProcessTransmitDescriptors64(), and ProcessTransmitDescriptorsLegacy().

◆ NV_WRITE()

| FORCEINLINE VOID NV_WRITE | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ NVNET_REGISTER | Register, | ||

| _In_ ULONG | Value | ||

| ) |

Definition at line 646 of file nvnet.h.

Referenced by HandleLinkStateChange(), MiiRead(), MiiWrite(), MiniportHalt(), MiniportInitialize(), MiniportISR(), MiniportShutdown(), NvNetApplyPacketFilter(), NvNetBackoffReseed(), NvNetBackoffReseedEx(), NvNetBackoffSetSlotTime(), NvNetGetPermanentMacAddress(), NvNetIdleTransmitter(), NvNetInitNIC(), NvNetInitPhaseSynchronized(), NvNetPhyInit(), NvNetPowerWorker(), NvNetResetMac(), NvNetResetReceiverAndTransmitter(), NvNetResetWorker(), NvNetSetPowerState(), NvNetSetSpeedAndDuplex(), NvNetSetTcpTaskOffload(), NvNetSetupMacAddress(), NvNetStartReceiver(), NvNetStartTransmitter(), NvNetStopReceiver(), NvNetStopTransmitter(), NvNetToggleClockPowerGating(), NvNetTransmitPacket32(), NvNetTransmitPacket64(), NvNetUpdatePauseFrame(), PhyInitRealtek8211c(), ProcessTransmitDescriptors64(), SidebandUnitAcquireSemaphore(), SidebandUnitGetVersion(), SidebandUnitReleaseSemaphore(), and WriteWakeFrame().

◆ NvNetBackoffReseed()

| VOID NvNetBackoffReseed | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 91 of file backoff.c.

Referenced by ProcessTransmitDescriptors32(), ProcessTransmitDescriptors64(), and ProcessTransmitDescriptorsLegacy().

◆ NvNetBackoffReseedEx()

| VOID NvNetBackoffReseedEx | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 125 of file backoff.c.

Referenced by NvNetBackoffSetSlotTime(), ProcessTransmitDescriptors32(), and ProcessTransmitDescriptors64().

◆ NvNetBackoffSetSlotTime()

| VOID NvNetBackoffSetSlotTime | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 58 of file backoff.c.

Referenced by NvNetInitNIC().

◆ NvNetFindPhyDevice()

| NDIS_STATUS NvNetFindPhyDevice | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

◆ NvNetFlushTransmitQueue()

| VOID NvNetFlushTransmitQueue | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ NDIS_STATUS | CompleteStatus | ||

| ) |

Definition at line 24 of file nvnet.c.

Referenced by MiniportHalt(), NvNetPowerWorker(), and NvNetResetWorker().

◆ NvNetFreeAdapter()

| VOID NvNetFreeAdapter | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 595 of file init.c.

Referenced by MiniportHalt(), and MiniportInitialize().

◆ NvNetGetPermanentMacAddress()

| NDIS_STATUS NvNetGetPermanentMacAddress | ( | _Inout_ PNVNET_ADAPTER | Adapter, |

| _Out_writes_bytes_all_(ETH_LENGTH_OF_ADDRESS) PUCHAR | MacAddress | ||

| ) |

Definition at line 541 of file nic.c.

Referenced by MiniportInitialize().

◆ NvNetIdleTransmitter()

| VOID NvNetIdleTransmitter | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ BOOLEAN | ClearPhyControl | ||

| ) |

Definition at line 211 of file nic.c.

Referenced by MiniportHalt(), MiniportShutdown(), NvNetPowerWorker(), and NvNetResetWorker().

◆ NvNetInitNIC()

| NDIS_STATUS NvNetInitNIC | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ BOOLEAN | InitPhy | ||

| ) |

Definition at line 401 of file nic.c.

Referenced by MiniportInitialize(), NvNetPowerWorker(), and NvNetResetWorker().

◆ NvNetPauseProcessing()

| DECLSPEC_NOINLINE VOID NvNetPauseProcessing | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 46 of file nvnet.c.

Referenced by MiniportHalt(), MiniportReset(), MiniportShutdown(), and NvNetPowerWorker().

◆ NvNetPhyInit()

| NDIS_STATUS NvNetPhyInit | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 1036 of file phy.c.

Referenced by NvNetInitNIC().

◆ NvNetRecognizeHardware()

| NDIS_STATUS NvNetRecognizeHardware | ( | _Inout_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 675 of file nic.c.

Referenced by MiniportInitialize().

◆ NvNetResetReceiverAndTransmitter()

| VOID NvNetResetReceiverAndTransmitter | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 91 of file nic.c.

Referenced by NvNetInitNIC().

◆ NvNetSetPowerState()

| VOID NvNetSetPowerState | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ NDIS_DEVICE_POWER_STATE | NewPowerState, | ||

| _In_ ULONG | WakeFlags | ||

| ) |

Definition at line 501 of file requests.c.

Referenced by MiniportShutdown(), and NvNetPowerWorker().

◆ NvNetSetupMacAddress()

| VOID NvNetSetupMacAddress | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_reads_bytes_(ETH_LENGTH_OF_ADDRESS) PUCHAR | MacAddress | ||

| ) |

Definition at line 622 of file nic.c.

Referenced by MiniportInitialize().

◆ NvNetStartAdapter()

| VOID NvNetStartAdapter | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 74 of file nvnet.c.

Referenced by MiniportInitialize(), NvNetPowerWorker(), and NvNetResetWorker().

◆ NvNetStartReceiver()

| VOID NvNetStartReceiver | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 104 of file nic.c.

Referenced by HandleLinkStateChange(), NvNetApplyPacketFilter(), NvNetBackoffReseed(), NvNetInitPhaseSynchronized(), NvNetMediaDetectionDpc(), NvNetSetPowerState(), and NvNetSetSpeedAndDuplex().

◆ NvNetStartTransmitter()

| VOID NvNetStartTransmitter | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 130 of file nic.c.

Referenced by NvNetBackoffReseed(), NvNetInitPhaseSynchronized(), and NvNetSetSpeedAndDuplex().

◆ NvNetStopAdapter()

| VOID NvNetStopAdapter | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 58 of file nvnet.c.

Referenced by MiniportHalt(), NvNetPowerWorker(), and NvNetResetWorker().

◆ NvNetStopReceiver()

| VOID NvNetStopReceiver | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 147 of file nic.c.

Referenced by HandleLinkStateChange(), MiniportHalt(), MiniportShutdown(), NvNetApplyPacketFilter(), NvNetBackoffReseed(), NvNetMediaDetectionDpc(), NvNetPowerWorker(), NvNetResetWorker(), and NvNetSetSpeedAndDuplex().

◆ NvNetStopTransmitter()

| VOID NvNetStopTransmitter | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 178 of file nic.c.

Referenced by MiniportHalt(), MiniportShutdown(), NvNetBackoffReseed(), NvNetPowerWorker(), NvNetResetWorker(), and NvNetSetSpeedAndDuplex().

◆ NvNetToggleClockPowerGating()

| VOID NvNetToggleClockPowerGating | ( | _In_ PNVNET_ADAPTER | Adapter, |

| _In_ BOOLEAN | Gate | ||

| ) |

Definition at line 294 of file nic.c.

Referenced by HandleLinkStateChange(), MiniportHalt(), NvNetInitNIC(), and NvNetMediaDetectionDpc().

◆ NvNetUpdateLinkSpeed()

| BOOLEAN NvNetUpdateLinkSpeed | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 990 of file phy.c.

Referenced by HandleLinkStateChange(), NvNetInitPhaseSynchronized(), and NvNetMediaDetectionDpc().

◆ NvNetUpdatePauseFrame()

| VOID NvNetUpdatePauseFrame | ( | _Inout_ PNVNET_ADAPTER | Adapter, |

| _In_ ULONG | PauseFlags | ||

| ) |

Definition at line 242 of file nic.c.

Referenced by NvNetSetSpeedAndDuplex().

◆ SidebandUnitReleaseSemaphore()

| VOID SidebandUnitReleaseSemaphore | ( | _In_ PNVNET_ADAPTER | Adapter | ) |

Definition at line 667 of file phy.c.

Referenced by MiniportHalt(), and MiniportShutdown().

Variable Documentation

◆ NvNetInitPhaseSynchronized

| KSYNCHRONIZE_ROUTINE NvNetInitPhaseSynchronized |

Definition at line 470 of file nvnet.h.

Referenced by NvNetStartAdapter().

◆ NvNetMediaDetectionDpc

| NDIS_TIMER_FUNCTION NvNetMediaDetectionDpc |

Definition at line 471 of file nvnet.h.

Referenced by NvNetRecognizeHardware().

◆ NvNetTransmitPacket32

| NVNET_TRANSMIT_PACKET NvNetTransmitPacket32 |

Definition at line 390 of file nvnet.h.

Referenced by MiniportInitialize().

◆ NvNetTransmitPacket64

| NVNET_TRANSMIT_PACKET NvNetTransmitPacket64 |

Definition at line 391 of file nvnet.h.

Referenced by MiniportInitialize().

◆ ProcessTransmitDescriptors32

| NVNET_PROCESS_TRANSMIT ProcessTransmitDescriptors32 |

Definition at line 393 of file nvnet.h.

Referenced by MiniportInitialize().

◆ ProcessTransmitDescriptors64

| NVNET_PROCESS_TRANSMIT ProcessTransmitDescriptors64 |

Definition at line 394 of file nvnet.h.

Referenced by MiniportInitialize().

◆ ProcessTransmitDescriptorsLegacy

| NVNET_PROCESS_TRANSMIT ProcessTransmitDescriptorsLegacy |

Definition at line 392 of file nvnet.h.

Referenced by MiniportInitialize().