nic.h File Reference

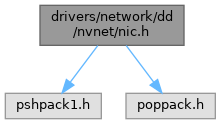

#include <pshpack1.h>#include <poppack.h>

Include dependency graph for nic.h:

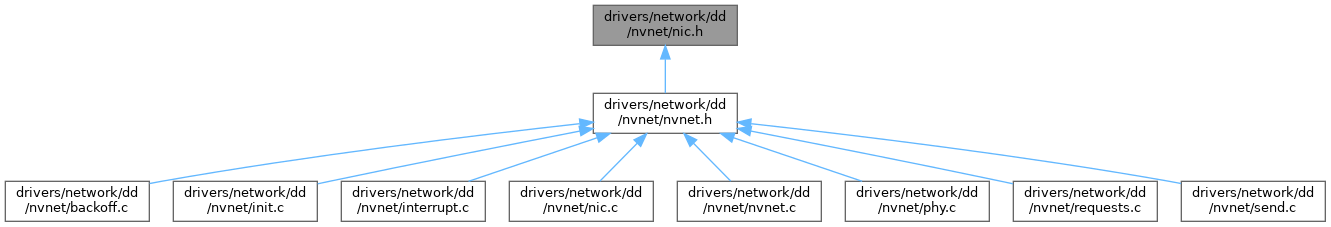

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | _NVNET_DESCRIPTOR_32 |

| struct | _NVNET_DESCRIPTOR_64 |

Typedefs | |

| typedef enum _NVNET_REGISTER | NVNET_REGISTER |

| typedef struct _NVNET_DESCRIPTOR_32 | NVNET_DESCRIPTOR_32 |

| typedef struct _NVNET_DESCRIPTOR_32 * | PNVNET_DESCRIPTOR_32 |

| typedef struct _NVNET_DESCRIPTOR_64 | NVNET_DESCRIPTOR_64 |

| typedef struct _NVNET_DESCRIPTOR_64 * | PNVNET_DESCRIPTOR_64 |

Macro Definition Documentation

◆ DEV_HAS_CHECKSUM

◆ DEV_HAS_COLLISION_FIX

◆ DEV_HAS_CORRECT_MACADDR

◆ DEV_HAS_GEAR_MODE

◆ DEV_HAS_HIGH_DMA

◆ DEV_HAS_LARGEDESC

| #define DEV_HAS_LARGEDESC |

◆ DEV_HAS_MGMT_UNIT

◆ DEV_HAS_MSI

◆ DEV_HAS_MSI_X

◆ DEV_HAS_PAUSEFRAME_TX_V1

◆ DEV_HAS_PAUSEFRAME_TX_V2

◆ DEV_HAS_PAUSEFRAME_TX_V3

◆ DEV_HAS_POWER_CNTRL

◆ DEV_HAS_STATISTICS_COUNTERS

| #define DEV_HAS_STATISTICS_COUNTERS |

Value:

◆ DEV_HAS_STATISTICS_V1

◆ DEV_HAS_STATISTICS_V2

◆ DEV_HAS_STATISTICS_V3

◆ DEV_HAS_TEST_EXTENDED

◆ DEV_HAS_TX_PAUSEFRAME

| #define DEV_HAS_TX_PAUSEFRAME |

Value:

◆ DEV_HAS_VLAN

◆ DEV_NEED_LINKTIMER

◆ DEV_NEED_LOW_POWER_FIX

◆ DEV_NEED_MSI_FIX

◆ DEV_NEED_PHY_INIT_FIX

◆ DEV_NEED_TIMERIRQ

◆ DEV_NEED_TX_LIMIT

◆ DEV_NEED_TX_LIMIT2

◆ FLAG_MASK_V1

◆ FLAG_MASK_V2

◆ LEN_MASK_V1

| #define LEN_MASK_V1 (0xffffffff ^ FLAG_MASK_V1) |

◆ LEN_MASK_V2

| #define LEN_MASK_V2 (0xffffffff ^ FLAG_MASK_V2) |

◆ NV_MAC_RESET_DELAY

◆ NV_MAXIMUM_SG_SIZE

| #define NV_MAXIMUM_SG_SIZE (1<<NV_TX2_TSO_MAX_SHIFT) |

◆ NV_MIIBUSY_DELAY

◆ NV_MIIPHY_DELAY

◆ NV_MIIPHY_DELAYMAX

◆ NV_MSI_CAPABLE

◆ NV_MSI_ENABLED

◆ NV_MSI_PRIV_OFFSET

◆ NV_MSI_PRIV_VALUE

◆ NV_MSI_X_CAPABLE

◆ NV_MSI_X_ENABLED

◆ NV_MSI_X_MAX_VECTORS

◆ NV_MSI_X_VECTOR_ALL

◆ NV_MSI_X_VECTOR_OTHER

◆ NV_MSI_X_VECTOR_RX

◆ NV_MSI_X_VECTOR_TX

◆ NV_MSI_X_VECTORS_MASK

◆ NV_PATTERN_V2_OFFSET

◆ NV_PAUSEFRAME_AUTONEG

◆ NV_PAUSEFRAME_RX_CAPABLE

◆ NV_PAUSEFRAME_RX_ENABLE

◆ NV_PAUSEFRAME_RX_REQ

◆ NV_PAUSEFRAME_TX_CAPABLE

◆ NV_PAUSEFRAME_TX_ENABLE

◆ NV_PAUSEFRAME_TX_REQ

◆ NV_POWER_ATTEMPTS

◆ NV_POWER_DELAY

◆ NV_POWER_STALL

◆ NV_POWERUP_DELAY

◆ NV_POWERUP_DELAYMAX

◆ NV_RX2_AVAIL

◆ NV_RX2_CHECKSUM_IP

◆ NV_RX2_CHECKSUM_IP_TCP

◆ NV_RX2_CHECKSUM_IP_UDP

◆ NV_RX2_CHECKSUMMASK

◆ NV_RX2_CRCERR

◆ NV_RX2_DESCRIPTORVALID

◆ NV_RX2_ERROR

◆ NV_RX2_ERROR1

◆ NV_RX2_ERROR2

◆ NV_RX2_ERROR3

◆ NV_RX2_ERROR4

◆ NV_RX2_ERROR_MASK

| #define NV_RX2_ERROR_MASK |

Value:

◆ NV_RX2_FRAMINGERR

◆ NV_RX2_OVERFLOW

◆ NV_RX2_SUBTRACT1

◆ NV_RX3_VLAN_TAG_MASK

◆ NV_RX3_VLAN_TAG_PRESENT

◆ NV_RX_ALLOC_PAD

◆ NV_RX_AVAIL

◆ NV_RX_CRCERR

◆ NV_RX_DESCRIPTORVALID

◆ NV_RX_ERROR

◆ NV_RX_ERROR1

◆ NV_RX_ERROR2

◆ NV_RX_ERROR3

◆ NV_RX_ERROR4

◆ NV_RX_ERROR_MASK

| #define NV_RX_ERROR_MASK |

Value:

◆ NV_RX_FRAMINGERR

◆ NV_RX_HEADERS

◆ NV_RX_MISSEDFRAME

◆ NV_RX_OVERFLOW

◆ NV_RX_SUBTRACT1

◆ NV_RXSTOP_DELAY1

◆ NV_RXSTOP_DELAY1MAX

◆ NV_RXSTOP_DELAY2

◆ NV_SETUP5_DELAY

◆ NV_SETUP5_DELAYMAX

◆ NV_TX2_CARRIERLOST

◆ NV_TX2_CHECKSUM_L3

◆ NV_TX2_CHECKSUM_L4

◆ NV_TX2_DEFERRED

◆ NV_TX2_ERROR

◆ NV_TX2_FORCED_INTERRUPT

◆ NV_TX2_LASTPACKET

◆ NV_TX2_LATECOLLISION

◆ NV_TX2_RETRYCOUNT_MASK

◆ NV_TX2_RETRYERROR

◆ NV_TX2_TSO

◆ NV_TX2_TSO_MAX_SHIFT

◆ NV_TX2_TSO_SHIFT

◆ NV_TX2_UNDERFLOW

◆ NV_TX2_VALID

◆ NV_TX3_VLAN_TAG_PRESENT

◆ NV_TX_CARRIERLOST

◆ NV_TX_DEFERRED

◆ NV_TX_ERROR

◆ NV_TX_FORCED_INTERRUPT

◆ NV_TX_LASTPACKET

◆ NV_TX_LATECOLLISION

◆ NV_TX_LIMIT_COUNT

◆ NV_TX_ONE_RETRY

◆ NV_TX_RETRYCOUNT_MASK

◆ NV_TX_RETRYERROR

◆ NV_TX_UNDERFLOW

◆ NV_TX_VALID

◆ NV_TXIDLE_ATTEMPTS

◆ NV_TXIDLE_DELAY

◆ NV_TXRX_RESET_DELAY

◆ NV_TXSTOP_DELAY1

◆ NV_TXSTOP_DELAY1MAX

◆ NV_TXSTOP_DELAY2

◆ NV_WAKEUPMASKENTRIES

◆ NV_WAKEUPPATTERNS

◆ NV_WAKEUPPATTERNS_V2

◆ NVREG_ADAPTCTL_LINKUP

◆ NVREG_ADAPTCTL_PHYSHIFT

◆ NVREG_ADAPTCTL_PHYVALID

◆ NVREG_ADAPTCTL_RUNNING

◆ NVREG_ADAPTCTL_START

◆ NVREG_BKOFFCTRL_DEFAULT

◆ NVREG_BKOFFCTRL_GEAR

◆ NVREG_BKOFFCTRL_SEED_MASK

◆ NVREG_BKOFFCTRL_SELECT

◆ NVREG_IRQ_LINK

◆ NVREG_IRQ_OTHER

| #define NVREG_IRQ_OTHER (NVREG_IRQ_TIMER|NVREG_IRQ_LINK|NVREG_IRQ_RECOVER_ERROR) |

◆ NVREG_IRQ_RECOVER_ERROR

◆ NVREG_IRQ_RX

◆ NVREG_IRQ_RX_ALL

| #define NVREG_IRQ_RX_ALL |

Value:

◆ NVREG_IRQ_RX_ERROR

◆ NVREG_IRQ_RX_FORCED

◆ NVREG_IRQ_RX_NOBUF

◆ NVREG_IRQ_TIMER

◆ NVREG_IRQ_TX_ALL

| #define NVREG_IRQ_TX_ALL (NVREG_IRQ_TX_ERR|NVREG_IRQ_TX_OK|NVREG_IRQ_TX_FORCED) |

◆ NVREG_IRQ_TX_ERR

◆ NVREG_IRQ_TX_FORCED

◆ NVREG_IRQ_TX_OK

◆ NVREG_IRQMASK_CPU

◆ NVREG_IRQMASK_THROUGHPUT

◆ NVREG_IRQSTAT_MASK

◆ NVREG_IRQSTAT_MIIEVENT

◆ NVREG_LINKSPEED_10

◆ NVREG_LINKSPEED_100

◆ NVREG_LINKSPEED_1000

◆ NVREG_LINKSPEED_FORCE

◆ NVREG_LINKSPEED_MASK

◆ NVREG_MAC_RESET_ASSERT

◆ NVREG_MCASTADDRA_FORCE

◆ NVREG_MCASTMASKA_NONE

◆ NVREG_MCASTMASKB_NONE

◆ NVREG_MGMTUNITCONTROL_INUSE

◆ NVREG_MGMTUNITGETVERSION

◆ NVREG_MGMTUNITVERSION

◆ NVREG_MII_LINKCHANGE

◆ NVREG_MIICTL_ADDRSHIFT

◆ NVREG_MIICTL_INUSE

◆ NVREG_MIICTL_WRITE

◆ NVREG_MIIDELAY

◆ NVREG_MIISPEED_BIT8

◆ NVREG_MIISTAT_ERROR

◆ NVREG_MIISTAT_LINKCHANGE

◆ NVREG_MIISTAT_MASK_ALL

◆ NVREG_MIISTAT_MASK_RW

◆ NVREG_MISC1_FORCE

◆ NVREG_MISC1_HD

◆ NVREG_MISC1_PAUSE_TX

◆ NVREG_MSI_VECTOR_0_ENABLED

◆ NVREG_OFFLOAD_HOMEPHY

◆ NVREG_OFFLOAD_NORMAL

◆ NVREG_PFF_ALWAYS

◆ NVREG_PFF_LOOPBACK

◆ NVREG_PFF_MYADDR

◆ NVREG_PFF_PAUSE_RX

◆ NVREG_PFF_PROMISC

◆ NVREG_POLL_DEFAULT_CPU

◆ NVREG_POLL_DEFAULT_THROUGHPUT

◆ NVREG_POWERCAP_D1SUPP

◆ NVREG_POWERCAP_D2SUPP

◆ NVREG_POWERCAP_D3SUPP

◆ NVREG_POWERSTATE2_GATE_CLOCK_1

◆ NVREG_POWERSTATE2_GATE_CLOCK_2

◆ NVREG_POWERSTATE2_GATE_CLOCK_3

◆ NVREG_POWERSTATE2_GATE_CLOCKS

◆ NVREG_POWERSTATE2_PHY_RESET

◆ NVREG_POWERSTATE2_POWERUP_MASK

◆ NVREG_POWERSTATE2_POWERUP_REV_A3

◆ NVREG_POWERSTATE2_WAKEUPPAT_5

◆ NVREG_POWERSTATE2_WAKEUPPAT_6

◆ NVREG_POWERSTATE2_WAKEUPPAT_7

◆ NVREG_POWERSTATE_D0

◆ NVREG_POWERSTATE_D1

◆ NVREG_POWERSTATE_D2

◆ NVREG_POWERSTATE_D3

◆ NVREG_POWERSTATE_MASK

◆ NVREG_POWERSTATE_POWEREDUP

◆ NVREG_POWERSTATE_VALID

◆ NVREG_RCVCTL_RX_PATH_EN

◆ NVREG_RCVCTL_START

◆ NVREG_RCVSTAT_BUSY

◆ NVREG_RINGSZ_RXSHIFT

◆ NVREG_RINGSZ_TXSHIFT

◆ NVREG_RX_DEFERRAL_DEFAULT

◆ NVREG_SLOTTIME_1000_FULL

◆ NVREG_SLOTTIME_10_100_FULL

◆ NVREG_SLOTTIME_DEFAULT

◆ NVREG_SLOTTIME_HALF

◆ NVREG_SLOTTIME_LEGBF_ENABLED

◆ NVREG_SLOTTIME_MASK

◆ NVREG_TRANSMITPOLL_MAC_ADDR_REV

◆ NVREG_TX_DEFERRAL_DEFAULT

◆ NVREG_TX_DEFERRAL_MII_STRETCH

◆ NVREG_TX_DEFERRAL_RGMII_1000

◆ NVREG_TX_DEFERRAL_RGMII_10_100

◆ NVREG_TX_DEFERRAL_RGMII_STRETCH_10

◆ NVREG_TX_DEFERRAL_RGMII_STRETCH_100

◆ NVREG_TX_PAUSEFRAME_DISABLE

◆ NVREG_TX_PAUSEFRAME_ENABLE_V1

◆ NVREG_TX_PAUSEFRAME_ENABLE_V2

◆ NVREG_TX_PAUSEFRAME_ENABLE_V3

◆ NVREG_TX_PAUSEFRAMELIMIT_ENABLE

◆ NVREG_TX_WM_DESC1_DEFAULT

◆ NVREG_TX_WM_DESC2_3_1000

◆ NVREG_TX_WM_DESC2_3_DEFAULT

◆ NVREG_TXRXCTL_BIT1

◆ NVREG_TXRXCTL_BIT2

◆ NVREG_TXRXCTL_DESC_1

◆ NVREG_TXRXCTL_DESC_2

◆ NVREG_TXRXCTL_DESC_3

◆ NVREG_TXRXCTL_IDLE

◆ NVREG_TXRXCTL_KICK

◆ NVREG_TXRXCTL_RESET

◆ NVREG_TXRXCTL_RXCHECK

◆ NVREG_TXRXCTL_VLANINS

◆ NVREG_TXRXCTL_VLANSTRIP

◆ NVREG_UNKSETUP5_BIT31

◆ NVREG_UNKSETUP6_VAL

◆ NVREG_VLANCONTROL_ENABLE

◆ NVREG_WAKEUPFLAGS_ACCEPT_LINKCHANGE

◆ NVREG_WAKEUPFLAGS_ACCEPT_MAGPAT

◆ NVREG_WAKEUPFLAGS_ACCEPT_WAKEUPPAT

◆ NVREG_WAKEUPFLAGS_BUSYSHIFT

◆ NVREG_WAKEUPFLAGS_D0SHIFT

◆ NVREG_WAKEUPFLAGS_D1SHIFT

◆ NVREG_WAKEUPFLAGS_D2SHIFT

◆ NVREG_WAKEUPFLAGS_D3SHIFT

◆ NVREG_WAKEUPFLAGS_ENABLE_LINKCHANGE

◆ NVREG_WAKEUPFLAGS_ENABLE_MAGPAT

◆ NVREG_WAKEUPFLAGS_ENABLE_WAKEUPPAT

◆ NVREG_WAKEUPFLAGS_ENABLESHIFT

◆ NVREG_WAKEUPFLAGS_VAL

◆ NVREG_XMITCTL_DATA_ERROR

◆ NVREG_XMITCTL_DATA_READY

◆ NVREG_XMITCTL_DATA_START

◆ NVREG_XMITCTL_HOST_LOADED

◆ NVREG_XMITCTL_HOST_SEMA_ACQ

◆ NVREG_XMITCTL_HOST_SEMA_MASK

◆ NVREG_XMITCTL_MGMT_SEMA_FREE

◆ NVREG_XMITCTL_MGMT_SEMA_MASK

◆ NVREG_XMITCTL_MGMT_ST

◆ NVREG_XMITCTL_START

◆ NVREG_XMITCTL_SYNC_MASK

◆ NVREG_XMITCTL_SYNC_NOT_READY

◆ NVREG_XMITCTL_SYNC_PHY_INIT

◆ NVREG_XMITCTL_TX_PATH_EN

◆ NVREG_XMITSTAT_BUSY

◆ PHY_100

◆ PHY_1000

◆ PHY_CICADA_INIT1

◆ PHY_CICADA_INIT2

◆ PHY_CICADA_INIT3

◆ PHY_CICADA_INIT4

◆ PHY_CICADA_INIT5

◆ PHY_CICADA_INIT6

◆ PHY_CICADA_INIT_REG1

◆ PHY_CICADA_INIT_REG2

◆ PHY_CICADA_INIT_REG3

◆ PHY_GIGABIT

◆ PHY_HALF

◆ PHY_MARVELL_E3016_INITMASK

◆ PHY_MARVELL_INIT_REG1

◆ PHY_MODEL_MARVELL_E3016

◆ PHY_MODEL_REALTEK_8201

◆ PHY_MODEL_REALTEK_8211

◆ PHY_OUI_CICADA

◆ PHY_OUI_MARVELL

◆ PHY_OUI_REALTEK

◆ PHY_OUI_REALTEK2

◆ PHY_OUI_VITESSE

◆ PHY_REALTEK_INIT1

◆ PHY_REALTEK_INIT10

◆ PHY_REALTEK_INIT11

◆ PHY_REALTEK_INIT2

◆ PHY_REALTEK_INIT3

◆ PHY_REALTEK_INIT4

◆ PHY_REALTEK_INIT5

◆ PHY_REALTEK_INIT6

◆ PHY_REALTEK_INIT7

◆ PHY_REALTEK_INIT8

◆ PHY_REALTEK_INIT9

◆ PHY_REALTEK_INIT_MSK1

◆ PHY_REALTEK_INIT_REG1

◆ PHY_REALTEK_INIT_REG2

◆ PHY_REALTEK_INIT_REG3

◆ PHY_REALTEK_INIT_REG4

◆ PHY_REALTEK_INIT_REG5

◆ PHY_REALTEK_INIT_REG6

◆ PHY_REALTEK_INIT_REG7

◆ PHY_REALTEK_REVISION

◆ PHY_REV_MASK

◆ PHY_REV_REALTEK_8211B

◆ PHY_REV_REALTEK_8211C

◆ PHY_RGMII

◆ PHY_VITESSE_INIT1

◆ PHY_VITESSE_INIT10

◆ PHY_VITESSE_INIT2

◆ PHY_VITESSE_INIT3

◆ PHY_VITESSE_INIT4

◆ PHY_VITESSE_INIT5

◆ PHY_VITESSE_INIT6

◆ PHY_VITESSE_INIT7

◆ PHY_VITESSE_INIT8

◆ PHY_VITESSE_INIT9

◆ PHY_VITESSE_INIT_MSK1

◆ PHY_VITESSE_INIT_MSK2

◆ PHY_VITESSE_INIT_REG1

◆ PHY_VITESSE_INIT_REG2

◆ PHY_VITESSE_INIT_REG3

◆ PHY_VITESSE_INIT_REG4

◆ PHYID1_OUI_MASK

◆ PHYID1_OUI_SHFT

◆ PHYID2_MODEL_MASK

◆ PHYID2_OUI_MASK

◆ PHYID2_OUI_SHFT

Typedef Documentation

◆ NVNET_DESCRIPTOR_32

◆ NVNET_DESCRIPTOR_64

◆ NVNET_REGISTER

| typedef enum _NVNET_REGISTER NVNET_REGISTER |

◆ PNVNET_DESCRIPTOR_32

| typedef struct _NVNET_DESCRIPTOR_32 * PNVNET_DESCRIPTOR_32 |

◆ PNVNET_DESCRIPTOR_64

| typedef struct _NVNET_DESCRIPTOR_64 * PNVNET_DESCRIPTOR_64 |

Enumeration Type Documentation

◆ _NVNET_REGISTER

Definition at line 49 of file nic.h.

51{

52 NvRegIrqStatus = 0x000,

53#define NVREG_IRQSTAT_MIIEVENT 0x040

54#define NVREG_IRQSTAT_MASK 0x83ff

55

56 NvRegIrqMask = 0x004,

57#define NVREG_IRQ_RX_ERROR 0x0001

58#define NVREG_IRQ_RX 0x0002

59#define NVREG_IRQ_RX_NOBUF 0x0004

60#define NVREG_IRQ_TX_ERR 0x0008

61#define NVREG_IRQ_TX_OK 0x0010

62#define NVREG_IRQ_TIMER 0x0020

63#define NVREG_IRQ_LINK 0x0040

64#define NVREG_IRQ_RX_FORCED 0x0080

65#define NVREG_IRQ_TX_FORCED 0x0100

66#define NVREG_IRQ_RECOVER_ERROR 0x8200

67#define NVREG_IRQMASK_THROUGHPUT 0x00df

68#define NVREG_IRQMASK_CPU 0x0060

69#define NVREG_IRQ_TX_ALL (NVREG_IRQ_TX_ERR|NVREG_IRQ_TX_OK|NVREG_IRQ_TX_FORCED)

70#define NVREG_IRQ_RX_ALL (NVREG_IRQ_RX_ERROR|NVREG_IRQ_RX|NVREG_IRQ_RX_NOBUF| \

71 NVREG_IRQ_RX_FORCED)

72#define NVREG_IRQ_OTHER (NVREG_IRQ_TIMER|NVREG_IRQ_LINK|NVREG_IRQ_RECOVER_ERROR)

73

74 NvRegUnknownSetupReg6 = 0x008,

75#define NVREG_UNKSETUP6_VAL 3

76

77 NvRegPollingInterval = 0x00c,

78#define NVREG_POLL_DEFAULT_THROUGHPUT 65535

79#define NVREG_POLL_DEFAULT_CPU 13

80

81 NvRegMSIMap0 = 0x020,

82 NvRegMSIMap1 = 0x024,

83

84 NvRegMSIIrqMask = 0x030,

85#define NVREG_MSI_VECTOR_0_ENABLED 0x01

86

87 NvRegMacReset = 0x34,

88#define NVREG_MAC_RESET_ASSERT 0x0F3

89

90 NvRegMisc1 = 0x080,

91#define NVREG_MISC1_PAUSE_TX 0x01

92#define NVREG_MISC1_HD 0x02

93#define NVREG_MISC1_FORCE 0x3b0f3c

94

95 NvRegTransmitterControl = 0x084,

96#define NVREG_XMITCTL_START 0x01

97#define NVREG_XMITCTL_MGMT_ST 0x40000000

98#define NVREG_XMITCTL_SYNC_MASK 0x000f0000

99#define NVREG_XMITCTL_SYNC_NOT_READY 0x0

100#define NVREG_XMITCTL_SYNC_PHY_INIT 0x00040000

101#define NVREG_XMITCTL_MGMT_SEMA_MASK 0x00000f00

102#define NVREG_XMITCTL_MGMT_SEMA_FREE 0x0

103#define NVREG_XMITCTL_HOST_SEMA_MASK 0x0000f000

104#define NVREG_XMITCTL_HOST_SEMA_ACQ 0x0000f000

105#define NVREG_XMITCTL_HOST_LOADED 0x00004000

106#define NVREG_XMITCTL_TX_PATH_EN 0x01000000

107#define NVREG_XMITCTL_DATA_START 0x00100000

108#define NVREG_XMITCTL_DATA_READY 0x00010000

109#define NVREG_XMITCTL_DATA_ERROR 0x00020000

110

111 NvRegTransmitterStatus = 0x088,

112#define NVREG_XMITSTAT_BUSY 0x01

113

114 NvRegPacketFilterFlags = 0x8c,

115#define NVREG_PFF_PAUSE_RX 0x08

116#define NVREG_PFF_ALWAYS 0x7F0000

117#define NVREG_PFF_PROMISC 0x80

118#define NVREG_PFF_MYADDR 0x20

119#define NVREG_PFF_LOOPBACK 0x10

120

121 NvRegOffloadConfig = 0x90,

122#define NVREG_OFFLOAD_HOMEPHY 0x601

123#define NVREG_OFFLOAD_NORMAL RX_NIC_BUFSIZE

124

125 NvRegReceiverControl = 0x094,

126#define NVREG_RCVCTL_START 0x01

127#define NVREG_RCVCTL_RX_PATH_EN 0x01000000

128

129 NvRegReceiverStatus = 0x98,

130#define NVREG_RCVSTAT_BUSY 0x01

131

132 NvRegSlotTime = 0x9c,

133#define NVREG_SLOTTIME_LEGBF_ENABLED 0x80000000

134#define NVREG_SLOTTIME_10_100_FULL 0x00007f00

135#define NVREG_SLOTTIME_1000_FULL 0x0003ff00

136#define NVREG_SLOTTIME_HALF 0x0000ff00

137#define NVREG_SLOTTIME_DEFAULT 0x00007f00

138#define NVREG_SLOTTIME_MASK 0x000000ff

139

140 NvRegTxDeferral = 0xA0,

141#define NVREG_TX_DEFERRAL_DEFAULT 0x15050f

142#define NVREG_TX_DEFERRAL_RGMII_10_100 0x16070f

143#define NVREG_TX_DEFERRAL_RGMII_1000 0x14050f

144#define NVREG_TX_DEFERRAL_RGMII_STRETCH_10 0x16190f

145#define NVREG_TX_DEFERRAL_RGMII_STRETCH_100 0x16300f

146#define NVREG_TX_DEFERRAL_MII_STRETCH 0x152000

147

148 NvRegRxDeferral = 0xA4,

149#define NVREG_RX_DEFERRAL_DEFAULT 0x16

150

151 NvRegMacAddrA = 0xA8,

152 NvRegMacAddrB = 0xAC,

153

154 NvRegMulticastAddrA = 0xB0,

155 NvRegMulticastAddrB = 0xB4,

156#define NVREG_MCASTADDRA_FORCE 0x01

157

158 NvRegMulticastMaskA = 0xB8,

159#define NVREG_MCASTMASKA_NONE 0xffffffff

160

161 NvRegMulticastMaskB = 0xBC,

162#define NVREG_MCASTMASKB_NONE 0xffff

163

164 NvRegPhyInterface = 0xC0,

165#define PHY_100 0x1

166#define PHY_1000 0x2

167#define PHY_HALF 0x100

168#define PHY_RGMII 0x10000000

169

170 NvRegBackOffControl = 0xC4,

171#define NVREG_BKOFFCTRL_DEFAULT 0x70000000

172#define NVREG_BKOFFCTRL_SEED_MASK 0x000003ff

173#define NVREG_BKOFFCTRL_SELECT 24

174#define NVREG_BKOFFCTRL_GEAR 12

175

176 NvRegTxRingPhysAddr = 0x100,

177 NvRegRxRingPhysAddr = 0x104,

178

179 NvRegRingSizes = 0x108,

180#define NVREG_RINGSZ_TXSHIFT 0

181#define NVREG_RINGSZ_RXSHIFT 16

182

183 NvRegTransmitPoll = 0x10c,

184#define NVREG_TRANSMITPOLL_MAC_ADDR_REV 0x00008000

185

186 NvRegLinkSpeed = 0x110,

187#define NVREG_LINKSPEED_FORCE 0x10000

188#define NVREG_LINKSPEED_10 1000

189#define NVREG_LINKSPEED_100 100

190#define NVREG_LINKSPEED_1000 50

191#define NVREG_LINKSPEED_MASK (0xFFF)

192

193 NvRegUnknownSetupReg5 = 0x130,

194#define NVREG_UNKSETUP5_BIT31 (1<<31)

195

196 NvRegTxWatermark = 0x13c,

197#define NVREG_TX_WM_DESC1_DEFAULT 0x0200010

198#define NVREG_TX_WM_DESC2_3_DEFAULT 0x1e08000

199#define NVREG_TX_WM_DESC2_3_1000 0xfe08000

200

201 NvRegTxRxControl = 0x144,

202#define NVREG_TXRXCTL_KICK 0x0001

203#define NVREG_TXRXCTL_BIT1 0x0002

204#define NVREG_TXRXCTL_BIT2 0x0004

205#define NVREG_TXRXCTL_IDLE 0x0008

206#define NVREG_TXRXCTL_RESET 0x0010

207#define NVREG_TXRXCTL_RXCHECK 0x0400

208#define NVREG_TXRXCTL_DESC_1 0

209#define NVREG_TXRXCTL_DESC_2 0x002100

210#define NVREG_TXRXCTL_DESC_3 0xc02200

211#define NVREG_TXRXCTL_VLANSTRIP 0x00040

212#define NVREG_TXRXCTL_VLANINS 0x00080

213

214 NvRegTxRingPhysAddrHigh = 0x148,

215 NvRegRxRingPhysAddrHigh = 0x14C,

216

217 NvRegTxPauseFrame = 0x170,

218#define NVREG_TX_PAUSEFRAME_DISABLE 0x0fff0080

219#define NVREG_TX_PAUSEFRAME_ENABLE_V1 0x01800010

220#define NVREG_TX_PAUSEFRAME_ENABLE_V2 0x056003f0

221#define NVREG_TX_PAUSEFRAME_ENABLE_V3 0x09f00880

222

223 NvRegTxPauseFrameLimit = 0x174,

224#define NVREG_TX_PAUSEFRAMELIMIT_ENABLE 0x00010000

225

226 NvRegMIIStatus = 0x180,

227#define NVREG_MIISTAT_ERROR 0x0001

228#define NVREG_MIISTAT_LINKCHANGE 0x0008

229#define NVREG_MIISTAT_MASK_RW 0x0007

230#define NVREG_MIISTAT_MASK_ALL 0x000f

231

232 NvRegMIIMask = 0x184,

233#define NVREG_MII_LINKCHANGE 0x0008

234

235 NvRegAdapterControl = 0x188,

236#define NVREG_ADAPTCTL_START 0x02

237#define NVREG_ADAPTCTL_LINKUP 0x04

238#define NVREG_ADAPTCTL_PHYVALID 0x40000

239#define NVREG_ADAPTCTL_RUNNING 0x100000

240#define NVREG_ADAPTCTL_PHYSHIFT 24

241

242 NvRegMIISpeed = 0x18c,

243#define NVREG_MIISPEED_BIT8 (1<<8)

244#define NVREG_MIIDELAY 5

245

246 NvRegMIIControl = 0x190,

247#define NVREG_MIICTL_INUSE 0x08000

248#define NVREG_MIICTL_WRITE 0x00400

249#define NVREG_MIICTL_ADDRSHIFT 5

250

251 NvRegMIIData = 0x194,

252 NvRegTxUnicast = 0x1a0,

253 NvRegTxMulticast = 0x1a4,

254 NvRegTxBroadcast = 0x1a8,

255

256 NvRegWakeUpFlags = 0x200,

257#define NVREG_WAKEUPFLAGS_VAL 0x7770

258#define NVREG_WAKEUPFLAGS_BUSYSHIFT 24

259#define NVREG_WAKEUPFLAGS_ENABLESHIFT 16

260#define NVREG_WAKEUPFLAGS_D3SHIFT 12

261#define NVREG_WAKEUPFLAGS_D2SHIFT 8

262#define NVREG_WAKEUPFLAGS_D1SHIFT 4

263#define NVREG_WAKEUPFLAGS_D0SHIFT 0

264#define NVREG_WAKEUPFLAGS_ACCEPT_MAGPAT 0x01

265#define NVREG_WAKEUPFLAGS_ACCEPT_WAKEUPPAT 0x02

266#define NVREG_WAKEUPFLAGS_ACCEPT_LINKCHANGE 0x04

267#define NVREG_WAKEUPFLAGS_ENABLE_MAGPAT 0x1111

268#define NVREG_WAKEUPFLAGS_ENABLE_WAKEUPPAT 0x2222

269#define NVREG_WAKEUPFLAGS_ENABLE_LINKCHANGE 0x4444

270

271 NvRegPatternCrc = 0x204,

272 NvRegPatternMask0 = 0x208,

273 NvRegPatternMask1 = 0x20C,

274 NvRegPatternMask2 = 0x210,

275 NvRegPatternMask3 = 0x214,

276

277 NvRegMgmtUnitGetVersion = 0x204,

278#define NVREG_MGMTUNITGETVERSION 0x01

279

280 NvRegMgmtUnitVersion = 0x208,

281#define NVREG_MGMTUNITVERSION 0x08

282

283 NvRegPowerCap = 0x268,

284#define NVREG_POWERCAP_D3SUPP (1<<30)

285#define NVREG_POWERCAP_D2SUPP (1<<26)

286#define NVREG_POWERCAP_D1SUPP (1<<25)

287

288 NvRegPowerState = 0x26c,

289#define NVREG_POWERSTATE_POWEREDUP 0x8000

290#define NVREG_POWERSTATE_VALID 0x0100

291#define NVREG_POWERSTATE_MASK 0x0003

292#define NVREG_POWERSTATE_D0 0x0000

293#define NVREG_POWERSTATE_D1 0x0001

294#define NVREG_POWERSTATE_D2 0x0002

295#define NVREG_POWERSTATE_D3 0x0003

296

297 NvRegMgmtUnitControl = 0x278,

298#define NVREG_MGMTUNITCONTROL_INUSE 0x20000

299

300 NvRegTxCnt = 0x280,

301 NvRegTxZeroReXmt = 0x284,

302 NvRegTxOneReXmt = 0x288,

303 NvRegTxManyReXmt = 0x28c,

304 NvRegTxLateCol = 0x290,

305 NvRegTxUnderflow = 0x294,

306 NvRegTxLossCarrier = 0x298,

307 NvRegTxExcessDef = 0x29c,

308 NvRegTxRetryErr = 0x2a0,

309 NvRegRxFrameErr = 0x2a4,

310 NvRegRxExtraByte = 0x2a8,

311 NvRegRxLateCol = 0x2ac,

312 NvRegRxRunt = 0x2b0,

313 NvRegRxFrameTooLong = 0x2b4,

314 NvRegRxOverflow = 0x2b8,

315 NvRegRxFCSErr = 0x2bc,

316 NvRegRxFrameAlignErr = 0x2c0,

317 NvRegRxLenErr = 0x2c4,

318 NvRegRxUnicast = 0x2c8,

319 NvRegRxMulticast = 0x2cc,

320 NvRegRxBroadcast = 0x2d0,

321 NvRegTxDef = 0x2d4,

322 NvRegTxFrame = 0x2d8,

323 NvRegRxCnt = 0x2dc,

324 NvRegTxPause = 0x2e0,

325 NvRegRxPause = 0x2e4,

326 NvRegRxDropFrame = 0x2e8,

327

328 NvRegVlanControl = 0x300,

329#define NVREG_VLANCONTROL_ENABLE 0x2000

330

331 NvRegMSIXMap0 = 0x3e0,

332 NvRegMSIXMap1 = 0x3e4,

333 NvRegMSIXIrqStatus = 0x3f0,

334

335 NvRegPowerState2 = 0x600,

336#define NVREG_POWERSTATE2_POWERUP_MASK 0x0F15

337#define NVREG_POWERSTATE2_POWERUP_REV_A3 0x0001

338#define NVREG_POWERSTATE2_PHY_RESET 0x0004

339#define NVREG_POWERSTATE2_GATE_CLOCK_1 0x0100

340#define NVREG_POWERSTATE2_GATE_CLOCK_2 0x0200

341#define NVREG_POWERSTATE2_GATE_CLOCK_3 0x0400

342#define NVREG_POWERSTATE2_GATE_CLOCKS 0x0F00

343#define NVREG_POWERSTATE2_WAKEUPPAT_5 (1<<16)

344#define NVREG_POWERSTATE2_WAKEUPPAT_6 (1<<17)

345#define NVREG_POWERSTATE2_WAKEUPPAT_7 (1<<18)

346

347 NvRegPatternCrcEx = 0x604,

348 NvRegPatternMask0Ex = 0x608,

349 NvRegPatternMask1Ex = 0x60C,

350 NvRegPatternMask2Ex = 0x610,

351 NvRegPatternMask3Ex = 0x614