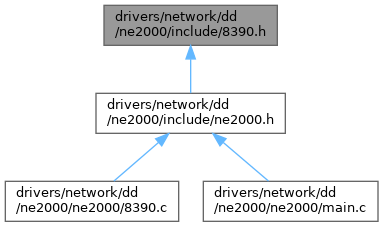

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | _PACKET_HEADER |

| struct | _ETH_HEADER |

| struct | _DISCARD_HEADER |

Macros | |

| #define | PG0_CR 0x00 /* Command Register (R/W) */ |

| #define | PG0_CLDA0 0x01 /* Current Local DMA Address 0 (R) */ |

| #define | PG0_PSTART 0x01 /* Page Start Register (W) */ |

| #define | PG0_CLDA1 0x02 /* Current Local DMA Address 1 (R) */ |

| #define | PG0_PSTOP 0x02 /* Page Stop Register (W) */ |

| #define | PG0_BNRY 0x03 /* Boundary Pointer (R/W) */ |

| #define | PG0_TSR 0x04 /* Transmit Status Register (R) */ |

| #define | PG0_TPSR 0x04 /* Transmit Page Start Register (W) */ |

| #define | PG0_NCR 0x05 /* Number of Collisions Register (R) */ |

| #define | PG0_TBCR0 0x05 /* Transmit Byte Count Register 0 (W) */ |

| #define | PG0_FIFO 0x06 /* FIFO (R) */ |

| #define | PG0_TBCR1 0x06 /* Transmit Byte Count Register 1 (W) */ |

| #define | PG0_ISR 0x07 /* Interrupt Status Register (R/W) */ |

| #define | PG0_CRDA0 0x08 /* Current Remote DMA Address 0 (R) */ |

| #define | PG0_RSAR0 0x08 /* Remote Start Address Register 0 (W) */ |

| #define | PG0_CRDA1 0x09 /* Current Remote DMA Address 1 (R) */ |

| #define | PG0_RSAR1 0x09 /* Remote Start Address Register 1 (W) */ |

| #define | PG0_RBCR0 0x0A /* Remote Byte Count Register 0 (W) */ |

| #define | PG0_RBCR1 0x0B /* Remote Byte Count Register 1 (W) */ |

| #define | PG0_RSR 0x0C /* Receive Status Register (R) */ |

| #define | PG0_RCR 0x0C /* Receive Configuration Register (W) */ |

| #define | PG0_CNTR0 0x0D /* Tally Counter 0 (Frame Alignment Errors) (R) */ |

| #define | PG0_TCR 0x0D /* Transmit Configuration Register (W) */ |

| #define | PG0_CNTR1 0x0E /* Tally Counter 1 (CRC Errors) (R) */ |

| #define | PG0_DCR 0x0E /* Data Configuration Register (W) */ |

| #define | PG0_CNTR2 0x0F /* Tally Counter 2 (Missed Packet Errors) (R) */ |

| #define | PG0_IMR 0x0F /* Interrupt Mask Register (W) */ |

| #define | PG1_CR 0x00 /* Command Register (R/W) */ |

| #define | PG1_PAR 0x01 /* Physical Address Registers (6 registers) (R/W) */ |

| #define | PG1_CURR 0x07 /* Current Page Register (R/W) */ |

| #define | PG1_MAR 0x08 /* Multicast Address Registers (8 registers) (R/W) */ |

| #define | PG2_CR 0x00 /* Command Register (R/W) */ |

| #define | PG2_PSTART 0x01 /* Page Start Register (R) */ |

| #define | PG2_CLDA0 0x01 /* Current Local DMA Address 0 (W) */ |

| #define | PG2_PSTOP 0x02 /* Page Stop Register (R) */ |

| #define | PG2_CLDA1 0x02 /* Current Local DMA Address 1 (W) */ |

| #define | PG2_RNPP 0x03 /* Remote Next Packet Pointer (R/W) */ |

| #define | PG2_TPSR 0x04 /* Transmit Page Start Address (R) */ |

| #define | PG2_LNPP 0x05 /* Local Next Packet Pointer (R/W) */ |

| #define | PG2_AC1 0x06 /* Address Counter (Upper) (R/W) */ |

| #define | PG2_AC0 0x07 /* Address Counter (Lower) (R/W) */ |

| #define | PG2_RCR 0x0C /* Receive Configuration Register (R) */ |

| #define | PG2_TCR 0x0D /* Transmit Configuration Register (R) */ |

| #define | PG2_DCR 0x0E /* Data Configuration Register (R) */ |

| #define | PG2_IMR 0x0F /* Interrupt Mask Register (R) */ |

| #define | CR_STP 0x01 /* Stop chip */ |

| #define | CR_STA 0x02 /* Start chip */ |

| #define | CR_TXP 0x04 /* Transmit a frame */ |

| #define | CR_RD0 0x08 /* Remote read */ |

| #define | CR_RD1 0x10 /* Remote write */ |

| #define | CR_RD2 0x20 /* Abort/complete remote DMA */ |

| #define | CR_PAGE0 0x00 /* Select page 0 of chip registers */ |

| #define | CR_PAGE1 0x40 /* Select page 1 of chip registers */ |

| #define | CR_PAGE2 0x80 /* Select page 2 of chip registers */ |

| #define | ISR_PRX 0x01 /* Packet received, no errors */ |

| #define | ISR_PTX 0x02 /* Packet transmitted, no errors */ |

| #define | ISR_RXE 0x04 /* Receive error */ |

| #define | ISR_TXE 0x08 /* Transmit error */ |

| #define | ISR_OVW 0x10 /* Overwrite warning */ |

| #define | ISR_CNT 0x20 /* Counter overflow */ |

| #define | ISR_RDC 0x40 /* Remote DMA complete */ |

| #define | ISR_RST 0x80 /* Reset status */ |

| #define | TSR_PTX 0x01h /* Packet transmitted without error */ |

| #define | TSR_COL 0x04h /* Collided at least once */ |

| #define | TSR_ABT 0x08h /* Collided 16 times and was dropped */ |

| #define | TSR_CRS 0x10h /* Carrier sense lost */ |

| #define | TSR_FU 0x20h /* Transmit FIFO Underrun */ |

| #define | TSR_CDH 0x40h /* Collision detect heartbeat */ |

| #define | TSR_OWC 0x80h /* Out of window collision */ |

| #define | RCR_SEP 0x01 /* Save error packets */ |

| #define | RCR_AR 0x02 /* Accept runt packets */ |

| #define | RCR_AB 0x04 /* Accept broadcasts */ |

| #define | RCR_AM 0x08 /* Accept multicast */ |

| #define | RCR_PRO 0x10 /* Promiscuous physical addresses */ |

| #define | RCR_MON 0x20 /* Monitor mode */ |

| #define | RSR_PRX 0x01 /* Received packet intact */ |

| #define | RSR_CRC 0x02 /* CRC error */ |

| #define | RSR_FAE 0x04 /* Frame alignment error */ |

| #define | RSR_FO 0x08 /* FIFO overrun */ |

| #define | RSR_MPA 0x10 /* Missed packet */ |

| #define | RSR_PHY 0x20 /* Physical/multicast address */ |

| #define | RSR_DIS 0x40 /* Receiver disabled (monitor mode) */ |

| #define | RSR_DFR 0x80 /* Deferring */ |

| #define | TCR_CRC 0x01 /* Inhibit CRC, do not append CRC */ |

| #define | TCR_LOOP 0x02 /* Set loopback mode */ |

| #define | TCR_LB01 0x06 /* Encoded loopback control */ |

| #define | TCR_ATD 0x08 /* Auto transmit disable */ |

| #define | TCR_OFST 0x10 /* Collision offset enable */ |

| #define | DCR_WTS 0x01 /* Word transfer mode selection */ |

| #define | DCR_BOS 0x02 /* Byte order selection */ |

| #define | DCR_LAS 0x04 /* Long address selection */ |

| #define | DCR_LS 0x08 /* Loopback select (when 0) */ |

| #define | DCR_ARM 0x10 /* Autoinitialize remote */ |

| #define | DCR_FT00 0x00 /* Burst length selection (1 word/2 bytes) */ |

| #define | DCR_FT01 0x20 /* burst length selection (2 words/4 bytes) */ |

| #define | DCR_FT10 0x40 /* Burst length selection (4 words/8 bytes) */ |

| #define | DCR_FT11 0x60 /* Burst length selection (6 words/12 bytes) */ |

| #define | IMR_PRXE 0x01 /* Packet received interrupt enable */ |

| #define | IMR_PTXE 0x02 /* Packet transmitted interrupt enable */ |

| #define | IMR_RXEE 0x04 /* Receive error interrupt enable */ |

| #define | IMR_TXEE 0x08 /* Transmit error interrupt enable */ |

| #define | IMR_OVWE 0x10 /* Overwrite warning interrupt enable */ |

| #define | IMR_CNTE 0x20 /* Counter overflow interrupt enable */ |

| #define | IMR_RDCE 0x40 /* Remote DMA complete interrupt enable */ |

| #define | IMR_ALLE 0x7F /* All interrupts enable */ |

| #define | IEEE_802_ADDR_LENGTH 6 |

| #define | NICDisableInterrupts(Adapter) |

| #define | NICEnableInterrupts(Adapter) |

Typedefs | |

| typedef struct _PACKET_HEADER | PACKET_HEADER |

| typedef struct _PACKET_HEADER * | PPACKET_HEADER |

| typedef struct _ETH_HEADER | ETH_HEADER |

| typedef struct _ETH_HEADER * | PETH_HEADER |

| typedef struct _DISCARD_HEADER | DISCARD_HEADER |

| typedef struct _DISCARD_HEADER * | PDISCARD_HEADER |

Functions | |

| VOID NTAPI | MiniportHandleInterrupt (IN NDIS_HANDLE MiniportAdapterContext) |

Macro Definition Documentation

◆ CR_PAGE0

◆ CR_PAGE1

◆ CR_PAGE2

◆ CR_RD0

◆ CR_RD1

◆ CR_RD2

◆ CR_STA

◆ CR_STP

◆ CR_TXP

◆ DCR_ARM

◆ DCR_BOS

◆ DCR_FT00

◆ DCR_FT01

◆ DCR_FT10

◆ DCR_FT11

◆ DCR_LAS

◆ DCR_LS

◆ DCR_WTS

◆ IEEE_802_ADDR_LENGTH

◆ IMR_ALLE

◆ IMR_CNTE

◆ IMR_OVWE

◆ IMR_PRXE

◆ IMR_PTXE

◆ IMR_RDCE

◆ IMR_RXEE

◆ IMR_TXEE

◆ ISR_CNT

◆ ISR_OVW

◆ ISR_PRX

◆ ISR_PTX

◆ ISR_RDC

◆ ISR_RST

◆ ISR_RXE

◆ ISR_TXE

◆ NICDisableInterrupts

| #define NICDisableInterrupts | ( | Adapter | ) |

◆ NICEnableInterrupts

| #define NICEnableInterrupts | ( | Adapter | ) |

◆ PG0_BNRY

◆ PG0_CLDA0

◆ PG0_CLDA1

◆ PG0_CNTR0

◆ PG0_CNTR1

◆ PG0_CNTR2

◆ PG0_CR

◆ PG0_CRDA0

◆ PG0_CRDA1

◆ PG0_DCR

◆ PG0_FIFO

◆ PG0_IMR

◆ PG0_ISR

◆ PG0_NCR

◆ PG0_PSTART

◆ PG0_PSTOP

◆ PG0_RBCR0

◆ PG0_RBCR1

◆ PG0_RCR

◆ PG0_RSAR0

◆ PG0_RSAR1

◆ PG0_RSR

◆ PG0_TBCR0

◆ PG0_TBCR1

◆ PG0_TCR

| #define PG0_TCR 0x0D /* Transmit Configuration Register (W) */ |

◆ PG0_TPSR

◆ PG0_TSR

◆ PG1_CR

◆ PG1_CURR

◆ PG1_MAR

◆ PG1_PAR

◆ PG2_AC0

◆ PG2_AC1

◆ PG2_CLDA0

◆ PG2_CLDA1

◆ PG2_CR

◆ PG2_DCR

◆ PG2_IMR

◆ PG2_LNPP

◆ PG2_PSTART

◆ PG2_PSTOP

◆ PG2_RCR

◆ PG2_RNPP

◆ PG2_TCR

| #define PG2_TCR 0x0D /* Transmit Configuration Register (R) */ |

◆ PG2_TPSR

◆ RCR_AB

◆ RCR_AM

◆ RCR_AR

◆ RCR_MON

◆ RCR_PRO

◆ RCR_SEP

◆ RSR_CRC

◆ RSR_DFR

◆ RSR_DIS

◆ RSR_FAE

◆ RSR_FO

◆ RSR_MPA

◆ RSR_PHY

◆ RSR_PRX

◆ TCR_ATD

◆ TCR_CRC

◆ TCR_LB01

◆ TCR_LOOP

◆ TCR_OFST

◆ TSR_ABT

◆ TSR_CDH

◆ TSR_COL

◆ TSR_CRS

◆ TSR_FU

◆ TSR_OWC

◆ TSR_PTX

Typedef Documentation

◆ DISCARD_HEADER

| typedef struct _DISCARD_HEADER DISCARD_HEADER |

◆ ETH_HEADER

| typedef struct _ETH_HEADER ETH_HEADER |

◆ PACKET_HEADER

| typedef struct _PACKET_HEADER PACKET_HEADER |

◆ PDISCARD_HEADER

| typedef struct _DISCARD_HEADER * PDISCARD_HEADER |

◆ PETH_HEADER

| typedef struct _ETH_HEADER * PETH_HEADER |

◆ PPACKET_HEADER

| typedef struct _PACKET_HEADER * PPACKET_HEADER |

Function Documentation

◆ MiniportHandleInterrupt()

| VOID NTAPI MiniportHandleInterrupt | ( | IN NDIS_HANDLE | MiniportAdapterContext | ) |

Definition at line 46 of file interrupt.c.

48{

49 ULONG InterruptPending;

52

54

56

57

58 /* Link State Changed */

60 {

62

63 InterruptPending &= ~E1000_IMS_LSC;

65

66 NICUpdateLinkStatus(Adapter);

67

68 Status = Adapter->MediaState == NdisMediaStateConnected ? NDIS_STATUS_MEDIA_CONNECT : NDIS_STATUS_MEDIA_DISCONNECT;

69

72 }

73

74 /* Handling receive interrupts */

76 {

78 PETH_HEADER EthHeader;

79 ULONG BufferOffset;

81 ULONG RxDescHead, RxDescTail, CurrRxDesc;

82

83 /* Clear out these interrupts */

85

88

90 {

91 CurrRxDesc = (RxDescTail + 1) % NUM_RECEIVE_DESCRIPTORS;

92 BufferOffset = CurrRxDesc * Adapter->ReceiveBufferEntrySize;

93 ReceiveDescriptor = Adapter->ReceiveDescriptors + CurrRxDesc;

94

95 /* Check if the hardware have released this descriptor (DD - Descriptor Done) */

97 {

98 /* No need to check descriptors after the first unfinished one */

99 break;

100 }

101

102 /* Ignoring these flags for now */

104

106 {

107 NDIS_DbgPrint(MIN_TRACE, ("Unrecognized ReceiveDescriptor status flag: %u\n", ReceiveDescriptor->Status));

108 }

109

110 /* Make sure the receive indications are enabled */

112 {

113 goto NextReceiveDescriptor;

114 }

115

117 {

119

121 NULL,

122 (PCHAR)EthHeader,

124 (PCHAR)(EthHeader + 1),

127

128 bGotAny = TRUE;

129 }

130 else

131 {

133 }

134

135NextReceiveDescriptor:

136 /* Give the descriptor back */

137 ReceiveDescriptor->Status = 0;

138

139 RxDescTail = CurrRxDesc;

140 }

141

142 if (bGotAny)

143 {

144 /* Write back new tail value */

146

148

150 }

151 }

152

153 /* Handling transmit interrupts */

155 {

156 PNDIS_PACKET AckPackets[40] = {0};

158

159 /* Clear out these interrupts */

161

162 while ((Adapter->TxFull || Adapter->LastTxDesc != Adapter->CurrentTxDesc) && NumPackets < ARRAYSIZE(AckPackets))

163 {

165

167 {

169 {

172 TransmitDescriptor->Status = 0;

173 }

174

177 }

178 else

179 {

180 break;

181 }

182 }

183

184 if (NumPackets)

185 {

186 NDIS_DbgPrint(MAX_TRACE, ("Tx: (TDH: %u, TDT: %u)\n", Adapter->CurrentTxDesc, Adapter->LastTxDesc));

188

190 {

192 }

193 }

194 }

195

196 ASSERT(InterruptPending == 0);

197}

struct _ETH_HEADER * PETH_HEADER

VOID NTAPI NICUpdateLinkStatus(IN PE1000_ADAPTER Adapter)

Definition: hardware.c:740

struct _E1000_ADAPTER * PE1000_ADAPTER

FORCEINLINE VOID E1000ReadUlong(_In_ PE1000_ADAPTER Adapter, _In_ ULONG Address, _Out_ PULONG Value)

Definition: nic.h:209

FORCEINLINE VOID E1000WriteUlong(_In_ PE1000_ADAPTER Adapter, _In_ ULONG Address, _In_ ULONG Value)

Definition: nic.h:219

GLsizei GLenum const GLvoid GLsizei GLenum GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLint GLint GLint GLshort GLshort GLshort GLubyte GLubyte GLubyte GLuint GLuint GLuint GLushort GLushort GLushort GLbyte GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLfloat GLint GLint GLint GLint GLshort GLshort GLshort GLshort GLubyte GLubyte GLubyte GLubyte GLuint GLuint GLuint GLuint GLushort GLushort GLushort GLushort GLboolean const GLdouble const GLfloat const GLint const GLshort const GLbyte const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLdouble const GLfloat const GLfloat const GLint const GLint const GLshort const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort GLenum GLenum GLenum GLfloat GLenum GLint GLenum GLenum GLenum GLfloat GLenum GLenum GLint GLenum GLfloat GLenum GLint GLint GLushort GLenum GLenum GLfloat GLenum GLenum GLint GLfloat const GLubyte GLenum GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLint GLint GLsizei GLsizei GLint GLenum GLenum const GLvoid GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLenum const GLdouble GLenum GLenum const GLfloat GLenum GLenum const GLint GLsizei GLuint GLfloat GLuint GLbitfield GLfloat GLint GLuint GLboolean GLenum GLfloat GLenum GLbitfield GLenum GLfloat GLfloat GLint GLint const GLfloat GLenum GLfloat GLfloat GLint GLint GLfloat GLfloat GLint GLint const GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat const GLdouble const GLfloat const GLdouble const GLfloat GLint i

Definition: glfuncs.h:248

#define NdisMEthIndicateReceiveComplete(MiniportAdapterHandle)

Definition: ndis.h:5482

#define NdisMIndicateStatusComplete(MiniportAdapterHandle)

Definition: ndis.h:5580

#define NdisMEthIndicateReceive(MiniportAdapterHandle, MiniportReceiveContext, HeaderBuffer, HeaderBufferSize, LookaheadBuffer, LookaheadBufferSize, PacketSize)

Definition: ndis.h:5458

#define NdisMSendComplete(MiniportAdapterHandle, Packet, Status)

Definition: ndis.h:5689

#define NdisMIndicateStatus(MiniportAdapterHandle, GeneralStatus, StatusBuffer, StatusBufferSize)

Definition: ndis.h:5570

long __cdecl _InterlockedExchange(_Interlocked_operand_ long volatile *_Target, long _Value)

Definition: lan.h:33

Definition: nic.h:28

PE1000_TRANSMIT_DESCRIPTOR TransmitDescriptors

Definition: nic.h:74

PNDIS_PACKET TransmitPackets[NUM_TRANSMIT_DESCRIPTORS]

Definition: nic.h:77

Definition: e1000hw.h:65

Definition: e1000hw.h:87

Definition: util.h:12

Definition: ndis.h:734