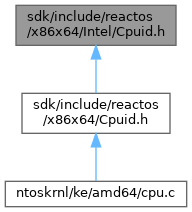

Go to the source code of this file.

Detailed Description

Intel CPUID leaf definitions.

Provides defines for CPUID leaf indexes. Data structures are provided for registers returned by a CPUID leaf that contain one or more bit fields. If a register returned is a single 32-bit value, then a data structure is not provided for that register.

Copyright (c) 2015 - 2023, Intel Corporation. All rights reserved.

SPDX-License-Identifier: BSD-2-Clause-Patent

- Specification Reference:

- Intel(R) 64 and IA-32 Architectures Software Developer's Manual, Volume 2A, November 2018, CPUID instruction. Architecture Specification: Intel(R) Trust Domain Extensions Module, Chap 10.2 344425-003US, August 2021

Definition in file Cpuid.h.

Macro Definition Documentation

◆ CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING

| #define CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING 0x0A |

CPUID Architectural Performance Monitoring

- Parameters

-

EAX CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING (0x0A)

- Return values

-

EAX Architectural Performance Monitoring information described by the type CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING_EAX. EBX Architectural Performance Monitoring information described by the type CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING_EBX. ECX Reserved. EDX Architectural Performance Monitoring information described by the type CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING_EDX.

Example usage

◆ CPUID_BRAND_STRING1

| #define CPUID_BRAND_STRING1 0x80000002 |

CPUID Processor Brand String

- Parameters

-

EAX CPUID_BRAND_STRING1 (0x80000002)

- Return values

-

EAX Processor Brand String in type CPUID_BRAND_STRING_DATA. EBX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA. ECX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA. EDX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA.

Example usage

◆ CPUID_BRAND_STRING2

| #define CPUID_BRAND_STRING2 0x80000003 |

CPUID Processor Brand String

- Parameters

-

EAX CPUID_BRAND_STRING2 (0x80000003)

- Return values

-

EAX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA. EBX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA. ECX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA. EDX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA.

Example usage

◆ CPUID_BRAND_STRING3

| #define CPUID_BRAND_STRING3 0x80000004 |

CPUID Processor Brand String

- Parameters

-

EAX CPUID_BRAND_STRING3 (0x80000004)

- Return values

-

EAX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA. EBX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA. ECX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA. EDX Processor Brand String Continued in type CPUID_BRAND_STRING_DATA.

Example usage

◆ CPUID_CACHE_INFO

| #define CPUID_CACHE_INFO 0x02 |

CPUID Cache and TLB Information

- Parameters

-

EAX CPUID_CACHE_INFO (0x02)

- Return values

-

EAX Cache and TLB Information described by the type CPUID_CACHE_INFO_CACHE_TLB. CPUID_CACHE_INFO_CACHE_TLB.CacheDescriptor[0] always returns 0x01 and must be ignored. Only valid if CPUID_CACHE_INFO_CACHE_TLB.Bits.NotValid is clear. EBX Cache and TLB Information described by the type CPUID_CACHE_INFO_CACHE_TLB. Only valid if CPUID_CACHE_INFO_CACHE_TLB.Bits.NotValid is clear. ECX Cache and TLB Information described by the type CPUID_CACHE_INFO_CACHE_TLB. Only valid if CPUID_CACHE_INFO_CACHE_TLB.Bits.NotValid is clear. EDX Cache and TLB Information described by the type CPUID_CACHE_INFO_CACHE_TLB. Only valid if CPUID_CACHE_INFO_CACHE_TLB.Bits.NotValid is clear.

Example usage

Cache Descriptor values

| Value | Type | Description |

|---|---|---|

| 0x00 | General | Null descriptor, this byte contains no information |

| 0x01 | TLB | Instruction TLB: 4 KByte pages, 4-way set associative, 32 entries |

| 0x02 | TLB | Instruction TLB: 4 MByte pages, fully associative, 2 entries |

| 0x03 | TLB | Data TLB: 4 KByte pages, 4-way set associative, 64 entries |

| 0x04 | TLB | Data TLB: 4 MByte pages, 4-way set associative, 8 entries |

| 0x05 | TLB | Data TLB1: 4 MByte pages, 4-way set associative, 32 entries |

| 0x06 | Cache | 1st-level instruction cache: 8 KBytes, 4-way set associative, 32 byte line size |

| 0x08 | Cache | 1st-level instruction cache: 16 KBytes, 4-way set associative, 32 byte line size |

| 0x09 | Cache | 1st-level instruction cache: 32KBytes, 4-way set associative, 64 byte line size |

| 0x0A | Cache | 1st-level data cache: 8 KBytes, 2-way set associative, 32 byte line size |

| 0x0B | TLB | Instruction TLB: 4 MByte pages, 4-way set associative, 4 entries |

| 0x0C | Cache | 1st-level data cache: 16 KBytes, 4-way set associative, 32 byte line size |

| 0x0D | Cache | 1st-level data cache: 16 KBytes, 4-way set associative, 64 byte line size |

| 0x0E | Cache | 1st-level data cache: 24 KBytes, 6-way set associative, 64 byte line size |

| 0x1D | Cache | 2nd-level cache: 128 KBytes, 2-way set associative, 64 byte line size |

| 0x21 | Cache | 2nd-level cache: 256 KBytes, 8-way set associative, 64 byte line size |

| 0x22 | Cache | 3rd-level cache: 512 KBytes, 4-way set associative, 64 byte line size, 2 lines per sector |

| 0x23 | Cache | 3rd-level cache: 1 MBytes, 8-way set associative, 64 byte line size, 2 lines per sector |

| 0x24 | Cache | 2nd-level cache: 1 MBytes, 16-way set associative, 64 byte line size |

| 0x25 | Cache | 3rd-level cache: 2 MBytes, 8-way set associative, 64 byte line size, 2 lines per sector |

| 0x29 | Cache | 3rd-level cache: 4 MBytes, 8-way set associative, 64 byte line size, 2 lines per sector |

| 0x2C | Cache | 1st-level data cache: 32 KBytes, 8-way set associative, 64 byte line size |

| 0x30 | Cache | 1st-level instruction cache: 32 KBytes, 8-way set associative, 64 byte line size |

| 0x40 | Cache | No 2nd-level cache or, if processor contains a valid 2nd-level cache, no 3rd-level cache |

| 0x41 | Cache | 2nd-level cache: 128 KBytes, 4-way set associative, 32 byte line size |

| 0x42 | Cache | 2nd-level cache: 256 KBytes, 4-way set associative, 32 byte line size |

| 0x43 | Cache | 2nd-level cache: 512 KBytes, 4-way set associative, 32 byte line size |

| 0x44 | Cache | 2nd-level cache: 1 MByte, 4-way set associative, 32 byte line size |

| 0x45 | Cache | 2nd-level cache: 2 MByte, 4-way set associative, 32 byte line size |

| 0x46 | Cache | 3rd-level cache: 4 MByte, 4-way set associative, 64 byte line size |

| 0x47 | Cache | 3rd-level cache: 8 MByte, 8-way set associative, 64 byte line size |

| 0x48 | Cache | 2nd-level cache: 3MByte, 12-way set associative, 64 byte line size |

| 0x49 | Cache | 3rd-level cache: 4MB, 16-way set associative, 64-byte line size (Intel Xeon processor MP, Family 0FH, Model 06H) 2nd-level cache: 4 MByte, 16-way set associative, 64 byte line size |

| 0x4A | Cache | 3rd-level cache: 6MByte, 12-way set associative, 64 byte line size |

| 0x4B | Cache | 3rd-level cache: 8MByte, 16-way set associative, 64 byte line size |

| 0x4C | Cache | 3rd-level cache: 12MByte, 12-way set associative, 64 byte line size |

| 0x4D | Cache | 3rd-level cache: 16MByte, 16-way set associative, 64 byte line size |

| 0x4E | Cache | 2nd-level cache: 6MByte, 24-way set associative, 64 byte line size |

| 0x4F | TLB | Instruction TLB: 4 KByte pages, 32 entries |

| 0x50 | TLB | Instruction TLB: 4 KByte and 2-MByte or 4-MByte pages, 64 entries |

| 0x51 | TLB | Instruction TLB: 4 KByte and 2-MByte or 4-MByte pages, 128 entries |

| 0x52 | TLB | Instruction TLB: 4 KByte and 2-MByte or 4-MByte pages, 256 entries |

| 0x55 | TLB | Instruction TLB: 2-MByte or 4-MByte pages, fully associative, 7 entries |

| 0x56 | TLB | Data TLB0: 4 MByte pages, 4-way set associative, 16 entries |

| 0x57 | TLB | Data TLB0: 4 KByte pages, 4-way associative, 16 entries |

| 0x59 | TLB | Data TLB0: 4 KByte pages, fully associative, 16 entries |

| 0x5A | TLB | Data TLB0: 2 MByte or 4 MByte pages, 4-way set associative, 32 entries |

| 0x5B | TLB | Data TLB: 4 KByte and 4 MByte pages, 64 entries |

| 0x5C | TLB | Data TLB: 4 KByte and 4 MByte pages,128 entries |

| 0x5D | TLB | Data TLB: 4 KByte and 4 MByte pages,256 entries |

| 0x60 | Cache | 1st-level data cache: 16 KByte, 8-way set associative, 64 byte line size |

| 0x61 | TLB | Instruction TLB: 4 KByte pages, fully associative, 48 entries |

| 0x63 | TLB | Data TLB: 2 MByte or 4 MByte pages, 4-way set associative, 32 entries and a separate array with 1 GByte pages, 4-way set associative, 4 entries |

| 0x64 | TLB | Data TLB: 4 KByte pages, 4-way set associative, 512 entries |

| 0x66 | Cache | 1st-level data cache: 8 KByte, 4-way set associative, 64 byte line size |

| 0x67 | Cache | 1st-level data cache: 16 KByte, 4-way set associative, 64 byte line size |

| 0x68 | Cache | 1st-level data cache: 32 KByte, 4-way set associative, 64 byte line size |

| 0x6A | Cache | uTLB: 4 KByte pages, 8-way set associative, 64 entries |

| 0x6B | Cache | DTLB: 4 KByte pages, 8-way set associative, 256 entries |

| 0x6C | Cache | DTLB: 2M/4M pages, 8-way set associative, 128 entries |

| 0x6D | Cache | DTLB: 1 GByte pages, fully associative, 16 entries |

| 0x70 | Cache | Trace cache: 12 K-uop, 8-way set associative |

| 0x71 | Cache | Trace cache: 16 K-uop, 8-way set associative |

| 0x72 | Cache | Trace cache: 32 K-uop, 8-way set associative |

| 0x76 | TLB | Instruction TLB: 2M/4M pages, fully associative, 8 entries |

| 0x78 | Cache | 2nd-level cache: 1 MByte, 4-way set associative, 64byte line size |

| 0x79 | Cache | 2nd-level cache: 128 KByte, 8-way set associative, 64 byte line size, 2 lines per sector |

| 0x7A | Cache | 2nd-level cache: 256 KByte, 8-way set associative, 64 byte line size, 2 lines per sector |

| 0x7B | Cache | 2nd-level cache: 512 KByte, 8-way set associative, 64 byte line size, 2 lines per sector |

| 0x7C | Cache | 2nd-level cache: 1 MByte, 8-way set associative, 64 byte line size, 2 lines per sector |

| 0x7D | Cache | 2nd-level cache: 2 MByte, 8-way set associative, 64byte line size |

| 0x7F | Cache | 2nd-level cache: 512 KByte, 2-way set associative, 64-byte line size |

| 0x80 | Cache | 2nd-level cache: 512 KByte, 8-way set associative, 64-byte line size |

| 0x82 | Cache | 2nd-level cache: 256 KByte, 8-way set associative, 32 byte line size |

| 0x83 | Cache | 2nd-level cache: 512 KByte, 8-way set associative, 32 byte line size |

| 0x84 | Cache | 2nd-level cache: 1 MByte, 8-way set associative, 32 byte line size |

| 0x85 | Cache | 2nd-level cache: 2 MByte, 8-way set associative, 32 byte line size |

| 0x86 | Cache | 2nd-level cache: 512 KByte, 4-way set associative, 64 byte line size |

| 0x87 | Cache | 2nd-level cache: 1 MByte, 8-way set associative, 64 byte line size |

| 0xA0 | DTLB | DTLB: 4k pages, fully associative, 32 entries |

| 0xB0 | TLB | Instruction TLB: 4 KByte pages, 4-way set associative, 128 entries |

| 0xB1 | TLB | Instruction TLB: 2M pages, 4-way, 8 entries or 4M pages, 4-way, 4 entries |

| 0xB2 | TLB | Instruction TLB: 4KByte pages, 4-way set associative, 64 entries |

| 0xB3 | TLB | Data TLB: 4 KByte pages, 4-way set associative, 128 entries |

| 0xB4 | TLB | Data TLB1: 4 KByte pages, 4-way associative, 256 entries |

| 0xB5 | TLB | Instruction TLB: 4KByte pages, 8-way set associative, 64 entries |

| 0xB6 | TLB | Instruction TLB: 4KByte pages, 8-way set associative, 128 entries |

| 0xBA | TLB | Data TLB1: 4 KByte pages, 4-way associative, 64 entries |

| 0xC0 | TLB | Data TLB: 4 KByte and 4 MByte pages, 4-way associative, 8 entries |

| 0xC1 | STLB | Shared 2nd-Level TLB: 4 KByte/2MByte pages, 8-way associative, 1024 entries |

| 0xC2 | DTLB | DTLB: 4 KByte/2 MByte pages, 4-way associative, 16 entries |

| 0xC3 | STLB | Shared 2nd-Level TLB: 4 KByte /2 MByte pages, 6-way associative, 1536 entries. Also 1GBbyte pages, 4-way, 16 entries. |

| 0xC4 | DTLB | DTLB: 2M/4M Byte pages, 4-way associative, 32 entries |

| 0xCA | STLB | Shared 2nd-Level TLB: 4 KByte pages, 4-way associative, 512 entries |

| 0xD0 | Cache | 3rd-level cache: 512 KByte, 4-way set associative, 64 byte line size |

| 0xD1 | Cache | 3rd-level cache: 1 MByte, 4-way set associative, 64 byte line size |

| 0xD2 | Cache | 3rd-level cache: 2 MByte, 4-way set associative, 64 byte line size |

| 0xD6 | Cache | 3rd-level cache: 1 MByte, 8-way set associative, 64 byte line size |

| 0xD7 | Cache | 3rd-level cache: 2 MByte, 8-way set associative, 64 byte line size |

| 0xD8 | Cache | 3rd-level cache: 4 MByte, 8-way set associative, 64 byte line size |

| 0xDC | Cache | 3rd-level cache: 1.5 MByte, 12-way set associative, 64 byte line size |

| 0xDD | Cache | 3rd-level cache: 3 MByte, 12-way set associative, 64 byte line size |

| 0xDE | Cache | 3rd-level cache: 6 MByte, 12-way set associative, 64 byte line size |

| 0xE2 | Cache | 3rd-level cache: 2 MByte, 16-way set associative, 64 byte line size |

| 0xE3 | Cache | 3rd-level cache: 4 MByte, 16-way set associative, 64 byte line size |

| 0xE4 | Cache | 3rd-level cache: 8 MByte, 16-way set associative, 64 byte line size |

| 0xEA | Cache | 3rd-level cache: 12MByte, 24-way set associative, 64 byte line size |

| 0xEB | Cache | 3rd-level cache: 18MByte, 24-way set associative, 64 byte line size |

| 0xEC | Cache | 3rd-level cache: 24MByte, 24-way set associative, 64 byte line size |

| 0xF0 | Prefetch | 64-Byte prefetching |

| 0xF1 | Prefetch | 128-Byte prefetching |

| 0xFE | General | CPUID leaf 2 does not report TLB descriptor information; use CPUID leaf 18H to query TLB and other address translation parameters. |

| 0xFF | General | CPUID leaf 2 does not report cache descriptor information, use CPUID leaf 4 to query cache parameters |

◆ CPUID_CACHE_PARAMS

| #define CPUID_CACHE_PARAMS 0x04 |

CPUID Cache Parameters

- Parameters

-

EAX CPUID_CACHE_PARAMS (0x04) ECX Cache Level. Valid values start at 0. Software can enumerate the deterministic cache parameters for each level of the cache hierarchy starting with an index value of 0, until the parameters report the value associated with the CacheType field in CPUID_CACHE_PARAMS_EAX is 0.

- Return values

-

EAX Returns cache type information described by the type CPUID_CACHE_PARAMS_EAX. EBX Returns cache line and associativity information described by the type CPUID_CACHE_PARAMS_EBX. ECX Returns the number of sets in the cache. EDX Returns cache WINVD/INVD behavior described by the type CPUID_CACHE_PARAMS_EDX.

Example usage

◆ CPUID_CACHE_PARAMS_CACHE_TYPE_DATA

◆ CPUID_CACHE_PARAMS_CACHE_TYPE_INSTRUCTION

◆ CPUID_CACHE_PARAMS_CACHE_TYPE_NULL

| #define CPUID_CACHE_PARAMS_CACHE_TYPE_NULL 0x00 |

Define value for bit field CPUID_CACHE_PARAMS_EAX.CacheType

◆ CPUID_CACHE_PARAMS_CACHE_TYPE_UNIFIED

◆ CPUID_CORE_TYPE_INTEL_ATOM

| #define CPUID_CORE_TYPE_INTEL_ATOM 0x20 |

Define value for CPUID_NATIVE_MODEL_ID_AND_CORE_TYPE_EAX.CoreType

◆ CPUID_CORE_TYPE_INTEL_CORE

◆ CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS

| #define CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS 0x18 |

CPUID Deterministic Address Translation Parameters

- Note

- Each sub-leaf enumerates a different address translation structure. If ECX contains an invalid sub-leaf index, EAX/EBX/ECX/EDX return 0. Sub-leaf index n is invalid if n exceeds the value that sub-leaf 0 returns in EAX. A sub-leaf index is also invalid if EDX[4:0] returns 0. Valid sub-leaves do not need to be contiguous or in any particular order. A valid sub-leaf may be in a higher input ECX value than an invalid sub-leaf or than a valid sub-leaf of a higher or lower-level structure. Some unified TLBs will allow a single TLB entry to satisfy data read/write and instruction fetches. Others will require separate entries (e.g., one loaded on data read/write and another loaded on an instruction fetch). Please see the Intel 64 and IA-32 Architectures Optimization Reference Manual for details of a particular product. Add one to the return value to get the result.

- Parameters

-

EAX CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS (0x18) ECX CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_MAIN_LEAF (0x00) CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_SUB_LEAF (0x*)

◆ CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_MAIN_LEAF

| #define CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_MAIN_LEAF 0x00 |

CPUID Deterministic Address Translation Parameters

- Parameters

-

EAX CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS (0x18) ECX CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_MAIN_LEAF (0x00)

- Return values

-

EAX Reports the maximum input value of supported sub-leaf in leaf 18H. EBX Returns Deterministic Address Translation Parameters described by the type CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_EBX. ECX Number of Sets. EDX Returns Deterministic Address Translation Parameters described by the type CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_EDX.

Example usage

◆ CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_TRANSLATION_CACHE_TYPE_DATA_TLB

| #define CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_TRANSLATION_CACHE_TYPE_DATA_TLB 0x01 |

◆ CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_TRANSLATION_CACHE_TYPE_INSTRUCTION_TLB

| #define CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_TRANSLATION_CACHE_TYPE_INSTRUCTION_TLB 0x02 |

◆ CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_TRANSLATION_CACHE_TYPE_INVALID

| #define CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_TRANSLATION_CACHE_TYPE_INVALID 0x00 |

◆ CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_TRANSLATION_CACHE_TYPE_UNIFIED_TLB

| #define CPUID_DETERMINISTIC_ADDRESS_TRANSLATION_PARAMETERS_TRANSLATION_CACHE_TYPE_UNIFIED_TLB 0x03 |

◆ CPUID_DIRECT_CACHE_ACCESS_INFO

| #define CPUID_DIRECT_CACHE_ACCESS_INFO 0x09 |

CPUID Direct Cache Access Information

- Parameters

-

EAX CPUID_DIRECT_CACHE_ACCESS_INFO (0x09)

- Return values

-

EAX Value of bits [31:0] of IA32_PLATFORM_DCA_CAP MSR (address 1F8H). EBX Reserved. ECX Reserved. EDX Reserved.

Example usage

◆ CPUID_EXTENDED_CACHE_INFO

| #define CPUID_EXTENDED_CACHE_INFO 0x80000006 |

CPUID Extended Cache information

- Parameters

-

EAX CPUID_EXTENDED_CACHE_INFO (0x80000006)

- Return values

-

EAX Reserved. EBX Reserved. ECX Extended cache information described by the type CPUID_EXTENDED_CACHE_INFO_ECX. EDX Reserved.

Example usage

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_128_WAY

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_128_WAY 0x0E |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_16_WAY

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_16_WAY 0x08 |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_2_WAY

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_2_WAY 0x02 |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_32_WAY

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_32_WAY 0x0A |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_48_WAY

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_48_WAY 0x0B |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_4_WAY

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_4_WAY 0x04 |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_64_WAY

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_64_WAY 0x0C |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_8_WAY

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_8_WAY 0x06 |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_96_WAY

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_96_WAY 0x0D |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_DIRECT_MAPPED

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_DIRECT_MAPPED 0x01 |

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_DISABLED

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_DISABLED 0x00 |

Define value for bit field CPUID_EXTENDED_CACHE_INFO_ECX.L2Associativity

◆ CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_FULL

| #define CPUID_EXTENDED_CACHE_INFO_ECX_L2_ASSOCIATIVITY_FULL 0x0F |

◆ CPUID_EXTENDED_CPU_SIG

| #define CPUID_EXTENDED_CPU_SIG 0x80000001 |

CPUID Extended Processor Signature and Feature Bits

- Parameters

-

EAX CPUID_EXTENDED_CPU_SIG (0x80000001)

- Return values

-

EAX CPUID_EXTENDED_CPU_SIG. EBX Reserved. ECX Extended Processor Signature and Feature Bits information described by the type CPUID_EXTENDED_CPU_SIG_ECX. EDX Extended Processor Signature and Feature Bits information described by the type CPUID_EXTENDED_CPU_SIG_EDX.

Example usage

◆ CPUID_EXTENDED_FUNCTION

| #define CPUID_EXTENDED_FUNCTION 0x80000000 |

CPUID Extended Function

- Parameters

-

EAX CPUID_EXTENDED_FUNCTION (0x80000000)

- Return values

-

EAX Maximum Input Value for Extended Function CPUID Information. EBX Reserved. ECX Reserved. EDX Reserved.

Example usage

◆ CPUID_EXTENDED_STATE

| #define CPUID_EXTENDED_STATE 0x0D |

CPUID Extended State Information

- Parameters

-

EAX CPUID_EXTENDED_STATE (0x0D) ECX CPUID_EXTENDED_STATE_MAIN_LEAF (0x00). CPUID_EXTENDED_STATE_SUB_LEAF (0x01). CPUID_EXTENDED_STATE_SIZE_OFFSET (0x02). Sub leafs 2..n based on supported bits in XCR0 or IA32_XSS_MSR.

◆ CPUID_EXTENDED_STATE_MAIN_LEAF

| #define CPUID_EXTENDED_STATE_MAIN_LEAF 0x00 |

CPUID Extended State Information Main Leaf

- Parameters

-

EAX CPUID_EXTENDED_STATE (0x0D) ECX CPUID_EXTENDED_STATE_MAIN_LEAF (0x00)

- Return values

-

EAX Reports the supported bits of the lower 32 bits of XCR0. XCR0[n] can be set to 1 only if EAX[n] is 1. The format of the extended state main leaf is described by the type CPUID_EXTENDED_STATE_MAIN_LEAF_EAX. EBX Maximum size (bytes, from the beginning of the XSAVE/XRSTOR save area) required by enabled features in XCR0. May be different than ECX if some features at the end of the XSAVE save area are not enabled. ECX Maximum size (bytes, from the beginning of the XSAVE/XRSTOR save area) of the XSAVE/XRSTOR save area required by all supported features in the processor, i.e., all the valid bit fields in XCR0. EDX Reports the supported bits of the upper 32 bits of XCR0. XCR0[n+32] can be set to 1 only if EDX[n] is 1.

Example usage

◆ CPUID_EXTENDED_STATE_SIZE_OFFSET

| #define CPUID_EXTENDED_STATE_SIZE_OFFSET 0x02 |

CPUID Extended State Information Size and Offset Sub Leaf

- Note

- Leaf 0DH output depends on the initial value in ECX. Each sub-leaf index (starting at position 2) is supported if it corresponds to a supported bit in either the XCR0 register or the IA32_XSS MSR. If ECX contains an invalid sub-leaf index, EAX/EBX/ECX/EDX return 0. Sub-leaf n (0 <= n <= 31) is invalid if sub-leaf 0 returns 0 in EAX[n] and sub-leaf 1 returns 0 in ECX[n]. Sub-leaf n (32 <= n <= 63) is invalid if sub-leaf 0 returns 0 in EDX[n-32] and sub-leaf 1 returns 0 in EDX[n-32].

- Parameters

-

EAX CPUID_EXTENDED_STATE (0x0D) ECX CPUID_EXTENDED_STATE_SIZE_OFFSET (0x02). Sub leafs 2..n based on supported bits in XCR0 or IA32_XSS_MSR.

- Return values

-

EAX The size in bytes (from the offset specified in EBX) of the save area for an extended state feature associated with a valid sub-leaf index, n. EBX The offset in bytes of this extended state component's save area from the beginning of the XSAVE/XRSTOR area. This field reports 0 if the sub-leaf index, n, does not map to a valid bit in the XCR0 register. ECX The format of the extended state components's save area as described by the type CPUID_EXTENDED_STATE_SIZE_OFFSET_ECX. This field reports 0 if the sub-leaf index, n, is invalid. EDX This field reports 0 if the sub-leaf index, n, is invalid; otherwise it is reserved.

Example usage

◆ CPUID_EXTENDED_STATE_SUB_LEAF

| #define CPUID_EXTENDED_STATE_SUB_LEAF 0x01 |

CPUID Extended State Information Sub Leaf

- Parameters

-

EAX CPUID_EXTENDED_STATE (0x0D) ECX CPUID_EXTENDED_STATE_SUB_LEAF (0x01)

- Return values

-

EAX The format of the extended state sub-leaf is described by the type CPUID_EXTENDED_STATE_SUB_LEAF_EAX. EBX The size in bytes of the XSAVE area containing all states enabled by XCRO | IA32_XSS. ECX The format of the extended state sub-leaf is described by the type CPUID_EXTENDED_STATE_SUB_LEAF_ECX. EDX Reports the supported bits of the upper 32 bits of the IA32_XSS MSR. IA32_XSS[n+32] can be set to 1 only if EDX[n] is 1.

Example usage

◆ CPUID_EXTENDED_TIME_STAMP_COUNTER

| #define CPUID_EXTENDED_TIME_STAMP_COUNTER 0x80000007 |

CPUID Extended Time Stamp Counter information

- Parameters

-

EAX CPUID_EXTENDED_TIME_STAMP_COUNTER (0x80000007)

- Return values

-

EAX Reserved. EBX Reserved. ECX Reserved. EDX Extended time stamp counter (TSC) information described by the type CPUID_EXTENDED_TIME_STAMP_COUNTER_EDX.

Example usage

◆ CPUID_EXTENDED_TOPOLOGY

| #define CPUID_EXTENDED_TOPOLOGY 0x0B |

CPUID Extended Topology Information

- Note

- CPUID leaf 1FH is a preferred superset to leaf 0BH. Intel recommends first checking for the existence of Leaf 1FH before using leaf 0BH. Most of Leaf 0BH output depends on the initial value in ECX. The EDX output of leaf 0BH is always valid and does not vary with input value in ECX. Output value in ECX[7:0] always equals input value in ECX[7:0]. Sub-leaf index 0 enumerates SMT level. Each subsequent higher sub-leaf index enumerates a higher-level topological entity in hierarchical order. For sub-leaves that return an invalid level-type of 0 in ECX[15:8]; EAX and EBX will return 0. If an input value n in ECX returns the invalid level-type of 0 in ECX[15:8], other input values with ECX > n also return 0 in ECX[15:8].

- Parameters

-

EAX CPUID_EXTENDED_TOPOLOGY (0x0B) ECX Level number

- Return values

-

EAX Extended topology information described by the type CPUID_EXTENDED_TOPOLOGY_EAX. EBX Extended topology information described by the type CPUID_EXTENDED_TOPOLOGY_EBX. ECX Extended topology information described by the type CPUID_EXTENDED_TOPOLOGY_ECX. EDX x2APIC ID the current logical processor.

Example usage

◆ CPUID_EXTENDED_TOPOLOGY_LEVEL_TYPE_CORE

◆ CPUID_EXTENDED_TOPOLOGY_LEVEL_TYPE_INVALID

| #define CPUID_EXTENDED_TOPOLOGY_LEVEL_TYPE_INVALID 0x00 |

Define value for CPUID_EXTENDED_TOPOLOGY_ECX.LevelType

◆ CPUID_EXTENDED_TOPOLOGY_LEVEL_TYPE_SMT

◆ CPUID_GUESTTD_RUNTIME_ENVIRONMENT

| #define CPUID_GUESTTD_RUNTIME_ENVIRONMENT 0x21 |

CPUID Guest TD Run Time Environment Enumeration Leaf

- Note

- Guest software can be designed to run either as a TD, as a legacy virtual machine, or directly on the CPU, based on enumeration of its run-time environment. CPUID leaf 21H emulation is done by the Intel TDX module. Sub-leaf 0 returns the values shown below. Other sub-leaves return 0 in EAX/EBX/ECX/EDX. EAX: 0x00000000 EBX: 0x65746E49 "Inte" ECX: 0x20202020 " " EDX: 0x5844546C "lTDX"

- Parameters

-

EAX CPUID_GUESTTD_RUNTIME_ENVIRONMENT (0x21) ECX Level number

◆ CPUID_GUESTTD_SIGNATURE_GENUINE_INTEL_EBX

◆ CPUID_GUESTTD_SIGNATURE_GENUINE_INTEL_ECX

| #define CPUID_GUESTTD_SIGNATURE_GENUINE_INTEL_ECX SIGNATURE_32 (' ', ' ', ' ', ' ') |

◆ CPUID_GUESTTD_SIGNATURE_GENUINE_INTEL_EDX

◆ CPUID_HYBRID_INFORMATION

| #define CPUID_HYBRID_INFORMATION 0x1A |

CPUID Hybrid Information Enumeration Leaf

- Parameters

-

EAX CPUID_HYBRID_INFORMATION (0x1A) ECX CPUID_HYBRID_INFORMATION_MAIN_LEAF (0x00).

- Return values

-

EAX Enumerates the native model ID and core type described by the type CPUID_NATIVE_MODEL_ID_AND_CORE_TYPE_EAX EBX Reserved. ECX Reserved. EDX Reserved.

Example usage

◆ CPUID_HYBRID_INFORMATION_MAIN_LEAF

| #define CPUID_HYBRID_INFORMATION_MAIN_LEAF 0x00 |

◆ CPUID_INTEL_PROCESSOR_TRACE

| #define CPUID_INTEL_PROCESSOR_TRACE 0x14 |

◆ CPUID_INTEL_PROCESSOR_TRACE_MAIN_LEAF

| #define CPUID_INTEL_PROCESSOR_TRACE_MAIN_LEAF 0x00 |

CPUID Intel Processor Trace Information Main Leaf

- Parameters

-

EAX CPUID_INTEL_PROCEDSSOR_TRACE (0x14) ECX CPUID_INTEL_PROCEDSSOR_TRACE_MAIN_LEAF (0x00)

- Return values

-

EAX Reports the maximum sub-leaf supported in leaf 14H. EBX Returns Intel processor trace information described by the type CPUID_INTEL_PROCESSOR_TRACE_MAIN_LEAF_EBX. ECX Returns Intel processor trace information described by the type CPUID_INTEL_PROCESSOR_TRACE_MAIN_LEAF_ECX. EDX Reserved.

Example usage

◆ CPUID_INTEL_PROCESSOR_TRACE_SUB_LEAF

| #define CPUID_INTEL_PROCESSOR_TRACE_SUB_LEAF 0x01 |

CPUID Intel Processor Trace Information Sub-leaf

- Parameters

-

EAX CPUID_INTEL_PROCEDSSOR_TRACE (0x14) ECX CPUID_INTEL_PROCESSOR_TRACE_SUB_LEAF (0x01)

- Return values

-

EAX Returns Intel processor trace information described by the type CPUID_INTEL_PROCESSOR_TRACE_SUB_LEAF_EAX. EBX Returns Intel processor trace information described by the type CPUID_INTEL_PROCESSOR_TRACE_SUB_LEAF_EBX. ECX Reserved. EDX Reserved.

Example usage

◆ CPUID_INTEL_RDT_ALLOCATION

| #define CPUID_INTEL_RDT_ALLOCATION 0x10 |

CPUID Intel Resource Director Technology (Intel RDT) Allocation Information

- Parameters

-

EAX CPUID_INTEL_RDT_ALLOCATION (0x10). ECX CPUID_INTEL_RDT_ALLOCATION_ENUMERATION_SUB_LEAF (0x00). CPUID_INTEL_RDT_ALLOCATION_L3_CACHE_SUB_LEAF (0x01). CPUID_INTEL_RDT_ALLOCATION_L2_CACHE_SUB_LEAF (0x02).

◆ CPUID_INTEL_RDT_ALLOCATION_ENUMERATION_SUB_LEAF

| #define CPUID_INTEL_RDT_ALLOCATION_ENUMERATION_SUB_LEAF 0x00 |

Intel Resource Director Technology (Intel RDT) Allocation Enumeration Sub-leaf

- Parameters

-

EAX CPUID_INTEL_RDT_ALLOCATION (0x10) ECX CPUID_INTEL_RDT_ALLOCATION_ENUMERATION_SUB_LEAF (0x00).

- Return values

-

EAX Reserved. EBX L3 and L2 Cache Allocation Technology information described by the type CPUID_INTEL_RDT_ALLOCATION_ENUMERATION_SUB_LEAF_EBX. ECX Reserved. EDX Reserved.

Example usage

◆ CPUID_INTEL_RDT_ALLOCATION_L2_CACHE_SUB_LEAF

| #define CPUID_INTEL_RDT_ALLOCATION_L2_CACHE_SUB_LEAF 0x02 |

L2 Cache Allocation Technology Enumeration Sub-leaf

- Parameters

-

EAX CPUID_INTEL_RDT_ALLOCATION (0x10) ECX CPUID_INTEL_RDT_ALLOCATION_L2_CACHE_SUB_LEAF (0x02)

- Return values

-

EAX RESID L2 Cache Allocation Technology information described by the type CPUID_INTEL_RDT_ALLOCATION_L2_CACHE_SUB_LEAF_EAX. EBX Bit-granular map of isolation/contention of allocation units. ECX Reserved. EDX RESID L2 Cache Allocation Technology information described by the type CPUID_INTEL_RDT_ALLOCATION_L2_CACHE_SUB_LEAF_EDX.

Example usage

◆ CPUID_INTEL_RDT_ALLOCATION_L3_CACHE_SUB_LEAF

| #define CPUID_INTEL_RDT_ALLOCATION_L3_CACHE_SUB_LEAF 0x01 |

L3 Cache Allocation Technology Enumeration Sub-leaf

- Parameters

-

EAX CPUID_INTEL_RDT_ALLOCATION (0x10) ECX CPUID_INTEL_RDT_ALLOCATION_L3_CACHE_SUB_LEAF (0x01)

- Return values

-

EAX RESID L3 Cache Allocation Technology information described by the type CPUID_INTEL_RDT_ALLOCATION_L3_CACHE_SUB_LEAF_EAX. EBX Bit-granular map of isolation/contention of allocation units. ECX RESID L3 Cache Allocation Technology information described by the type CPUID_INTEL_RDT_ALLOCATION_L3_CACHE_SUB_LEAF_ECX. EDX RESID L3 Cache Allocation Technology information described by the type CPUID_INTEL_RDT_ALLOCATION_L3_CACHE_SUB_LEAF_EDX.

Example usage

◆ CPUID_INTEL_RDT_ALLOCATION_MEMORY_BANDWIDTH_SUB_LEAF

| #define CPUID_INTEL_RDT_ALLOCATION_MEMORY_BANDWIDTH_SUB_LEAF 0x03 |

Memory Bandwidth Allocation Enumeration Sub-leaf

- Parameters

-

EAX CPUID_INTEL_RDT_ALLOCATION (0x10) ECX CPUID_INTEL_RDT_ALLOCATION_MEMORY_BANDWIDTH_SUB_LEAF (0x03)

- Return values

-

EAX RESID memory bandwidth Allocation Technology information described by the type CPUID_INTEL_RDT_ALLOCATION_MEMORY_BANDWIDTH_SUB_LEAF_EAX. EBX Reserved. ECX RESID memory bandwidth Allocation Technology information described by the type CPUID_INTEL_RDT_ALLOCATION_MEMORY_BANDWIDTH_SUB_LEAF_ECX. EDX RESID memory bandwidth Allocation Technology information described by the type CPUID_INTEL_RDT_ALLOCATION_MEMORY_BANDWIDTH_SUB_LEAF_EDX.

Example usage

◆ CPUID_INTEL_RDT_MONITORING

| #define CPUID_INTEL_RDT_MONITORING 0x0F |

◆ CPUID_INTEL_RDT_MONITORING_ENUMERATION_SUB_LEAF

| #define CPUID_INTEL_RDT_MONITORING_ENUMERATION_SUB_LEAF 0x00 |

CPUID Intel Resource Director Technology (Intel RDT) Monitoring Information Enumeration Sub-leaf

- Parameters

-

EAX CPUID_INTEL_RDT_MONITORING (0x0F) ECX CPUID_INTEL_RDT_MONITORING_ENUMERATION_SUB_LEAF (0x00)

- Return values

-

EAX Reserved. EBX Maximum range (zero-based) of RMID within this physical processor of all types. ECX Reserved. EDX L3 Cache Intel RDT Monitoring Information Enumeration described by the type CPUID_INTEL_RDT_MONITORING_ENUMERATION_SUB_LEAF_EDX.

Example usage

◆ CPUID_INTEL_RDT_MONITORING_L3_CACHE_SUB_LEAF

| #define CPUID_INTEL_RDT_MONITORING_L3_CACHE_SUB_LEAF 0x01 |

CPUID L3 Cache Intel RDT Monitoring Capability Enumeration Sub-leaf

- Parameters

-

EAX CPUID_INTEL_RDT_MONITORING (0x0F) ECX CPUID_INTEL_RDT_MONITORING_L3_CACHE_SUB_LEAF (0x01)

- Return values

-

EAX Reserved. EBX Conversion factor from reported IA32_QM_CTR value to occupancy metric (bytes). ECX Maximum range (zero-based) of RMID of this resource type. EDX L3 Cache Intel RDT Monitoring Capability information described by the type CPUID_INTEL_RDT_MONITORING_L3_CACHE_SUB_LEAF_EDX.

Example usage

◆ CPUID_INTEL_SGX

| #define CPUID_INTEL_SGX 0x12 |

Intel SGX resource capability and configuration. See Section 37.7.2 "Intel(R) SGX Resource Enumeration Leaves".

If CPUID.(EAX=07H, ECX=0H):EBX.SGX = 1, the processor also supports querying CPUID with EAX=12H on Intel SGX resource capability and configuration.

- Parameters

-

EAX CPUID_INTEL_SGX (0x12) ECX CPUID_INTEL_SGX_CAPABILITIES_0_SUB_LEAF (0x00). CPUID_INTEL_SGX_CAPABILITIES_1_SUB_LEAF (0x01). CPUID_INTEL_SGX_CAPABILITIES_RESOURCES_SUB_LEAF (0x02). Sub leafs 2..n based on the sub-leaf-type encoding (returned in EAX[3:0]) until the sub-leaf type is invalid.

◆ CPUID_INTEL_SGX_CAPABILITIES_0_SUB_LEAF

| #define CPUID_INTEL_SGX_CAPABILITIES_0_SUB_LEAF 0x00 |

Sub-Leaf 0 Enumeration of Intel SGX Capabilities. Enumerates Intel SGX capability, including enclave instruction opcode support.

- Parameters

-

EAX CPUID_INTEL_SGX (0x12) ECX CPUID_INTEL_SGX_CAPABILITIES_0_SUB_LEAF (0x00)

- Return values

-

EAX The format of Sub-Leaf 0 Enumeration of Intel SGX Capabilities is described by the type CPUID_INTEL_SGX_CAPABILITIES_0_SUB_LEAF_EAX. EBX MISCSELECT: Reports the bit vector of supported extended features that can be written to the MISC region of the SSA. ECX Reserved. EDX The format of Sub-Leaf 0 Enumeration of Intel SGX Capabilities is described by the type CPUID_INTEL_SGX_CAPABILITIES_0_SUB_LEAF_EDX.

Example usage

◆ CPUID_INTEL_SGX_CAPABILITIES_1_SUB_LEAF

| #define CPUID_INTEL_SGX_CAPABILITIES_1_SUB_LEAF 0x01 |

Sub-Leaf 1 Enumeration of Intel SGX Capabilities. Enumerates Intel SGX capability of processor state configuration and enclave configuration in the SECS structure.

- Parameters

-

EAX CPUID_INTEL_SGX (0x12) ECX CPUID_INTEL_SGX_CAPABILITIES_1_SUB_LEAF (0x01)

- Return values

-

EAX Report the valid bits of SECS.ATTRIBUTES[31:0] that software can set with ECREATE. SECS.ATTRIBUTES[n] can be set to 1 using ECREATE only if EAX[n] is 1, where n < 32. EBX Report the valid bits of SECS.ATTRIBUTES[63:32] that software can set with ECREATE. SECS.ATTRIBUTES[n+32] can be set to 1 using ECREATE only if EBX[n] is 1, where n < 32. ECX Report the valid bits of SECS.ATTRIBUTES[95:64] that software can set with ECREATE. SECS.ATTRIBUTES[n+64] can be set to 1 using ECREATE only if ECX[n] is 1, where n < 32. EDX Report the valid bits of SECS.ATTRIBUTES[127:96] that software can set with ECREATE. SECS.ATTRIBUTES[n+96] can be set to 1 using ECREATE only if EDX[n] is 1, where n < 32.

Example usage

◆ CPUID_INTEL_SGX_CAPABILITIES_RESOURCES_SUB_LEAF

| #define CPUID_INTEL_SGX_CAPABILITIES_RESOURCES_SUB_LEAF 0x02 |

Sub-Leaf Index 2 or Higher Enumeration of Intel SGX Resources. Enumerates available EPC resources.

- Parameters

-

EAX CPUID_INTEL_SGX (0x12) ECX CPUID_INTEL_SGX_CAPABILITIES_RESOURCES_SUB_LEAF (0x02)

- Return values

-

EAX The format of Sub-Leaf Index 2 or Higher Enumeration of Intel SGX Resources is described by the type CPUID_INTEL_SGX_CAPABILITIES_RESOURCES_SUB_LEAF_EAX. EBX The format of Sub-Leaf Index 2 or Higher Enumeration of Intel SGX Resources is described by the type CPUID_INTEL_SGX_CAPABILITIES_RESOURCES_SUB_LEAF_EBX. EDX The format of Sub-Leaf Index 2 or Higher Enumeration of Intel SGX Resources is described by the type CPUID_INTEL_SGX_CAPABILITIES_RESOURCES_SUB_LEAF_ECX. EDX The format of Sub-Leaf Index 2 or Higher Enumeration of Intel SGX Resources is described by the type CPUID_INTEL_SGX_CAPABILITIES_RESOURCES_SUB_LEAF_EDX.

Example usage

◆ CPUID_MONITOR_MWAIT

| #define CPUID_MONITOR_MWAIT 0x05 |

CPUID MONITOR/MWAIT Information

- Parameters

-

EAX CPUID_MONITOR_MWAIT (0x05)

- Return values

-

EAX Smallest monitor-line size in bytes described by the type CPUID_MONITOR_MWAIT_EAX. EBX Largest monitor-line size in bytes described by the type CPUID_MONITOR_MWAIT_EBX. ECX Enumeration of Monitor-Mwait extensions support described by the type CPUID_MONITOR_MWAIT_ECX. EDX Sub C-states supported described by the type CPUID_MONITOR_MWAIT_EDX.

Example usage

◆ CPUID_PROCESSOR_FREQUENCY

| #define CPUID_PROCESSOR_FREQUENCY 0x16 |

CPUID Processor Frequency Information

- Note

- Data is returned from this interface in accordance with the processor's specification and does not reflect actual values. Suitable use of this data includes the display of processor information in like manner to the processor brand string and for determining the appropriate range to use when displaying processor information e.g. frequency history graphs. The returned information should not be used for any other purpose as the returned information does not accurately correlate to information / counters returned by other processor interfaces. While a processor may support the Processor Frequency Information leaf, fields that return a value of zero are not supported.

- Parameters

-

EAX CPUID_TIME_STAMP_COUNTER (0x16)

- Return values

-

EAX Returns processor base frequency information described by the type CPUID_PROCESSOR_FREQUENCY_EAX. EBX Returns maximum frequency information described by the type CPUID_PROCESSOR_FREQUENCY_EBX. ECX Returns bus frequency information described by the type CPUID_PROCESSOR_FREQUENCY_ECX. EDX Reserved.

Example usage

◆ CPUID_SERIAL_NUMBER

| #define CPUID_SERIAL_NUMBER 0x03 |

CPUID Processor Serial Number

Processor serial number (PSN) is not supported in the Pentium 4 processor or later. On all models, use the PSN flag (returned using CPUID) to check for PSN support before accessing the feature.

- Parameters

-

EAX CPUID_SERIAL_NUMBER (0x03)

- Return values

-

EAX Reserved. EBX Reserved. ECX Bits 31:0 of 96 bit processor serial number. (Available in Pentium III processor only; otherwise, the value in this register is reserved.) EDX Bits 63:32 of 96 bit processor serial number. (Available in Pentium III processor only; otherwise, the value in this register is reserved.)

Example usage

◆ CPUID_SIGNATURE

| #define CPUID_SIGNATURE 0x00 |

CPUID Signature Information

- Parameters

-

EAX CPUID_SIGNATURE (0x00)

- Return values

-

EAX Returns the highest value the CPUID instruction recognizes for returning basic processor information. The value is returned is processor specific. EBX First 4 characters of a vendor identification string. ECX Last 4 characters of a vendor identification string. EDX Middle 4 characters of a vendor identification string.

Example usage

◆ CPUID_SIGNATURE_GENUINE_INTEL_EBX

◆ CPUID_SIGNATURE_GENUINE_INTEL_ECX

◆ CPUID_SIGNATURE_GENUINE_INTEL_EDX

◆ CPUID_SOC_VENDOR

| #define CPUID_SOC_VENDOR 0x17 |

CPUID SoC Vendor Information

- Parameters

-

EAX CPUID_SOC_VENDOR (0x17) ECX CPUID_SOC_VENDOR_MAIN_LEAF (0x00) CPUID_SOC_VENDOR_BRAND_STRING1 (0x01) CPUID_SOC_VENDOR_BRAND_STRING1 (0x02) CPUID_SOC_VENDOR_BRAND_STRING1 (0x03)

- Note

- Leaf 17H output depends on the initial value in ECX. SOC Vendor Brand String is a UTF-8 encoded string padded with trailing bytes of 00H. The complete SOC Vendor Brand String is constructed by concatenating in ascending order of EAX:EBX:ECX:EDX and from the sub-leaf 1 fragment towards sub-leaf 3.

◆ CPUID_SOC_VENDOR_BRAND_STRING1

| #define CPUID_SOC_VENDOR_BRAND_STRING1 0x01 |

CPUID SoC Vendor Information

- Parameters

-

EAX CPUID_SOC_VENDOR (0x17) ECX CPUID_SOC_VENDOR_BRAND_STRING1 (0x01)

- Return values

-

EAX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA. EBX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA. ECX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA. EDX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA.

Example usage

◆ CPUID_SOC_VENDOR_BRAND_STRING2

| #define CPUID_SOC_VENDOR_BRAND_STRING2 0x02 |

CPUID SoC Vendor Information

- Parameters

-

EAX CPUID_SOC_VENDOR (0x17) ECX CPUID_SOC_VENDOR_BRAND_STRING2 (0x02)

- Return values

-

EAX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA. EBX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA. ECX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA. EDX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA.

Example usage

◆ CPUID_SOC_VENDOR_BRAND_STRING3

| #define CPUID_SOC_VENDOR_BRAND_STRING3 0x03 |

CPUID SoC Vendor Information

- Parameters

-

EAX CPUID_SOC_VENDOR (0x17) ECX CPUID_SOC_VENDOR_BRAND_STRING3 (0x03)

- Return values

-

EAX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA. EBX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA. ECX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA. EDX SOC Vendor Brand String. UTF-8 encoded string of type CPUID_SOC_VENDOR_BRAND_STRING_DATA.

Example usage

◆ CPUID_SOC_VENDOR_MAIN_LEAF

| #define CPUID_SOC_VENDOR_MAIN_LEAF 0x00 |

CPUID SoC Vendor Information

- Parameters

-

EAX CPUID_SOC_VENDOR (0x17) ECX CPUID_SOC_VENDOR_MAIN_LEAF (0x00)

- Return values

-

EAX MaxSOCID_Index. Reports the maximum input value of supported sub-leaf in leaf 17H. EBX Returns SoC Vendor information described by the type CPUID_SOC_VENDOR_MAIN_LEAF_EBX. ECX Project ID. A unique number an SOC vendor assigns to its SOC projects. EDX Stepping ID. A unique number within an SOC project that an SOC vendor assigns.

Example usage

◆ CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS

| #define CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS 0x07 |

CPUID Structured Extended Feature Flags Enumeration

- Parameters

-

EAX CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS (0x07) ECX CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_SUB_LEAF_INFO (0x00).

- Note

- If ECX contains an invalid sub-leaf index, EAX/EBX/ECX/EDX return 0. Sub-leaf index n is invalid if n exceeds the value that sub-leaf 0 returns in EAX.

- Return values

-

EAX The maximum input value for ECX to retrieve sub-leaf information. EBX Structured Extended Feature Flags described by the type CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EBX. ECX Structured Extended Feature Flags described by the type CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX. EDX Reserved.

Example usage

◆ CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_SUB_LEAF_INFO

| #define CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_SUB_LEAF_INFO 0x00 |

◆ CPUID_THERMAL_POWER_MANAGEMENT

| #define CPUID_THERMAL_POWER_MANAGEMENT 0x06 |

CPUID Thermal and Power Management

- Parameters

-

EAX CPUID_THERMAL_POWER_MANAGEMENT (0x06)

- Return values

-

EAX Thermal and power management features described by the type CPUID_THERMAL_POWER_MANAGEMENT_EAX. EBX Number of Interrupt Thresholds in Digital Thermal Sensor described by the type CPUID_THERMAL_POWER_MANAGEMENT_EBX. ECX Performance features described by the type CPUID_THERMAL_POWER_MANAGEMENT_ECX. EDX Reserved.

Example usage

◆ CPUID_TIME_STAMP_COUNTER

| #define CPUID_TIME_STAMP_COUNTER 0x15 |

CPUID Time Stamp Counter and Nominal Core Crystal Clock Information

- Note

- If EBX[31:0] is 0, the TSC/"core crystal clock" ratio is not enumerated. EBX[31:0]/EAX[31:0] indicates the ratio of the TSC frequency and the core crystal clock frequency. If ECX is 0, the nominal core crystal clock frequency is not enumerated. "TSC frequency" = "core crystal clock frequency" * EBX/EAX. The core crystal clock may differ from the reference clock, bus clock, or core clock frequencies.

- Parameters

-

EAX CPUID_TIME_STAMP_COUNTER (0x15)

- Return values

-

EAX An unsigned integer which is the denominator of the TSC/"core crystal clock" ratio EBX An unsigned integer which is the numerator of the TSC/"core crystal clock" ratio. ECX An unsigned integer which is the nominal frequency of the core crystal clock in Hz. EDX Reserved.

Example usage

◆ CPUID_V2_EXTENDED_TOPOLOGY

| #define CPUID_V2_EXTENDED_TOPOLOGY 0x1F |

CPUID V2 Extended Topology Enumeration Leaf

- Note

- CPUID leaf 1FH is a preferred superset to leaf 0BH. Intel recommends first checking for the existence of Leaf 1FH and using this if available. Most of Leaf 1FH output depends on the initial value in ECX. The EDX output of leaf 1FH is always valid and does not vary with input value in ECX. Output value in ECX[7:0] always equals input value in ECX[7:0]. Sub-leaf index 0 enumerates SMT level. Each subsequent higher sub-leaf index enumerates a higher-level topological entity in hierarchical order. For sub-leaves that return an invalid level-type of 0 in ECX[15:8]; EAX and EBX will return 0. If an input value n in ECX returns the invalid level-type of 0 in ECX[15:8], other input values with ECX > n also return 0 in ECX[15:8].

Software should use this field (EAX[4:0]) to enumerate processor topology of the system. Software must not use EBX[15:0] to enumerate processor topology of the system. This value in this field (EBX[15:0]) is only intended for display/diagnostic purposes. The actual number of logical processors available to BIOS/OS/Applications may be different from the value of EBX[15:0], depending on software and platform hardware configurations.

- Parameters

-

EAX CPUID_V2_EXTENDED_TOPOLOGY (0x1F) ECX Level number

◆ CPUID_V2_EXTENDED_TOPOLOGY_LEVEL_TYPE_DIE

◆ CPUID_V2_EXTENDED_TOPOLOGY_LEVEL_TYPE_MODULE

| #define CPUID_V2_EXTENDED_TOPOLOGY_LEVEL_TYPE_MODULE 0x03 |

Define value for CPUID_EXTENDED_TOPOLOGY_ECX.LevelType The value of the "level type" field is not related to level numbers in any way, higher "level type" values do not mean higher levels.

◆ CPUID_V2_EXTENDED_TOPOLOGY_LEVEL_TYPE_TILE

◆ CPUID_VERSION_INFO

| #define CPUID_VERSION_INFO 0x01 |

CPUID Version Information

- Parameters

-

EAX CPUID_VERSION_INFO (0x01)

- Return values

-

EAX Returns Model, Family, Stepping Information described by the type CPUID_VERSION_INFO_EAX. EBX Returns Brand, Cache Line Size, and Initial APIC ID described by the type CPUID_VERSION_INFO_EBX. ECX CPU Feature Information described by the type CPUID_VERSION_INFO_ECX. EDX CPU Feature Information described by the type CPUID_VERSION_INFO_EDX.

Example usage

◆ CPUID_VERSION_INFO_EAX_PROCESSOR_TYPE_DUAL_PROCESSOR

| #define CPUID_VERSION_INFO_EAX_PROCESSOR_TYPE_DUAL_PROCESSOR 0x02 |

◆ CPUID_VERSION_INFO_EAX_PROCESSOR_TYPE_INTEL_OVERDRIVE_PROCESSOR

| #define CPUID_VERSION_INFO_EAX_PROCESSOR_TYPE_INTEL_OVERDRIVE_PROCESSOR 0x01 |

◆ CPUID_VERSION_INFO_EAX_PROCESSOR_TYPE_ORIGINAL_OEM_PROCESSOR

| #define CPUID_VERSION_INFO_EAX_PROCESSOR_TYPE_ORIGINAL_OEM_PROCESSOR 0x00 |

Define value for bit field CPUID_VERSION_INFO_EAX.ProcessorType

◆ CPUID_VIR_PHY_ADDRESS_SIZE

| #define CPUID_VIR_PHY_ADDRESS_SIZE 0x80000008 |

CPUID Linear Physical Address Size

- Parameters

-

EAX CPUID_VIR_PHY_ADDRESS_SIZE (0x80000008)

- Return values

-

EAX Linear/Physical Address Size described by the type CPUID_VIR_PHY_ADDRESS_SIZE_EAX. EBX Reserved. ECX Reserved. EDX Reserved.

Example usage