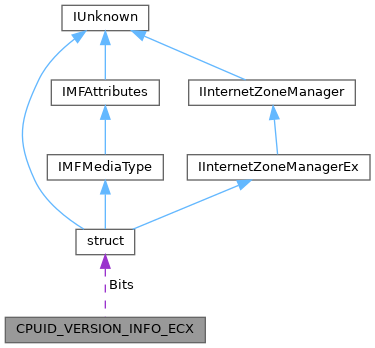

#include <Cpuid.h>

CPUID Version Information returned in ECX for CPUID leaf CPUID_VERSION_INFO.

Definition at line 165 of file Cpuid.h.

◆ AESNI

| UINT32 CPUID_VERSION_INFO_ECX::AESNI |

[Bit 25] A value of 1 indicates that the processor supports the AESNI instruction extensions.

Definition at line 298 of file Cpuid.h.

◆ AVX

| UINT32 CPUID_VERSION_INFO_ECX::AVX |

[Bit 28] A value of 1 indicates the processor supports the AVX instruction extensions.

Definition at line 315 of file Cpuid.h.

| struct { ... } CPUID_VERSION_INFO_ECX::Bits |

◆ CMPXCHG16B

| UINT32 CPUID_VERSION_INFO_ECX::CMPXCHG16B |

[Bit 13] CMPXCHG16B Available. A value of 1 indicates that the feature is available.

Definition at line 243 of file Cpuid.h.

◆ CNXT_ID

| UINT32 CPUID_VERSION_INFO_ECX::CNXT_ID |

[Bit 10] L1 Context ID. A value of 1 indicates the L1 data cache mode can be set to either adaptive mode or shared mode. A value of 0 indicates this feature is not supported. See definition of the IA32_MISC_ENABLE MSR Bit 24 (L1 Data Cache Context Mode) for details

Definition at line 228 of file Cpuid.h.

◆ DCA

| UINT32 CPUID_VERSION_INFO_ECX::DCA |

[Bit 18] A value of 1 indicates the processor supports the ability to prefetch data from a memory mapped device. Direct Cache Access.

Definition at line 265 of file Cpuid.h.

◆ DS_CPL

| UINT32 CPUID_VERSION_INFO_ECX::DS_CPL |

[Bit 4] CPL Qualified Debug Store. A value of 1 indicates the processor supports the extensions to the Debug Store feature to allow for branch message storage qualified by CPL

Definition at line 195 of file Cpuid.h.

◆ DTES64

| UINT32 CPUID_VERSION_INFO_ECX::DTES64 |

[Bit 2] 64-bit DS Area. A value of 1 indicates the processor supports DS area using 64-bit layout.

Definition at line 184 of file Cpuid.h.

◆ EIST

| UINT32 CPUID_VERSION_INFO_ECX::EIST |

[Bit 7] Enhanced Intel SpeedStep(R) technology. A value of 1 indicates that the processor supports this technology

Definition at line 210 of file Cpuid.h.

◆ F16C

| UINT32 CPUID_VERSION_INFO_ECX::F16C |

[Bit 29] A value of 1 indicates that processor supports 16-bit floating-point conversion instructions.

Definition at line 320 of file Cpuid.h.

◆ FMA

| UINT32 CPUID_VERSION_INFO_ECX::FMA |

[Bit 12] A value of 1 indicates the processor supports FMA (Fused Multiple Add) extensions using YMM state.

Definition at line 238 of file Cpuid.h.

◆ MONITOR

| UINT32 CPUID_VERSION_INFO_ECX::MONITOR |

[Bit 3] MONITOR/MWAIT. A value of 1 indicates the processor supports this feature.

Definition at line 189 of file Cpuid.h.

◆ MOVBE

| UINT32 CPUID_VERSION_INFO_ECX::MOVBE |

[Bit 22] A value of 1 indicates that the processor supports MOVBE instruction.

Definition at line 283 of file Cpuid.h.

◆ OSXSAVE

| UINT32 CPUID_VERSION_INFO_ECX::OSXSAVE |

[Bit 27] A value of 1 indicates that the OS has set CR4.OSXSAVE[Bit 18] to enable XSETBV/XGETBV instructions to access XCR0 and to support processor extended state management using XSAVE/XRSTOR.

Definition at line 310 of file Cpuid.h.

◆ ParaVirtualized

| UINT32 CPUID_VERSION_INFO_ECX::ParaVirtualized |

[Bit 31] A value of 1 indicates that processor is in Para-Virtualized.

Definition at line 328 of file Cpuid.h.

◆ PCID

| UINT32 CPUID_VERSION_INFO_ECX::PCID |

[Bit 17] Process-context identifiers. A value of 1 indicates that the processor supports PCIDs and that software may set CR4.PCIDE to 1.

Definition at line 260 of file Cpuid.h.

◆ PCLMULQDQ

| UINT32 CPUID_VERSION_INFO_ECX::PCLMULQDQ |

[Bit 1] A value of 1 indicates the processor supports the PCLMULQDQ instruction. Carryless Multiplication

Definition at line 179 of file Cpuid.h.

◆ PDCM

| UINT32 CPUID_VERSION_INFO_ECX::PDCM |

[Bit 15] Perfmon and Debug Capability: A value of 1 indicates the processor supports the performance and debug feature indication MSR IA32_PERF_CAPABILITIES.

Definition at line 254 of file Cpuid.h.

◆ POPCNT

| UINT32 CPUID_VERSION_INFO_ECX::POPCNT |

[Bit 23] A value of 1 indicates that the processor supports the POPCNT instruction.

Definition at line 288 of file Cpuid.h.

◆ RDRAND

| UINT32 CPUID_VERSION_INFO_ECX::RDRAND |

[Bit 30] A value of 1 indicates that processor supports RDRAND instruction.

Definition at line 324 of file Cpuid.h.

◆ Reserved

| UINT32 CPUID_VERSION_INFO_ECX::Reserved |

◆ SDBG

| UINT32 CPUID_VERSION_INFO_ECX::SDBG |

[Bit 11] A value of 1 indicates the processor supports IA32_DEBUG_INTERFACE MSR for silicon debug

Definition at line 233 of file Cpuid.h.

◆ SMX

| UINT32 CPUID_VERSION_INFO_ECX::SMX |

[Bit 6] Safer Mode Extensions. A value of 1 indicates that the processor supports this technology

Definition at line 205 of file Cpuid.h.

◆ SSE3

| UINT32 CPUID_VERSION_INFO_ECX::SSE3 |

[Bit 0] Streaming SIMD Extensions 3 (SSE3). A value of 1 indicates the processor supports this technology

Definition at line 174 of file Cpuid.h.

◆ SSE4_1

| UINT32 CPUID_VERSION_INFO_ECX::SSE4_1 |

[Bit 19] A value of 1 indicates that the processor supports SSE4.1.

Definition at line 269 of file Cpuid.h.

◆ SSE4_2

| UINT32 CPUID_VERSION_INFO_ECX::SSE4_2 |

[Bit 20] A value of 1 indicates that the processor supports SSE4.2.

Definition at line 273 of file Cpuid.h.

◆ SSSE3

| UINT32 CPUID_VERSION_INFO_ECX::SSSE3 |

[Bit 9] A value of 1 indicates the presence of the Supplemental Streaming SIMD Extensions 3 (SSSE3). A value of 0 indicates the instruction extensions are not present in the processor.

Definition at line 221 of file Cpuid.h.

◆ TM2

| UINT32 CPUID_VERSION_INFO_ECX::TM2 |

[Bit 8] Thermal Monitor 2. A value of 1 indicates whether the processor supports this technology

Definition at line 215 of file Cpuid.h.

◆ TSC_Deadline

| UINT32 CPUID_VERSION_INFO_ECX::TSC_Deadline |

[Bit 24] A value of 1 indicates that the processor's local APIC timer supports one-shot operation using a TSC deadline value.

Definition at line 293 of file Cpuid.h.

◆ Uint32

| UINT32 CPUID_VERSION_INFO_ECX::Uint32 |

All bit fields as a 32-bit value

Definition at line 333 of file Cpuid.h.

◆ VMX

| UINT32 CPUID_VERSION_INFO_ECX::VMX |

[Bit 5] Virtual Machine Extensions. A value of 1 indicates that the processor supports this technology.

Definition at line 200 of file Cpuid.h.

◆ x2APIC

| UINT32 CPUID_VERSION_INFO_ECX::x2APIC |

[Bit 21] A value of 1 indicates that the processor supports x2APIC feature.

Definition at line 278 of file Cpuid.h.

◆ XSAVE

| UINT32 CPUID_VERSION_INFO_ECX::XSAVE |

[Bit 26] A value of 1 indicates that the processor supports the XSAVE/XRSTOR processor extended states feature, the XSETBV/XGETBV instructions, and XCR0.

Definition at line 304 of file Cpuid.h.

◆ xTPR_Update_Control

| UINT32 CPUID_VERSION_INFO_ECX::xTPR_Update_Control |

[Bit 14] xTPR Update Control. A value of 1 indicates that the processor supports changing IA32_MISC_ENABLE[Bit 23].

Definition at line 248 of file Cpuid.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/Cpuid.h