#include <Cpuid.h>

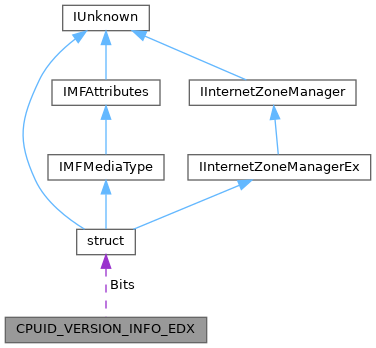

CPUID Version Information returned in EDX for CPUID leaf CPUID_VERSION_INFO.

Definition at line 340 of file Cpuid.h.

◆ ACPI

| UINT32 CPUID_VERSION_INFO_EDX::ACPI |

[Bit 22] Thermal Monitor and Software Controlled Clock Facilities. The processor implements internal MSRs that allow processor temperature to be monitored and processor performance to be modulated in predefined duty cycles under software control.

Definition at line 481 of file Cpuid.h.

◆ APIC

| UINT32 CPUID_VERSION_INFO_EDX::APIC |

[Bit 9] APIC On-Chip. The processor contains an Advanced Programmable Interrupt Controller (APIC), responding to memory mapped commands in the physical address range FFFE0000H to FFFE0FFFH (by default - some processors permit the APIC to be relocated).

Definition at line 409 of file Cpuid.h.

| struct { ... } CPUID_VERSION_INFO_EDX::Bits |

◆ CLFSH

| UINT32 CPUID_VERSION_INFO_EDX::CLFSH |

[Bit 19] CLFLUSH Instruction. CLFLUSH Instruction is supported.

Definition at line 466 of file Cpuid.h.

◆ CMOV

| UINT32 CPUID_VERSION_INFO_EDX::CMOV |

[Bit 15] Conditional Move Instructions. The conditional move instruction CMOV is supported. In addition, if x87 FPU is present as indicated by the CPUID.FPU feature bit, then the FCOMI and FCMOV instructions are supported.

Definition at line 442 of file Cpuid.h.

◆ CX8

| UINT32 CPUID_VERSION_INFO_EDX::CX8 |

[Bit 8] CMPXCHG8B Instruction. The compare-and-exchange 8 bytes(64 bits) instruction is supported (implicitly locked and atomic).

Definition at line 402 of file Cpuid.h.

◆ DE

| UINT32 CPUID_VERSION_INFO_EDX::DE |

[Bit 2] Debugging Extensions. Support for I/O breakpoints, including CR4.DE for controlling the feature, and optional trapping of accesses to DR4 and DR5.

Definition at line 362 of file Cpuid.h.

◆ DS

| UINT32 CPUID_VERSION_INFO_EDX::DS |

[Bit 21] Debug Store. The processor supports the ability to write debug information into a memory resident buffer. This feature is used by the branch trace store (BTS) and precise event-based sampling (PEBS) facilities.

Definition at line 474 of file Cpuid.h.

◆ FPU

| UINT32 CPUID_VERSION_INFO_EDX::FPU |

[Bit 0] Floating Point Unit On-Chip. The processor contains an x87 FPU.

Definition at line 348 of file Cpuid.h.

◆ FXSR

| UINT32 CPUID_VERSION_INFO_EDX::FXSR |

[Bit 24] FXSAVE and FXRSTOR Instructions. The FXSAVE and FXRSTOR instructions are supported for fast save and restore of the floating point context. Presence of this bit also indicates that CR4.OSFXSR is available for an operating system to indicate that it supports the FXSAVE and FXRSTOR instructions.

Definition at line 494 of file Cpuid.h.

◆ HTT

| UINT32 CPUID_VERSION_INFO_EDX::HTT |

[Bit 28] Max APIC IDs reserved field is Valid. A value of 0 for HTT indicates there is only a single logical processor in the package and software should assume only a single APIC ID is reserved. A value of 1 for HTT indicates the value in CPUID.1.EBX[23:16] (the Maximum number of addressable IDs for logical processors in this package) is valid for the package.

Definition at line 517 of file Cpuid.h.

◆ MCA

| UINT32 CPUID_VERSION_INFO_EDX::MCA |

[Bit 14] Machine Check Architecture. A value of 1 indicates the Machine Check Architecture of reporting machine errors is supported. The MCG_CAP MSR contains feature bits describing how many banks of error reporting MSRs are supported.

Definition at line 436 of file Cpuid.h.

◆ MCE

| UINT32 CPUID_VERSION_INFO_EDX::MCE |

[Bit 7] Machine Check Exception. Exception 18 is defined for Machine Checks, including CR4.MCE for controlling the feature. This feature does not define the model-specific implementations of machine-check error logging, reporting, and processor shutdowns. Machine Check exception handlers may have to depend on processor version to do model specific processing of the exception, or test for the presence of the Machine Check feature.

Definition at line 397 of file Cpuid.h.

◆ MMX

| UINT32 CPUID_VERSION_INFO_EDX::MMX |

[Bit 23] Intel MMX Technology. The processor supports the Intel MMX technology.

Definition at line 486 of file Cpuid.h.

◆ MSR

| UINT32 CPUID_VERSION_INFO_EDX::MSR |

[Bit 5] Model Specific Registers RDMSR and WRMSR Instructions. The RDMSR and WRMSR instructions are supported. Some of the MSRs are implementation dependent.

Definition at line 380 of file Cpuid.h.

◆ MTRR

| UINT32 CPUID_VERSION_INFO_EDX::MTRR |

[Bit 12] Memory Type Range Registers. MTRRs are supported. The MTRRcap MSR contains feature bits that describe what memory types are supported, how many variable MTRRs are supported, and whether fixed MTRRs are supported.

Definition at line 422 of file Cpuid.h.

◆ PAE

| UINT32 CPUID_VERSION_INFO_EDX::PAE |

[Bit 6] Physical Address Extension. Physical addresses greater than 32 bits are supported: extended page table entry formats, an extra level in the page translation tables is defined, 2-MByte pages are supported instead of 4 Mbyte pages if PAE bit is 1.

Definition at line 387 of file Cpuid.h.

◆ PAT

| UINT32 CPUID_VERSION_INFO_EDX::PAT |

[Bit 16] Page Attribute Table. Page Attribute Table is supported. This feature augments the Memory Type Range Registers (MTRRs), allowing an operating system to specify attributes of memory accessed through a linear address on a 4KB granularity.

Definition at line 449 of file Cpuid.h.

◆ PBE

| UINT32 CPUID_VERSION_INFO_EDX::PBE |

[Bit 31] Pending Break Enable. The processor supports the use of the FERR#/PBE# pin when the processor is in the stop-clock state (STPCLK# is asserted) to signal the processor that an interrupt is pending and that the processor should return to normal operation to handle the interrupt. Bit 10 (PBE enable) in the IA32_MISC_ENABLE MSR enables this capability.

Definition at line 531 of file Cpuid.h.

◆ PGE

| UINT32 CPUID_VERSION_INFO_EDX::PGE |

[Bit 13] Page Global Bit. The global bit is supported in paging-structure entries that map a page, indicating TLB entries that are common to different processes and need not be flushed. The CR4.PGE bit controls this feature.

Definition at line 429 of file Cpuid.h.

◆ PSE

| UINT32 CPUID_VERSION_INFO_EDX::PSE |

[Bit 3] Page Size Extension. Large pages of size 4 MByte are supported, including CR4.PSE for controlling the feature, the defined dirty bit in PDE (Page Directory Entries), optional reserved bit trapping in CR3, PDEs, and PTEs.

Definition at line 369 of file Cpuid.h.

◆ PSE_36

| UINT32 CPUID_VERSION_INFO_EDX::PSE_36 |

[Bit 17] 36-Bit Page Size Extension. 4-MByte pages addressing physical memory beyond 4 GBytes are supported with 32-bit paging. This feature indicates that upper bits of the physical address of a 4-MByte page are encoded in bits 20:13 of the page-directory entry. Such physical addresses are limited by MAXPHYADDR and may be up to 40 bits in size.

Definition at line 457 of file Cpuid.h.

◆ PSN

| UINT32 CPUID_VERSION_INFO_EDX::PSN |

[Bit 18] Processor Serial Number. The processor supports the 96-bit processor identification number feature and the feature is enabled.

Definition at line 462 of file Cpuid.h.

◆ Reserved1

| UINT32 CPUID_VERSION_INFO_EDX::Reserved1 |

◆ Reserved2

| UINT32 CPUID_VERSION_INFO_EDX::Reserved2 |

◆ Reserved3

| UINT32 CPUID_VERSION_INFO_EDX::Reserved3 |

◆ SEP

| UINT32 CPUID_VERSION_INFO_EDX::SEP |

[Bit 11] SYSENTER and SYSEXIT Instructions. The SYSENTER and SYSEXIT and associated MSRs are supported.

Definition at line 415 of file Cpuid.h.

◆ SS

| UINT32 CPUID_VERSION_INFO_EDX::SS |

[Bit 27] Self Snoop. The processor supports the management of conflicting memory types by performing a snoop of its own cache structure for transactions issued to the bus.

Definition at line 508 of file Cpuid.h.

◆ SSE

| UINT32 CPUID_VERSION_INFO_EDX::SSE |

[Bit 25] SSE. The processor supports the SSE extensions.

Definition at line 498 of file Cpuid.h.

◆ SSE2

| UINT32 CPUID_VERSION_INFO_EDX::SSE2 |

[Bit 26] SSE2. The processor supports the SSE2 extensions.

Definition at line 502 of file Cpuid.h.

◆ TM

| UINT32 CPUID_VERSION_INFO_EDX::TM |

[Bit 29] Thermal Monitor. The processor implements the thermal monitor automatic thermal control circuitry (TCC).

Definition at line 522 of file Cpuid.h.

◆ TSC

| UINT32 CPUID_VERSION_INFO_EDX::TSC |

[Bit 4] Time Stamp Counter. The RDTSC instruction is supported, including CR4.TSD for controlling privilege.

Definition at line 374 of file Cpuid.h.

◆ Uint32

| UINT32 CPUID_VERSION_INFO_EDX::Uint32 |

All bit fields as a 32-bit value

Definition at line 536 of file Cpuid.h.

◆ VME

| UINT32 CPUID_VERSION_INFO_EDX::VME |

[Bit 1] Virtual 8086 Mode Enhancements. Virtual 8086 mode enhancements, including CR4.VME for controlling the feature, CR4.PVI for protected mode virtual interrupts, software interrupt indirection, expansion of the TSS with the software indirection bitmap, and EFLAGS.VIF and EFLAGS.VIP flags.

Definition at line 356 of file Cpuid.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/Cpuid.h