#include <Cpuid.h>

Public Attributes | |

| struct { | |

| UINT32 ArchPerfMonVerID: 8 | |

| UINT32 PerformanceMonitorCounters: 8 | |

| UINT32 PerformanceMonitorCounterWidth: 8 | |

| UINT32 EbxBitVectorLength: 8 | |

| } | Bits |

| UINT32 | Uint32 |

Detailed Description

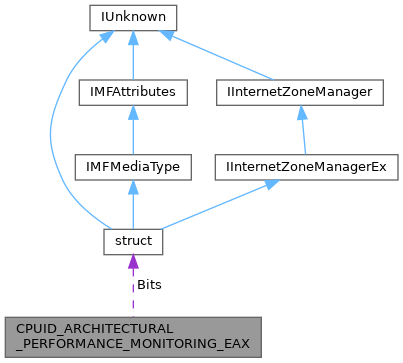

CPUID Architectural Performance Monitoring EAX for CPUID leaf CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING.

Member Data Documentation

◆ ArchPerfMonVerID

| UINT32 CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING_EAX::ArchPerfMonVerID |

◆

| struct { ... } CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING_EAX::Bits |

Individual bit fields

◆ EbxBitVectorLength

| UINT32 CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING_EAX::EbxBitVectorLength |

◆ PerformanceMonitorCounters

| UINT32 CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING_EAX::PerformanceMonitorCounters |

[Bits 15:8] Number of general-purpose performance monitoring counter per logical processor.

IA32_PERFEVTSELx MSRs start at address 186H and occupy a contiguous block of MSR address space. Each performance event select register is paired with a corresponding performance counter in the 0C1H address block.

◆ PerformanceMonitorCounterWidth

| UINT32 CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING_EAX::PerformanceMonitorCounterWidth |

[Bits 23:16] Bit width of general-purpose, performance monitoring counter.

The bit width of an IA32_PMCx MSR. This the number of valid bits for read operation. On write operations, the lower-order 32 bits of the MSR may be written with any value, and the high-order bits are sign-extended from the value of bit 31.

◆ Uint32

| UINT32 CPUID_ARCHITECTURAL_PERFORMANCE_MONITORING_EAX::Uint32 |

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/Cpuid.h