#include <Cpuid.h>

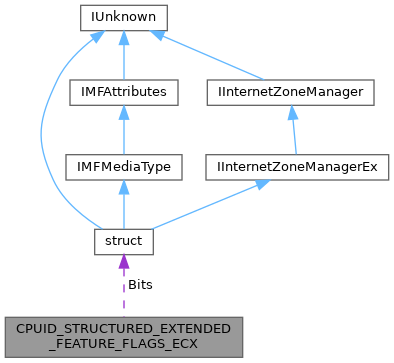

CPUID Structured Extended Feature Flags Enumeration in ECX for CPUID leaf CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS sub leaf CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_SUB_LEAF_INFO.

Definition at line 1466 of file Cpuid.h.

◆ AVX512_BITALG

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::AVX512_BITALG |

[Bit 12] AVX512_BITALG.

Definition at line 1510 of file Cpuid.h.

◆ AVX512_VBMI

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::AVX512_VBMI |

[Bit 1] AVX512_VBMI.

Definition at line 1479 of file Cpuid.h.

◆ AVX512_VBMI2

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::AVX512_VBMI2 |

[Bit 6] AVX512_VBMI2.

Definition at line 1497 of file Cpuid.h.

◆ AVX512_VNNI

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::AVX512_VNNI |

[Bit 11] AVX512_VNNI.

Definition at line 1506 of file Cpuid.h.

◆ AVX512_VPCLMULQDQ

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::AVX512_VPCLMULQDQ |

[Bit 10] AVX512_VPCLMULQDQ.

Definition at line 1502 of file Cpuid.h.

◆ AVX512_VPOPCNTDQ

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::AVX512_VPOPCNTDQ |

[Bits 14] AVX512_VPOPCNTDQ. (Intel Xeon Phi only.).

Definition at line 1519 of file Cpuid.h.

| struct { ... } CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::Bits |

◆ FiveLevelPage

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::FiveLevelPage |

[Bits 16] Supports 5-level paging if 1.

Definition at line 1524 of file Cpuid.h.

◆ MAWAU

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::MAWAU |

[Bits 21:17] The value of MAWAU used by the BNDLDX and BNDSTX instructions in 64-bit mode.

Definition at line 1529 of file Cpuid.h.

◆ OSPKE

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::OSPKE |

[Bit 4] If 1, OS has set CR4.PKE to enable protection keys (and the RDPKRU/WRPKRU instructions).

Definition at line 1492 of file Cpuid.h.

◆ PKU

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::PKU |

[Bit 3] Supports protection keys for user-mode pages if 1.

Definition at line 1487 of file Cpuid.h.

◆ PREFETCHWT1

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::PREFETCHWT1 |

[Bit 0] If 1 indicates the processor supports the PREFETCHWT1 instruction. (Intel Xeon Phi only.)

Definition at line 1475 of file Cpuid.h.

◆ RDPID

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::RDPID |

[Bit 22] RDPID and IA32_TSC_AUX are available if 1.

Definition at line 1533 of file Cpuid.h.

◆ Reserved

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::Reserved |

◆ Reserved3

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::Reserved3 |

◆ Reserved4

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::Reserved4 |

◆ Reserved7

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::Reserved7 |

◆ Reserved8

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::Reserved8 |

◆ SGX_LC

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::SGX_LC |

[Bit 30] Supports SGX Launch Configuration if 1.

Definition at line 1538 of file Cpuid.h.

◆ TME_EN

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::TME_EN |

[Bit 13] If 1, the following MSRs are supported: IA32_TME_CAPABILITY, IA32_TME_ACTIVATE, IA32_TME_EXCLUDE_MASK, and IA32_TME_EXCLUDE_BASE.

Definition at line 1515 of file Cpuid.h.

◆ Uint32

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::Uint32 |

All bit fields as a 32-bit value

Definition at line 1544 of file Cpuid.h.

◆ UMIP

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_ECX::UMIP |

[Bit 2] Supports user-mode instruction prevention if 1.

Definition at line 1483 of file Cpuid.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/Cpuid.h