#include <Cpuid.h>

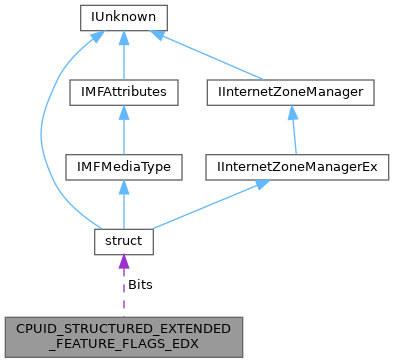

CPUID Structured Extended Feature Flags Enumeration in EDX for CPUID leaf CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS sub leaf CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_SUB_LEAF_INFO.

Definition at line 1552 of file Cpuid.h.

◆ AVX512_4FMAPS

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::AVX512_4FMAPS |

[Bit 3] AVX512_4FMAPS. (Intel Xeon Phi only.)

Definition at line 1568 of file Cpuid.h.

◆ AVX512_4VNNIW

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::AVX512_4VNNIW |

[Bit 2] AVX512_4VNNIW. (Intel Xeon Phi only.)

Definition at line 1564 of file Cpuid.h.

◆ AVX512_FP16

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::AVX512_FP16 |

[Bit 23] AVX512_FP16.

Definition at line 1589 of file Cpuid.h.

◆ AVX512_VP2INTERSECT

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::AVX512_VP2INTERSECT |

[Bit 8] AVX512_VP2INTERSECT.

Definition at line 1573 of file Cpuid.h.

| struct { ... } CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::Bits |

◆ EnumeratesSupportForCapability

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::EnumeratesSupportForCapability |

[Bit 29] Enumerates support for the IA32_ARCH_CAPABILITIES MSR.

Definition at line 1618 of file Cpuid.h.

◆ EnumeratesSupportForCoreCapabilitiesMsr

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::EnumeratesSupportForCoreCapabilitiesMsr |

[Bit 30] Enumerates support for the IA32_CORE_CAPABILITIES MSR.

Definition at line 1622 of file Cpuid.h.

◆ EnumeratesSupportForIBRSAndIBPB

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::EnumeratesSupportForIBRSAndIBPB |

[Bit 26] Enumerates support for indirect branch restricted speculation (IBRS) and the indirect branch pre-dictor barrier (IBPB). Processors that set this bit support the IA32_SPEC_CTRL MSR and the IA32_PRED_CMD MSR. They allow software to set IA32_SPEC_CTRL[0] (IBRS) and IA32_PRED_CMD[0] (IBPB).

Definition at line 1601 of file Cpuid.h.

◆ EnumeratesSupportForL1D_FLUSH

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::EnumeratesSupportForL1D_FLUSH |

[Bit 28] Enumerates support for L1D_FLUSH. Processors that set this bit support the IA32_FLUSH_CMD MSR. They allow software to set IA32_FLUSH_CMD[0] (L1D_FLUSH).

Definition at line 1614 of file Cpuid.h.

◆ EnumeratesSupportForSSBD

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::EnumeratesSupportForSSBD |

[Bit 31] Enumerates support for Speculative Store Bypass Disable (SSBD). Processors that set this bit sup-port the IA32_SPEC_CTRL MSR. They allow software to set IA32_SPEC_CTRL[2] (SSBD).

Definition at line 1628 of file Cpuid.h.

◆ EnumeratesSupportForSTIBP

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::EnumeratesSupportForSTIBP |

[Bit 27] Enumerates support for single thread indirect branch predictors (STIBP). Processors that set this bit support the IA32_SPEC_CTRL MSR. They allow software to set IA32_SPEC_CTRL[1] (STIBP).

Definition at line 1608 of file Cpuid.h.

◆ Hybrid

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::Hybrid |

[Bit 15] Hybrid. If 1, the processor is identified as a hybrid part.

Definition at line 1581 of file Cpuid.h.

◆ Reserved1

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::Reserved1 |

[Bit 1:0] Reserved.

Definition at line 1560 of file Cpuid.h.

◆ Reserved2

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::Reserved2 |

◆ Reserved3

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::Reserved3 |

[Bit 14:9] Reserved.

Definition at line 1577 of file Cpuid.h.

◆ Reserved4

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::Reserved4 |

[Bit 22:16] Reserved.

Definition at line 1585 of file Cpuid.h.

◆ Reserved5

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::Reserved5 |

[Bit 25:24] Reserved.

Definition at line 1593 of file Cpuid.h.

◆ Uint32

| UINT32 CPUID_STRUCTURED_EXTENDED_FEATURE_FLAGS_EDX::Uint32 |

All bit fields as a 32-bit value

Definition at line 1633 of file Cpuid.h.

The documentation for this union was generated from the following file:

- sdk/include/reactos/x86x64/Intel/Cpuid.h