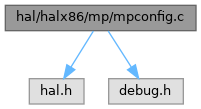

#include <hal.h>#include <debug.h>

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

Functions | |

| static UCHAR | MPChecksum (PUCHAR Base, ULONG Size) |

| static VOID | HaliMPIntSrcInfo (PMP_CONFIGURATION_INTSRC m) |

| PCHAR | HaliMPFamily (ULONG Family, ULONG Model) |

| static VOID | HaliMPProcessorInfo (PMP_CONFIGURATION_PROCESSOR m) |

| static VOID | HaliMPBusInfo (PMP_CONFIGURATION_BUS m) |

| static VOID | HaliMPIOApicInfo (PMP_CONFIGURATION_IOAPIC m) |

| static VOID | HaliMPIntLocalInfo (PMP_CONFIGURATION_INTLOCAL m) |

| static BOOLEAN | HaliReadMPConfigTable (PMP_CONFIGURATION_TABLE Table) |

| static VOID | HaliConstructDefaultIOIrqMPTable (ULONG Type) |

| static VOID | HaliConstructDefaultISAMPTable (ULONG Type) |

| static BOOLEAN | HaliScanForMPConfigTable (ULONG Base, ULONG Size) |

| static BOOLEAN | HaliGetSmpConfig (VOID) |

| BOOLEAN | HaliFindSmpConfig (VOID) |

Variables | |

| MP_FLOATING_POINTER * | Mpf = NULL |

Macro Definition Documentation

◆ NDEBUG

| #define NDEBUG |

Definition at line 12 of file mpconfig.c.

Function Documentation

◆ HaliConstructDefaultIOIrqMPTable()

Definition at line 356 of file mpconfig.c.

Referenced by HaliConstructDefaultISAMPTable(), and HaliGetSmpConfig().

◆ HaliConstructDefaultISAMPTable()

Definition at line 390 of file mpconfig.c.

Referenced by HaliGetSmpConfig().

◆ HaliFindSmpConfig()

Definition at line 605 of file mpconfig.c.

Referenced by HalpInitPhase0().

◆ HaliGetSmpConfig()

Definition at line 554 of file mpconfig.c.

Referenced by HaliFindSmpConfig().

◆ HaliMPBusInfo()

|

static |

Definition at line 176 of file mpconfig.c.

Referenced by HaliConstructDefaultISAMPTable(), HaliGetSmpConfig(), and HaliReadMPConfigTable().

◆ HaliMPFamily()

Definition at line 55 of file mpconfig.c.

Referenced by HaliMPProcessorInfo().

◆ HaliMPIntLocalInfo()

|

static |

Definition at line 230 of file mpconfig.c.

Referenced by HaliConstructDefaultISAMPTable(), and HaliReadMPConfigTable().

◆ HaliMPIntSrcInfo()

|

static |

Definition at line 37 of file mpconfig.c.

Referenced by HaliConstructDefaultIOIrqMPTable(), and HaliReadMPConfigTable().

◆ HaliMPIOApicInfo()

|

static |

Definition at line 207 of file mpconfig.c.

Referenced by HaliConstructDefaultISAMPTable(), and HaliReadMPConfigTable().

◆ HaliMPProcessorInfo()

|

static |

Definition at line 83 of file mpconfig.c.

Referenced by HaliConstructDefaultISAMPTable(), and HaliReadMPConfigTable().

◆ HaliReadMPConfigTable()

|

static |

Definition at line 258 of file mpconfig.c.

Referenced by HaliGetSmpConfig().

◆ HaliScanForMPConfigTable()

Definition at line 475 of file mpconfig.c.

Referenced by HaliFindSmpConfig().

◆ MPChecksum()

Definition at line 22 of file mpconfig.c.

Referenced by HaliReadMPConfigTable(), and HaliScanForMPConfigTable().

Variable Documentation

◆ Mpf

| MP_FLOATING_POINTER* Mpf = NULL |

Definition at line 17 of file mpconfig.c.

Referenced by HaliGetSmpConfig(), and HaliScanForMPConfigTable().