ahci_io.c File Reference

#include "pciidex.h"

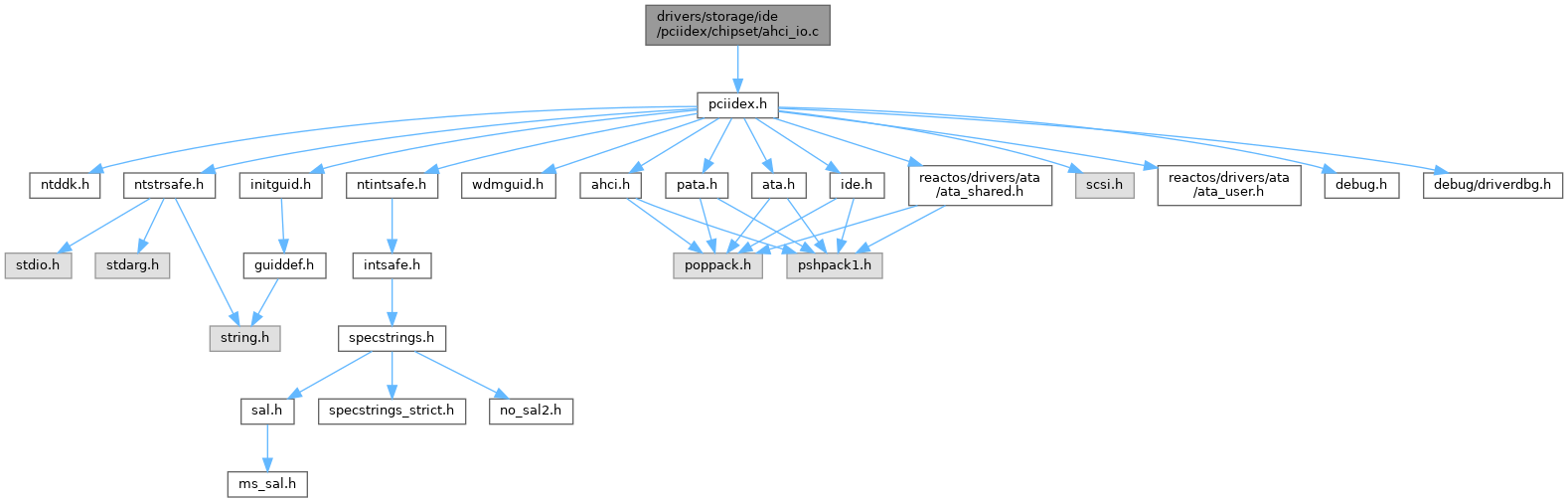

Include dependency graph for ahci_io.c:

Go to the source code of this file.

Function Documentation

◆ AtaAhciAllocateSlot()

| BOOLEAN AtaAhciAllocateSlot | ( | _In_ PVOID | ChannelContext, |

| _In_ PATA_DEVICE_REQUEST | Request, | ||

| _In_ BOOLEAN | Allocate | ||

| ) |

Definition at line 260 of file ahci_io.c.

264{

265 PCHANNEL_DATA_AHCI ChanData = ChannelContext;

266

268 {

269 /*

270 * We cannot issue commands to more than one device behind the Port Multiplier

271 * that supports only command-based switching.

272 */

274 !(ChanData->ChanInfo & CHANNEL_FLAG_FBS_ENABLED))

275 {

278 {

280 }

281

283

285 }

286 }

287 else

288 {

290 {

291 ChanData->LastPmpDeviceNumber = 0xFF;

292 }

293 }

294

296}

Definition: pciidex.h:336

◆ AtaAhciBeginHostToDeviceFis()

|

static |

Definition at line 16 of file ahci_io.c.

19{

21

22 Fis->Type = AHCI_FIS_REGISTER_HOST_TO_DEVICE;

24

26 Fis->Device = Request->TaskFile.DriveSelect;

27 else

28 Fis->Device = IDE_DRIVE_SELECT;

29

30 Fis->Control = IDE_DC_ALWAYS;

31}

Referenced by AtaAhciPrepareIo().

◆ AtaAhciBuildAtaCommandFis()

|

static |

Definition at line 68 of file ahci_io.c.

71{

73

75 Fis->Features = TaskFile->Feature;

76 Fis->LbaLow = TaskFile->LowLba;

77 Fis->LbaMid = TaskFile->MidLba;

78 Fis->LbaHigh = TaskFile->HighLba;

79 Fis->SectorCount = TaskFile->SectorCount;

80

81 /* Unique queue tag */

83 Fis->SectorCount |= Request->Slot << 3;

84

86 {

87 Fis->LbaLowEx = TaskFile->LowLbaEx;

88 Fis->LbaMidEx = TaskFile->MidLbaEx;

89 Fis->LbaHighEx = TaskFile->HighLbaEx;

90 Fis->FeaturesEx = TaskFile->FeatureEx;

91 Fis->SectorCountEx = TaskFile->SectorCountEx;

92 }

93

95 Fis->Icc = TaskFile->Icc;

96

98 Fis->Auxiliary = TaskFile->Auxiliary;

99}

Definition: hwidep.h:145

Referenced by AtaAhciPrepareIo().

◆ AtaAhciBuildPacketCommandFis()

|

static |

Definition at line 35 of file ahci_io.c.

38{

39 Fis->Command = IDE_COMMAND_ATAPI_PACKET;

40

42 {

43 /* DMA transfer */

46 {

47 /* Some SATA-to-PATA bridges require the DMADIR bit to be set */

49 }

50 else

51 {

52 Fis->Features = IDE_FEATURE_DMA;

53 }

54 }

55 else

56 {

58

59 /* PIO transfer */

62 Fis->LbaHigh = ByteCount >> 8;

63 }

64}

_Must_inspect_result_ typedef _In_ PHYSICAL_ADDRESS _In_ LARGE_INTEGER ByteCount

Definition: iotypes.h:1099

Referenced by AtaAhciPrepareIo().

◆ AtaAhciHbaIsr()

Definition at line 406 of file ahci_io.c.

409{

412

414 if (InterruptStatus == 0)

416

417 PortInterruptBitmap = InterruptStatus & Controller->ChannelBitmap;

419 {

420 PortInterruptBitmap &= ~(1 << Port);

421

423 }

424

425 /* Clear pending HBA interrupts */

427

429}

FORCEINLINE ULONG AHCI_HBA_READ(_In_ PVOID HbaIoBase, _In_ AHCI_HOST_BUS_ADAPTER_REGISTER Register)

Definition: ahci.h:529

FORCEINLINE VOID AHCI_HBA_WRITE(_In_ PVOID HbaIoBase, _In_ AHCI_HOST_BUS_ADAPTER_REGISTER Register, _In_ ULONG Value)

Definition: ahci.h:538

static VOID AtaAhciPortHandleInterrupt(_In_ PCHANNEL_DATA_AHCI ChanData)

Definition: ahci_io.c:343

unsigned char _BitScanForward(unsigned long *_Index, unsigned long _Mask)

Definition: intrin_arm.h:57

Definition: pciidex.h:170

◆ AtaAhciPortCompleteCommands()

|

static |

Definition at line 300 of file ahci_io.c.

303{

304 ULONG Slot;

305

307 {

309 UCHAR SrbStatus;

310

311 CommandsCompleted &= ~(1 << Slot);

312

313 Request = ChanData->Slots[Slot];

316

317 SrbStatus = SRB_STATUS_SUCCESS;

318

321 {

322 PAHCI_COMMAND_HEADER CommandHeader = &ChanData->CommandList->CommandHeader[Slot];

323

324 /* This indicates a residual underrun */

326 {

328 SrbStatus = SRB_STATUS_DATA_OVERRUN;

329 }

330 }

331 Request->SrbStatus = SrbStatus;

332

333 /* Save the latest copy of the task file registers */

335 {

337 }

338 }

339}

VOID AtaAhciSaveTaskFile(_In_ PCHANNEL_DATA_AHCI ChanData, _Inout_ PATA_DEVICE_REQUEST Request, _In_ BOOLEAN ProcessErrorStatus)

Definition: ahci_hw.c:1325

Definition: ahci.h:467

Definition: hwidep.h:159

Referenced by AtaAhciPortHandleInterrupt().

◆ AtaAhciPortHandleInterrupt()

|

static |

Definition at line 343 of file ahci_io.c.

345{

346 ULONG InterruptStatus, CommandsIssued, CommandsCompleted;

347 AHCI_PORT_REGISTER CommandRegister;

348

349 /* Clear all pending events */

352

354

355 /* Clear interface errors */

358

359 /* Determine commands that have completed */

360 if (ChanData->ActiveQueuedSlotsBitmap != 0)

361 CommandRegister = PxSataActive;

362 else

363 CommandRegister = PxCommandIssue;

364 CommandsIssued = AHCI_PORT_READ(ChanData->IoBase, CommandRegister);

365 CommandsCompleted = ~CommandsIssued & ChanData->ActiveSlotsBitmap;

366

367 /* Complete processed commands */

368 if (CommandsCompleted != 0)

369 {

370 ChanData->ActiveSlotsBitmap &= ~CommandsCompleted;

371 ChanData->ActiveQueuedSlotsBitmap &= ~CommandsCompleted;

372

373 AtaAhciPortCompleteCommands(ChanData, CommandsCompleted);

374 ChanData->PortNotification(AtaRequestComplete, ChanData->PortContext, CommandsCompleted);

375 }

376

377 /* Asynchronous notification received */

379 {

381

383 {

385

387

388 ChanData->PortNotification(AtaAsyncNotificationDetected, ChanData->PortContext, 0x1);

389 }

390 }

391

392 /* Handle various errors and link change events */

394 {

395 AtaAhciHandlePortStateChange(ChanData, InterruptStatus);

396 }

397

399 {

400 AtaAhciHandleFatalError(ChanData);

401 }

402}

FORCEINLINE VOID AHCI_PORT_WRITE(_In_ PVOID PortIoBase, _In_ AHCI_PORT_REGISTER Register, _In_ ULONG Value)

Definition: ahci.h:557

enum _AHCI_PORT_REGISTER AHCI_PORT_REGISTER

FORCEINLINE ULONG AHCI_PORT_READ(_In_ PVOID PortIoBase, _In_ AHCI_PORT_REGISTER Register)

Definition: ahci.h:548

VOID AtaAhciHandleFatalError(_In_ PCHANNEL_DATA_AHCI ChanData)

Definition: ahci_hw.c:1397

VOID AtaAhciHandlePortStateChange(_In_ PCHANNEL_DATA_AHCI ChanData, _In_ ULONG InterruptStatus)

Definition: ahci_hw.c:1512

static VOID AtaAhciPortCompleteCommands(_In_ PCHANNEL_DATA_AHCI ChanData, _In_ ULONG CommandsCompleted)

Definition: ahci_io.c:300

Referenced by AtaAhciHbaIsr().

◆ AtaAhciPrepareIo()

| VOID AtaAhciPrepareIo | ( | _In_ PVOID | ChannelContext, |

| _In_ PATA_DEVICE_REQUEST | Request | ||

| ) |

Definition at line 169 of file ahci_io.c.

172{

173 PCHANNEL_DATA_AHCI ChanData = ChannelContext;

174 PAHCI_COMMAND_TABLE CommandTable;

175 PAHCI_COMMAND_HEADER CommandHeader;

176 PAHCI_FIS_HOST_TO_DEVICE Fis;

178

181

183 {

185

187

189 {

191 }

192 }

193

195

196 Fis = &CommandTable->HostToDeviceFis;

197

199

201 {

204 Request->Cdb,

205 Request->Device);

206

208 }

209 else

210 {

212 }

213

216 CommandHeader->PrdByteCount = 0;

217

219}

#define AHCI_COMMAND_HEADER_PRDT_LENGTH_SHIFT

Definition: ahci.h:479

static VOID AtaAhciBuildPacketCommandFis(_In_ ATA_DEVICE_REQUEST *__restrict Request, _Out_ AHCI_FIS_HOST_TO_DEVICE *__restrict Fis)

Definition: ahci_io.c:35

static VOID AtaAhciTransferACMDRegion(_In_ VOID *__restrict Destination, _In_ VOID *__restrict Source, _In_ ATA_IO_CONTEXT_COMMON *__restrict Device)

Definition: ahci_io.c:104

static VOID AtaAhciBeginHostToDeviceFis(_In_ ATA_DEVICE_REQUEST *__restrict Request, _Out_ AHCI_FIS_HOST_TO_DEVICE *__restrict Fis)

Definition: ahci_io.c:16

static VOID AtaAhciBuildAtaCommandFis(_In_ ATA_DEVICE_REQUEST *__restrict Request, _Out_ AHCI_FIS_HOST_TO_DEVICE *__restrict Fis)

Definition: ahci_io.c:68

AHCI_COMMAND_HEADER CommandHeader[ANYSIZE_ARRAY]

Definition: ahci.h:492

Definition: ahci.h:509

Definition: ahci.h:356

PAHCI_COMMAND_TABLE CommandTable[AHCI_MAX_COMMAND_SLOTS]

Definition: pciidex.h:343

◆ AtaAhciPreparePrdTable()

| VOID AtaAhciPreparePrdTable | ( | _In_ PVOID | ChannelContext, |

| _In_ PATA_DEVICE_REQUEST | Request, | ||

| _In_ SCATTER_GATHER_LIST *__restrict | SgList | ||

| ) |

Definition at line 222 of file ahci_io.c.

226{

227 PCHANNEL_DATA_AHCI ChanData = ChannelContext;

228 PAHCI_PRD_TABLE_ENTRY PrdTableEntry;

230#if DBG

232#endif

233

236

238

240 {

245 ASSERT(i < ChanData->MaximumPhysicalPages);

246

250

251 ++PrdTableEntry;

252 }

253

254 /* Enable IRQ on last entry */

255 --PrdTableEntry;

257}

GLsizei GLenum const GLvoid GLsizei GLenum GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLint GLint GLint GLshort GLshort GLshort GLubyte GLubyte GLubyte GLuint GLuint GLuint GLushort GLushort GLushort GLbyte GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLfloat GLint GLint GLint GLint GLshort GLshort GLshort GLshort GLubyte GLubyte GLubyte GLubyte GLuint GLuint GLuint GLuint GLushort GLushort GLushort GLushort GLboolean const GLdouble const GLfloat const GLint const GLshort const GLbyte const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLdouble const GLfloat const GLfloat const GLint const GLint const GLshort const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort GLenum GLenum GLenum GLfloat GLenum GLint GLenum GLenum GLenum GLfloat GLenum GLenum GLint GLenum GLfloat GLenum GLint GLint GLushort GLenum GLenum GLfloat GLenum GLenum GLint GLfloat const GLubyte GLenum GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLint GLint GLsizei GLsizei GLint GLenum GLenum const GLvoid GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLenum const GLdouble GLenum GLenum const GLfloat GLenum GLenum const GLint GLsizei GLuint GLfloat GLuint GLbitfield GLfloat GLint GLuint GLboolean GLenum GLfloat GLenum GLbitfield GLenum GLfloat GLfloat GLint GLint const GLfloat GLenum GLfloat GLfloat GLint GLint GLfloat GLfloat GLint GLint const GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat const GLdouble const GLfloat const GLdouble const GLfloat GLint i

Definition: glfuncs.h:248

Definition: ahci.h:496

WDF_EXTERN_C_START typedef _In_ WDFDEVICE _In_ WDFCONTEXT _In_ WDF_DMA_DIRECTION _In_ PSCATTER_GATHER_LIST SgList

Definition: wdfdmatransaction.h:71

◆ AtaAhciStartIo()

| BOOLEAN AtaAhciStartIo | ( | _In_ PVOID | ChannelContext, |

| _In_ PATA_DEVICE_REQUEST | Request | ||

| ) |

Definition at line 134 of file ahci_io.c.

137{

138 PCHANNEL_DATA_AHCI ChanData = ChannelContext;

140 ULONG IssueSlot;

141

142 IssueSlot = 1 << Request->Slot;

143

144 ChanData->ActiveSlotsBitmap |= IssueSlot;

145

147 {

148 ChanData->ActiveQueuedSlotsBitmap |= IssueSlot;

150 }

151

154 {

156

158

162 }

163

166}

◆ AtaAhciTransferACMDRegion()

|

static |

Copy the CDB bytes (12 or 16 bytes)

Definition at line 104 of file ahci_io.c.

108{

109 /* Both addresses are 8-byte aligned */

110#if defined(_WIN64)

112

113 *Dest++ = *Src++;

114

116 *Dest = *Src;

117 else

119#else

121

122 *Dest++ = *Src++;

123 *Dest++ = *Src++;

124 *Dest++ = *Src++;

125

127 *Dest = *Src;

128#endif

129}

Referenced by AtaAhciPrepareIo().

◆ C_ASSERT() [1/2]

| C_ASSERT | ( | FIELD_OFFSET(AHCI_COMMAND_TABLE, AtapiCommand) % sizeof(ULONG64) | = =0 | ) |

◆ C_ASSERT() [2/2]

| C_ASSERT | ( | FIELD_OFFSET(ATA_DEVICE_REQUEST, Cdb) % sizeof(ULONG64) | = =0 | ) |