actbl2.h File Reference

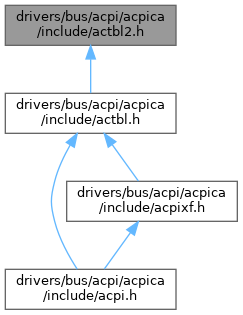

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macro Definition Documentation

◆ ACPI_AEST_CACHE_DATA

◆ ACPI_AEST_CACHE_INSTRUCTION

◆ ACPI_AEST_CACHE_RESERVED

◆ ACPI_AEST_CACHE_RESOURCE

◆ ACPI_AEST_CACHE_UNIFIED

◆ ACPI_AEST_GENERIC_RESOURCE

◆ ACPI_AEST_GIC_CPU

◆ ACPI_AEST_GIC_DISTRIBUTOR

◆ ACPI_AEST_GIC_ERROR_NODE

◆ ACPI_AEST_GIC_ITS

◆ ACPI_AEST_GIC_REDISTRIBUTOR

◆ ACPI_AEST_GIC_RESERVED

◆ ACPI_AEST_MEMORY_ERROR_NODE

◆ ACPI_AEST_NODE_ERROR_RECOVERY

◆ ACPI_AEST_NODE_FAULT_HANDLING

◆ ACPI_AEST_NODE_MEMORY_MAPPED

◆ ACPI_AEST_NODE_SYSTEM_REGISTER

◆ ACPI_AEST_NODE_TYPE_RESERVED

◆ ACPI_AEST_PROCESSOR_ERROR_NODE

◆ ACPI_AEST_RESOURCE_RESERVED

◆ ACPI_AEST_SMMU_ERROR_NODE

◆ ACPI_AEST_TLB_RESOURCE

◆ ACPI_AEST_VENDOR_ERROR_NODE

◆ ACPI_AEST_XFACE_RESERVED

◆ ACPI_AEST_XRUPT_RESERVED

◆ ACPI_AGDI_SIGNALING_MODE

◆ ACPI_APMT_FLAGS_AFFINITY

◆ ACPI_APMT_FLAGS_AFFINITY_PROC

◆ ACPI_APMT_FLAGS_AFFINITY_PROC_CONTAINER

◆ ACPI_APMT_FLAGS_ATOMIC

◆ ACPI_APMT_FLAGS_ATOMIC_NSUPP

◆ ACPI_APMT_FLAGS_ATOMIC_SUPP

◆ ACPI_APMT_FLAGS_DUAL_PAGE

◆ ACPI_APMT_FLAGS_DUAL_PAGE_NSUPP

◆ ACPI_APMT_FLAGS_DUAL_PAGE_SUPP

◆ ACPI_APMT_NODE_ID_LENGTH

◆ ACPI_APMT_OVFLW_IRQ_FLAGS_MODE

◆ ACPI_APMT_OVFLW_IRQ_FLAGS_MODE_EDGE

◆ ACPI_APMT_OVFLW_IRQ_FLAGS_MODE_LEVEL

◆ ACPI_APMT_OVFLW_IRQ_FLAGS_TYPE

◆ ACPI_APMT_OVFLW_IRQ_FLAGS_TYPE_WIRED

◆ ACPI_IORT_ATS_SUPPORTED

◆ ACPI_IORT_HT_OVERRIDE

◆ ACPI_IORT_HT_READ

◆ ACPI_IORT_HT_TRANSIENT

◆ ACPI_IORT_HT_WRITE

◆ ACPI_IORT_ID_SINGLE_MAPPING

◆ ACPI_IORT_MF_ATTRIBUTES

◆ ACPI_IORT_MF_COHERENCY

◆ ACPI_IORT_NC_PASID_BITS

◆ ACPI_IORT_NC_STALL_SUPPORTED

◆ ACPI_IORT_NODE_COHERENT

◆ ACPI_IORT_NODE_NOT_COHERENT

◆ ACPI_IORT_PASID_FWD_SUPPORTED

◆ ACPI_IORT_PASID_MAX_WIDTH

◆ ACPI_IORT_PRI_SUPPORTED

◆ ACPI_IORT_RMR_ACCESS_ATTRIBUTES

◆ ACPI_IORT_RMR_ACCESS_PRIVILEGE

◆ ACPI_IORT_RMR_ATTR_DEVICE_GRE

◆ ACPI_IORT_RMR_ATTR_DEVICE_NGNRE

◆ ACPI_IORT_RMR_ATTR_DEVICE_NGNRNE

◆ ACPI_IORT_RMR_ATTR_DEVICE_NGRE

◆ ACPI_IORT_RMR_ATTR_NORMAL_IWB_OWB

◆ ACPI_IORT_RMR_ATTR_NORMAL_NC

◆ ACPI_IORT_RMR_REMAP_PERMITTED

◆ ACPI_IORT_SMMU_CAVIUM_THUNDERX

| #define ACPI_IORT_SMMU_CAVIUM_THUNDERX 0x00000005 /* Cavium ThunderX SMMUv2 */ |

◆ ACPI_IORT_SMMU_COHERENT_WALK

◆ ACPI_IORT_SMMU_CORELINK_MMU400

| #define ACPI_IORT_SMMU_CORELINK_MMU400 0x00000002 /* ARM Corelink MMU-400 */ |

◆ ACPI_IORT_SMMU_CORELINK_MMU401

| #define ACPI_IORT_SMMU_CORELINK_MMU401 0x00000004 /* ARM Corelink MMU-401 */ |

◆ ACPI_IORT_SMMU_CORELINK_MMU500

| #define ACPI_IORT_SMMU_CORELINK_MMU500 0x00000003 /* ARM Corelink MMU-500 */ |

◆ ACPI_IORT_SMMU_DVM_SUPPORTED

◆ ACPI_IORT_SMMU_V1

◆ ACPI_IORT_SMMU_V2

◆ ACPI_IORT_SMMU_V3_CAVIUM_CN99XX

| #define ACPI_IORT_SMMU_V3_CAVIUM_CN99XX 0x00000002 /* Cavium CN99xx SMMUv3 */ |

◆ ACPI_IORT_SMMU_V3_COHACC_OVERRIDE

◆ ACPI_IORT_SMMU_V3_DEVICEID_VALID

◆ ACPI_IORT_SMMU_V3_GENERIC

| #define ACPI_IORT_SMMU_V3_GENERIC 0x00000000 /* Generic SMMUv3 */ |

◆ ACPI_IORT_SMMU_V3_HISILICON_HI161X

| #define ACPI_IORT_SMMU_V3_HISILICON_HI161X 0x00000001 /* HiSilicon Hi161x SMMUv3 */ |

◆ ACPI_IORT_SMMU_V3_HTTU_OVERRIDE

◆ ACPI_IORT_SMMU_V3_PXM_VALID

◆ ACPI_IVHD_ATS_DISABLED

◆ ACPI_IVHD_EINT_PASS

◆ ACPI_IVHD_ENTRY_LENGTH

◆ ACPI_IVHD_HPET

◆ ACPI_IVHD_INIT_PASS

◆ ACPI_IVHD_IOAPIC

◆ ACPI_IVHD_IOTLB

◆ ACPI_IVHD_ISOC

◆ ACPI_IVHD_LINT0_PASS

◆ ACPI_IVHD_LINT1_PASS

◆ ACPI_IVHD_MSI_NUMBER_MASK

◆ ACPI_IVHD_NMI_PASS

◆ ACPI_IVHD_PASS_PW

◆ ACPI_IVHD_RES_PASS_PW

◆ ACPI_IVHD_SYSTEM_MGMT

◆ ACPI_IVHD_TT_ENABLE

◆ ACPI_IVHD_UNIT_ID_MASK

◆ ACPI_IVMD_EXCLUSION_RANGE

◆ ACPI_IVMD_READ

◆ ACPI_IVMD_UNITY

◆ ACPI_IVMD_WRITE

◆ ACPI_IVRS_ATS_RESERVED

◆ ACPI_IVRS_PHYSICAL_SIZE

◆ ACPI_IVRS_UID_IS_INTEGER

◆ ACPI_IVRS_UID_IS_STRING

◆ ACPI_IVRS_UID_NOT_PRESENT

◆ ACPI_IVRS_VIRTUAL_SIZE

◆ ACPI_LPIT_NO_COUNTER

◆ ACPI_LPIT_STATE_DISABLED

◆ ACPI_MADT_CPEI_OVERRIDE

◆ ACPI_MADT_DUAL_PIC

◆ ACPI_MADT_ENABLED

◆ ACPI_MADT_MULTIPLE_APIC

◆ ACPI_MADT_ONLINE_CAPABLE

| #define ACPI_MADT_ONLINE_CAPABLE (2) /* 01: System HW supports enabling processor at runtime */ |

◆ ACPI_MADT_OVERRIDE_SPI_VALUES

◆ ACPI_MADT_PCAT_COMPAT

◆ ACPI_MADT_PERFORMANCE_IRQ_MODE

◆ ACPI_MADT_POLARITY_ACTIVE_HIGH

◆ ACPI_MADT_POLARITY_ACTIVE_LOW

◆ ACPI_MADT_POLARITY_CONFORMS

◆ ACPI_MADT_POLARITY_MASK

◆ ACPI_MADT_POLARITY_RESERVED

◆ ACPI_MADT_TRIGGER_CONFORMS

◆ ACPI_MADT_TRIGGER_EDGE

◆ ACPI_MADT_TRIGGER_LEVEL

◆ ACPI_MADT_TRIGGER_MASK

◆ ACPI_MADT_TRIGGER_RESERVED

◆ ACPI_MADT_VGIC_IRQ_MODE

◆ ACPI_MP_WAKE_COMMAND_WAKEUP

◆ ACPI_MPST_AUTOENTRY

◆ ACPI_MPST_AUTOEXIT

◆ ACPI_MPST_CHANNEL_INFO

◆ ACPI_MPST_ENABLED

◆ ACPI_MPST_HOT_PLUG_CAPABLE

◆ ACPI_MPST_POWER_MANAGED

◆ ACPI_MPST_PRESERVE

◆ ACPI_MULTIPROC_WAKEUP_MB_FIRMWARE_SIZE

◆ ACPI_MULTIPROC_WAKEUP_MB_OS_SIZE

◆ ACPI_NFIT_ADD_ONLINE_ONLY

◆ ACPI_NFIT_BUILD_DEVICE_HANDLE

Value:

((dimm) | \

((channel) << ACPI_NFIT_CHANNEL_NUMBER_OFFSET) | \

((memory) << ACPI_NFIT_MEMORY_ID_OFFSET) | \

((socket) << ACPI_NFIT_SOCKET_ID_OFFSET) | \

((node) << ACPI_NFIT_NODE_ID_OFFSET))

Definition: winhttp_private.h:285

Definition: dlist.c:348

◆ ACPI_NFIT_CAPABILITY_CACHE_FLUSH

◆ ACPI_NFIT_CAPABILITY_MEM_FLUSH

◆ ACPI_NFIT_CAPABILITY_MEM_MIRRORING

◆ ACPI_NFIT_CHANNEL_NUMBER_MASK

◆ ACPI_NFIT_CHANNEL_NUMBER_OFFSET

◆ ACPI_NFIT_CONTROL_BUFFERED

◆ ACPI_NFIT_CONTROL_MFG_INFO_VALID

◆ ACPI_NFIT_DIMM_NUMBER_MASK

◆ ACPI_NFIT_DIMM_NUMBER_OFFSET

◆ ACPI_NFIT_GET_CHANNEL_NUMBER

| #define ACPI_NFIT_GET_CHANNEL_NUMBER | ( | handle | ) | (((handle) & ACPI_NFIT_CHANNEL_NUMBER_MASK) >> ACPI_NFIT_CHANNEL_NUMBER_OFFSET) |

◆ ACPI_NFIT_GET_DIMM_NUMBER

| #define ACPI_NFIT_GET_DIMM_NUMBER | ( | handle | ) | ((handle) & ACPI_NFIT_DIMM_NUMBER_MASK) |

◆ ACPI_NFIT_GET_MEMORY_ID

| #define ACPI_NFIT_GET_MEMORY_ID | ( | handle | ) | (((handle) & ACPI_NFIT_MEMORY_ID_MASK) >> ACPI_NFIT_MEMORY_ID_OFFSET) |

◆ ACPI_NFIT_GET_NODE_ID

| #define ACPI_NFIT_GET_NODE_ID | ( | handle | ) | (((handle) & ACPI_NFIT_NODE_ID_MASK) >> ACPI_NFIT_NODE_ID_OFFSET) |

◆ ACPI_NFIT_GET_SOCKET_ID

| #define ACPI_NFIT_GET_SOCKET_ID | ( | handle | ) | (((handle) & ACPI_NFIT_SOCKET_ID_MASK) >> ACPI_NFIT_SOCKET_ID_OFFSET) |

◆ ACPI_NFIT_LOCATION_COOKIE_VALID

◆ ACPI_NFIT_MEM_FLUSH_FAILED

| #define ACPI_NFIT_MEM_FLUSH_FAILED (1<<2) /* 02: Platform flush failed */ |

◆ ACPI_NFIT_MEM_HEALTH_ENABLED

◆ ACPI_NFIT_MEM_HEALTH_OBSERVED

◆ ACPI_NFIT_MEM_MAP_FAILED

◆ ACPI_NFIT_MEM_NOT_ARMED

◆ ACPI_NFIT_MEM_RESTORE_FAILED

◆ ACPI_NFIT_MEM_SAVE_FAILED

◆ ACPI_NFIT_MEMORY_ID_MASK

◆ ACPI_NFIT_MEMORY_ID_OFFSET

◆ ACPI_NFIT_NODE_ID_MASK

◆ ACPI_NFIT_NODE_ID_OFFSET

◆ ACPI_NFIT_PROXIMITY_VALID

◆ ACPI_NFIT_SOCKET_ID_MASK

◆ ACPI_NFIT_SOCKET_ID_OFFSET

◆ ACPI_NHLT_ARRAY_TYPE_EXT_MASK

◆ ACPI_NHLT_ARRAY_TYPE_MASK

◆ ACPI_NHLT_ARRAY_TYPE_RESERVED

◆ ACPI_NHLT_BIG_LINEAR_2ELEMENT

◆ ACPI_NHLT_BT_SIDEBAND

◆ ACPI_NHLT_CONFIG_TYPE_GENERIC

◆ ACPI_NHLT_CONFIG_TYPE_MIC_ARRAY

◆ ACPI_NHLT_CONFIG_TYPE_RENDER_FEEDBACK

◆ ACPI_NHLT_CONFIG_TYPE_RESERVED

◆ ACPI_NHLT_DIR_CAPTURE

◆ ACPI_NHLT_DIR_RENDER

◆ ACPI_NHLT_DIR_RENDER_FEEDBACK

◆ ACPI_NHLT_DIR_RENDER_LOOPBACK

◆ ACPI_NHLT_DIR_RESERVED

◆ ACPI_NHLT_FIRST_GEOMETRY_LINEAR_4ELEMENT

◆ ACPI_NHLT_GENERIC

◆ ACPI_NHLT_I2S_TDM_CODECS

◆ ACPI_NHLT_LINK_BT_SIDEBAND

◆ ACPI_NHLT_LINK_FM

◆ ACPI_NHLT_LINK_MODEM

◆ ACPI_NHLT_LINK_SSP_ANALOG_CODEC

◆ ACPI_NHLT_MIC

◆ ACPI_NHLT_MIC_8_SHAPED

◆ ACPI_NHLT_MIC_CARDIOID

◆ ACPI_NHLT_MIC_HYPER_CARDIOID

◆ ACPI_NHLT_MIC_OMNIDIRECTIONAL

◆ ACPI_NHLT_MIC_POSITION_BACK

◆ ACPI_NHLT_MIC_POSITION_BOTTOM

◆ ACPI_NHLT_MIC_POSITION_FRONT

◆ ACPI_NHLT_MIC_POSITION_LEFT

◆ ACPI_NHLT_MIC_POSITION_RESERVED

◆ ACPI_NHLT_MIC_POSITION_RIGHT

◆ ACPI_NHLT_MIC_POSITION_TOP

◆ ACPI_NHLT_MIC_RESERVED

◆ ACPI_NHLT_MIC_RESERVED6

◆ ACPI_NHLT_MIC_SNR_SENSITIVITY_EXT

◆ ACPI_NHLT_MIC_SUBCARDIOID

◆ ACPI_NHLT_MIC_SUPER_CARDIOID

◆ ACPI_NHLT_MIC_VENDOR_DEFINED

◆ ACPI_NHLT_NO_EXTENSION

◆ ACPI_NHLT_PDM

◆ ACPI_NHLT_PDM_DMIC

◆ ACPI_NHLT_PDM_ON_CAVS_1P5

◆ ACPI_NHLT_PDM_ON_CAVS_1P8

◆ ACPI_NHLT_PLANAR_LSHAPED_4ELEMENT

◆ ACPI_NHLT_RENDER

◆ ACPI_NHLT_RESERVED_DSP

◆ ACPI_NHLT_RESERVED_HD_AUDIO

◆ ACPI_NHLT_RESERVED_SLIMBUS

◆ ACPI_NHLT_RESERVED_SOUNDWIRE

◆ ACPI_NHLT_SECOND_GEOMETRY_LINEAR_4ELEMENT

◆ ACPI_NHLT_SMALL_LINEAR_2ELEMENT

◆ ACPI_NHLT_SPKR_BACK_CENTER

◆ ACPI_NHLT_SPKR_BACK_LEFT

◆ ACPI_NHLT_SPKR_BACK_RIGHT

◆ ACPI_NHLT_SPKR_FRONT_CENTER

◆ ACPI_NHLT_SPKR_FRONT_LEFT

◆ ACPI_NHLT_SPKR_FRONT_LEFT_OF_CENTER

◆ ACPI_NHLT_SPKR_FRONT_RIGHT

◆ ACPI_NHLT_SPKR_FRONT_RIGHT_OF_CENTER

◆ ACPI_NHLT_SPKR_LOW_FREQ

◆ ACPI_NHLT_SPKR_SIDE_LEFT

◆ ACPI_NHLT_SPKR_SIDE_RIGHT

◆ ACPI_NHLT_SPKR_TOP_BACK_CENTER

◆ ACPI_NHLT_SPKR_TOP_BACK_LEFT

◆ ACPI_NHLT_SPKR_TOP_BACK_RIGHT

◆ ACPI_NHLT_SPKR_TOP_CENTER

◆ ACPI_NHLT_SPKR_TOP_FRONT_CENTER

◆ ACPI_NHLT_SPKR_TOP_FRONT_LEFT

◆ ACPI_NHLT_SPKR_TOP_FRONT_RIGHT

◆ ACPI_NHLT_SSP

◆ ACPI_NHLT_TYPE_RESERVED

◆ ACPI_NHLT_VENDOR_DEFINED

◆ ACPI_PCCT_DOORBELL

◆ ACPI_PCCT_INTERRUPT_MODE

◆ ACPI_PCCT_INTERRUPT_POLARITY

◆ ACPI_PDTT_RUNTIME_TRIGGER

◆ ACPI_PDTT_TRIGGER_ORDER

◆ ACPI_PDTT_WAIT_COMPLETION

◆ ACPI_PHAT_ADVISORY

◆ ACPI_PHAT_ERRORS_FOUND

◆ ACPI_PHAT_NO_ERRORS

◆ ACPI_PHAT_TYPE_FW_HEALTH_DATA

◆ ACPI_PHAT_TYPE_FW_VERSION_DATA

◆ ACPI_PHAT_TYPE_RESERVED

◆ ACPI_PHAT_UNKNOWN_ERRORS

◆ ACPI_PMTT_MEMORY_TYPE

◆ ACPI_PMTT_PHYSICAL

◆ ACPI_PMTT_TOP_LEVEL

◆ ACPI_PMTT_TYPE_CONTROLLER

◆ ACPI_PMTT_TYPE_DIMM

◆ ACPI_PMTT_TYPE_RESERVED

◆ ACPI_PMTT_TYPE_SOCKET

◆ ACPI_PMTT_TYPE_VENDOR

◆ ACPI_PPTT_ACPI_IDENTICAL

◆ ACPI_PPTT_ACPI_LEAF_NODE

◆ ACPI_PPTT_ACPI_PROCESSOR_ID_VALID

◆ ACPI_PPTT_ACPI_PROCESSOR_IS_THREAD

◆ ACPI_PPTT_ALLOCATION_TYPE_VALID

| #define ACPI_PPTT_ALLOCATION_TYPE_VALID (1<<3) /* Allocation type valid */ |

◆ ACPI_PPTT_ASSOCIATIVITY_VALID

◆ ACPI_PPTT_CACHE_ID_VALID

◆ ACPI_PPTT_CACHE_POLICY_WB

◆ ACPI_PPTT_CACHE_POLICY_WT

◆ ACPI_PPTT_CACHE_READ_ALLOCATE

◆ ACPI_PPTT_CACHE_RW_ALLOCATE

◆ ACPI_PPTT_CACHE_RW_ALLOCATE_ALT

| #define ACPI_PPTT_CACHE_RW_ALLOCATE_ALT (0x03) /* Alternate representation of above */ |

◆ ACPI_PPTT_CACHE_TYPE_DATA

◆ ACPI_PPTT_CACHE_TYPE_INSTR

| #define ACPI_PPTT_CACHE_TYPE_INSTR (1<<2) /* Instruction cache */ |

◆ ACPI_PPTT_CACHE_TYPE_UNIFIED

◆ ACPI_PPTT_CACHE_TYPE_UNIFIED_ALT

| #define ACPI_PPTT_CACHE_TYPE_UNIFIED_ALT (3<<2) /* Alternate representation of above */ |

◆ ACPI_PPTT_CACHE_TYPE_VALID

◆ ACPI_PPTT_CACHE_WRITE_ALLOCATE

◆ ACPI_PPTT_LINE_SIZE_VALID

◆ ACPI_PPTT_MASK_ALLOCATION_TYPE

| #define ACPI_PPTT_MASK_ALLOCATION_TYPE (0x03) /* Allocation type */ |

◆ ACPI_PPTT_MASK_CACHE_TYPE

◆ ACPI_PPTT_MASK_WRITE_POLICY

◆ ACPI_PPTT_NUMBER_OF_SETS_VALID

◆ ACPI_PPTT_PHYSICAL_PACKAGE

◆ ACPI_PPTT_SIZE_PROPERTY_VALID

◆ ACPI_PPTT_WRITE_POLICY_VALID

◆ ACPI_RASF_COMMAND_COMPLETE

◆ ACPI_RASF_ERROR

◆ ACPI_RASF_GENERATE_SCI

◆ ACPI_RASF_SCI_DOORBELL

◆ ACPI_RASF_SCRUBBER_RUNNING

◆ ACPI_RASF_SPEED

◆ ACPI_RASF_SPEED_FAST

◆ ACPI_RASF_SPEED_MEDIUM

◆ ACPI_RASF_SPEED_SLOW

◆ ACPI_RASF_STATUS

◆ ACPI_SDEV_HANDOFF_TO_UNSECURE_OS

◆ ACPI_SDEV_SECURE_COMPONENTS_PRESENT

◆ ACPI_SIG_AGDI

◆ ACPI_SIG_APMT

◆ ACPI_SIG_BDAT

◆ ACPI_SIG_CCEL

◆ ACPI_SIG_CDAT

◆ ACPI_SIG_IORT

◆ ACPI_SIG_IVRS

◆ ACPI_SIG_LPIT

◆ ACPI_SIG_MADT

| #define ACPI_SIG_MADT "APIC" /* Multiple APIC Description Table */ |

◆ ACPI_SIG_MCFG

| #define ACPI_SIG_MCFG "MCFG" /* PCI Memory Mapped Configuration table */ |

◆ ACPI_SIG_MCHI

◆ ACPI_SIG_MPST

◆ ACPI_SIG_MSDM

◆ ACPI_SIG_NFIT

◆ ACPI_SIG_NHLT

◆ ACPI_SIG_PCCT

◆ ACPI_SIG_PDTT

◆ ACPI_SIG_PHAT

◆ ACPI_SIG_PMTT

◆ ACPI_SIG_PPTT

◆ ACPI_SIG_PRMT

◆ ACPI_SIG_RASF

◆ ACPI_SIG_RGRT

◆ ACPI_SIG_SBST

◆ ACPI_SIG_SDEI

◆ ACPI_SIG_SDEV

◆ ACPI_SIG_SVKL

◆ ACPI_SIG_TDEL

Typedef Documentation

◆ ACPI_AEST_GIC

| typedef struct acpi_aest_gic ACPI_AEST_GIC |

◆ ACPI_AEST_HEADER

| typedef struct acpi_aest_hdr ACPI_AEST_HEADER |

◆ ACPI_AEST_MEMORY

| typedef struct acpi_aest_memory ACPI_AEST_MEMORY |

◆ ACPI_AEST_NODE_INTERFACE

◆ ACPI_AEST_NODE_INTERRUPT

◆ ACPI_AEST_PROCESSOR

◆ ACPI_AEST_PROCESSOR_CACHE

◆ ACPI_AEST_PROCESSOR_GENERIC

◆ ACPI_AEST_PROCESSOR_TLB

◆ ACPI_AEST_SMMU

| typedef struct acpi_aest_smmu ACPI_AEST_SMMU |

◆ ACPI_AEST_VENDOR

| typedef struct acpi_aest_vendor ACPI_AEST_VENDOR |

◆ ACPI_APMT_NODE

| typedef struct acpi_apmt_node ACPI_APMT_NODE |

◆ ACPI_IORT_ID_MAPPING

◆ ACPI_IORT_ITS_GROUP

◆ ACPI_IORT_MEMORY_ACCESS

◆ ACPI_IORT_NAMED_COMPONENT

◆ ACPI_IORT_NODE

| typedef struct acpi_iort_node ACPI_IORT_NODE |

◆ ACPI_IORT_PMCG

| typedef struct acpi_iort_pmcg ACPI_IORT_PMCG |

◆ ACPI_IORT_RMR

| typedef struct acpi_iort_rmr ACPI_IORT_RMR |

◆ ACPI_IORT_RMR_DESC

◆ ACPI_IORT_ROOT_COMPLEX

◆ ACPI_IORT_SMMU

| typedef struct acpi_iort_smmu ACPI_IORT_SMMU |

◆ ACPI_IORT_SMMU_GSI

◆ ACPI_IORT_SMMU_V3

| typedef struct acpi_iort_smmu_v3 ACPI_IORT_SMMU_V3 |

◆ ACPI_IVRS_DE_HEADER

◆ ACPI_IVRS_DEVICE4

| typedef struct acpi_ivrs_device4 ACPI_IVRS_DEVICE4 |

◆ ACPI_IVRS_DEVICE8A

◆ ACPI_IVRS_DEVICE8B

◆ ACPI_IVRS_DEVICE8C

◆ ACPI_IVRS_DEVICE_HID

◆ ACPI_IVRS_HARDWARE1

◆ ACPI_IVRS_HARDWARE2

◆ ACPI_IVRS_HEADER

| typedef struct acpi_ivrs_header ACPI_IVRS_HEADER |

◆ ACPI_IVRS_MEMORY

| typedef struct acpi_ivrs_memory ACPI_IVRS_MEMORY |

◆ ACPI_LPIT_HEADER

| typedef struct acpi_lpit_header ACPI_LPIT_HEADER |

◆ ACPI_LPIT_NATIVE

| typedef struct acpi_lpit_native ACPI_LPIT_NATIVE |

◆ ACPI_MADT_BIO_PIC

| typedef struct acpi_madt_bio_pic ACPI_MADT_BIO_PIC |

◆ ACPI_MADT_CORE_PIC

◆ ACPI_MADT_EIO_PIC

| typedef struct acpi_madt_eio_pic ACPI_MADT_EIO_PIC |

◆ ACPI_MADT_GENERIC_DISTRIBUTOR

◆ ACPI_MADT_GENERIC_INTERRUPT

◆ ACPI_MADT_GENERIC_MSI_FRAME

◆ ACPI_MADT_GENERIC_REDISTRIBUTOR

◆ ACPI_MADT_GENERIC_TRANSLATOR

◆ ACPI_MADT_HT_PIC

| typedef struct acpi_madt_ht_pic ACPI_MADT_HT_PIC |

◆ ACPI_MADT_INTERRUPT_OVERRIDE

◆ ACPI_MADT_INTERRUPT_SOURCE

◆ ACPI_MADT_IO_APIC

| typedef struct acpi_madt_io_apic ACPI_MADT_IO_APIC |

◆ ACPI_MADT_IO_SAPIC

◆ ACPI_MADT_LIO_PIC

| typedef struct acpi_madt_lio_pic ACPI_MADT_LIO_PIC |

◆ ACPI_MADT_LOCAL_APIC

◆ ACPI_MADT_LOCAL_APIC_NMI

◆ ACPI_MADT_LOCAL_APIC_OVERRIDE

◆ ACPI_MADT_LOCAL_SAPIC

◆ ACPI_MADT_LOCAL_X2APIC

◆ ACPI_MADT_LOCAL_X2APIC_NMI

◆ ACPI_MADT_LPC_PIC

| typedef struct acpi_madt_lpc_pic ACPI_MADT_LPC_PIC |

◆ ACPI_MADT_MSI_PIC

| typedef struct acpi_madt_msi_pic ACPI_MADT_MSI_PIC |

◆ ACPI_MADT_MULTIPROC_WAKEUP

◆ ACPI_MADT_MULTIPROC_WAKEUP_MAILBOX

◆ ACPI_MADT_NMI_SOURCE

◆ ACPI_MADT_OEM_DATA

◆ ACPI_MCFG_ALLOCATION

◆ ACPI_MPST_CHANNEL

| typedef struct acpi_mpst_channel ACPI_MPST_CHANNEL |

◆ ACPI_MPST_COMPONENT

◆ ACPI_MPST_DATA_HDR

◆ ACPI_MPST_POWER_DATA

◆ ACPI_MPST_POWER_NODE

◆ ACPI_MPST_POWER_STATE

◆ ACPI_MPST_SHARED

| typedef struct acpi_mpst_shared ACPI_MPST_SHARED |

◆ ACPI_MSCT_PROXIMITY

◆ ACPI_NFIT_CAPABILITIES

◆ ACPI_NFIT_CONTROL_REGION

◆ ACPI_NFIT_DATA_REGION

◆ ACPI_NFIT_FLUSH_ADDRESS

◆ ACPI_NFIT_HEADER

| typedef struct acpi_nfit_header ACPI_NFIT_HEADER |

◆ ACPI_NFIT_INTERLEAVE

◆ ACPI_NFIT_MEMORY_MAP

◆ ACPI_NFIT_SMBIOS

| typedef struct acpi_nfit_smbios ACPI_NFIT_SMBIOS |

◆ ACPI_NFIT_SYSTEM_ADDRESS

◆ ACPI_NHLT_DEVICE_INFO

◆ ACPI_NHLT_DEVICE_INFO_COUNT

◆ ACPI_NHLT_DEVICE_SPECIFIC_CONFIG

◆ ACPI_NHLT_DEVICE_SPECIFIC_CONFIG_A

◆ ACPI_NHLT_DEVICE_SPECIFIC_CONFIG_B

◆ ACPI_NHLT_DEVICE_SPECIFIC_CONFIG_C

◆ ACPI_NHLT_DEVICE_SPECIFIC_CONFIG_D

◆ ACPI_NHLT_DEVICE_SPECIFIC_HDR

◆ ACPI_NHLT_ENDPOINT

◆ ACPI_NHLT_FORMAT_CONFIG

◆ ACPI_NHLT_FORMATS_CONFIG

◆ ACPI_NHLT_MIC_DEVICE_SPECIFIC_CONFIG

◆ ACPI_NHLT_MIC_SNR_SENSITIVITY_EXTENSION

◆ ACPI_NHLT_RENDER_DEVICE_SPECIFIC_CONFIG

◆ ACPI_NHLT_RENDER_FEEDBACK_DEVICE_SPECIFIC_CONFIG

| typedef struct acpi_nhlt_render_feedback_device_specific_config ACPI_NHLT_RENDER_FEEDBACK_DEVICE_SPECIFIC_CONFIG |

◆ ACPI_NHLT_VENDOR_MIC_CONFIG

◆ ACPI_NHLT_VENDOR_MIC_COUNT

◆ ACPI_NHLT_VENDOR_MIC_DEVICE_SPECIFIC_CONFIG

| typedef struct acpi_nhlt_vendor_mic_device_specific_config ACPI_NHLT_VENDOR_MIC_DEVICE_SPECIFIC_CONFIG |

◆ ACPI_NHLT_WAVE_EXTENSIBLE

◆ ACPI_PCCT_EXT_PCC_MASTER

◆ ACPI_PCCT_EXT_PCC_SHARED_MEMORY

◆ ACPI_PCCT_EXT_PCC_SLAVE

◆ ACPI_PCCT_HW_REDUCED

◆ ACPI_PCCT_HW_REDUCED_TYPE2

◆ ACPI_PCCT_HW_REG

| typedef struct acpi_pcct_hw_reg ACPI_PCCT_HW_REG |

◆ ACPI_PCCT_SHARED_MEMORY

◆ ACPI_PCCT_SUBSPACE

◆ ACPI_PDTT_CHANNEL

| typedef struct acpi_pdtt_channel ACPI_PDTT_CHANNEL |

◆ ACPI_PHAT_HEADER

| typedef struct acpi_phat_header ACPI_PHAT_HEADER |

◆ ACPI_PHAT_HEALTH_DATA

◆ ACPI_PHAT_VERSION_DATA

◆ ACPI_PHAT_VERSION_ELEMENT

◆ ACPI_PMTT_CONTROLLER

◆ ACPI_PMTT_HEADER

| typedef struct acpi_pmtt_header ACPI_PMTT_HEADER |

◆ ACPI_PMTT_PHYSICAL_COMPONENT

◆ ACPI_PMTT_SOCKET

| typedef struct acpi_pmtt_socket ACPI_PMTT_SOCKET |

◆ ACPI_PMTT_VENDOR_SPECIFIC

◆ ACPI_PPTT_CACHE

| typedef struct acpi_pptt_cache ACPI_PPTT_CACHE |

◆ ACPI_PPTT_CACHE_V1

◆ ACPI_PPTT_ID

| typedef struct acpi_pptt_id ACPI_PPTT_ID |

◆ ACPI_PPTT_PROCESSOR

◆ ACPI_PRMT_HANDLER_INFO

◆ ACPI_PRMT_MODULE_HEADER

◆ ACPI_PRMT_MODULE_INFO

◆ ACPI_RASF_PARAMETER_BLOCK

◆ ACPI_RASF_PATROL_SCRUB_PARAMETER

◆ ACPI_RASF_SHARED_MEMORY

◆ ACPI_SDEV_COMPONENT

◆ ACPI_SDEV_HEADER

| typedef struct acpi_sdev_header ACPI_SDEV_HEADER |

◆ ACPI_SDEV_ID_COMPONENT

◆ ACPI_SDEV_MEM_COMPONENT

◆ ACPI_SDEV_NAMESPACE

◆ ACPI_SDEV_PCIE

| typedef struct acpi_sdev_pcie ACPI_SDEV_PCIE |

◆ ACPI_SDEV_PCIE_PATH

◆ ACPI_SDEV_SECURE_COMPONENT

◆ ACPI_SVKL_KEY

| typedef struct acpi_svkl_key ACPI_SVKL_KEY |

◆ ACPI_TABLE_AEST

| typedef struct acpi_table_aest ACPI_TABLE_AEST |

◆ ACPI_TABLE_AGDI

| typedef struct acpi_table_agdi ACPI_TABLE_AGDI |

◆ ACPI_TABLE_APMT

| typedef struct acpi_table_apmt ACPI_TABLE_APMT |

◆ ACPI_TABLE_BDAT

| typedef struct acpi_table_bdat ACPI_TABLE_BDAT |

◆ ACPI_TABLE_CCEL

| typedef struct acpi_table_ccel ACPI_TABLE_CCEL |

◆ ACPI_TABLE_IORT

| typedef struct acpi_table_iort ACPI_TABLE_IORT |

◆ ACPI_TABLE_IVRS

| typedef struct acpi_table_ivrs ACPI_TABLE_IVRS |

◆ ACPI_TABLE_LPIT

| typedef struct acpi_table_lpit ACPI_TABLE_LPIT |

◆ ACPI_TABLE_MADT

| typedef struct acpi_table_madt ACPI_TABLE_MADT |

◆ ACPI_TABLE_MCFG

| typedef struct acpi_table_mcfg ACPI_TABLE_MCFG |

◆ ACPI_TABLE_MCHI

| typedef struct acpi_table_mchi ACPI_TABLE_MCHI |

◆ ACPI_TABLE_MPST

| typedef struct acpi_table_mpst ACPI_TABLE_MPST |

◆ ACPI_TABLE_MSCT

| typedef struct acpi_table_msct ACPI_TABLE_MSCT |

◆ ACPI_TABLE_MSDM

| typedef struct acpi_table_msdm ACPI_TABLE_MSDM |

◆ ACPI_TABLE_NFIT

| typedef struct acpi_table_nfit ACPI_TABLE_NFIT |

◆ ACPI_TABLE_NHLT

| typedef struct acpi_table_nhlt ACPI_TABLE_NHLT |

◆ ACPI_TABLE_NHLT_ENDPOINT_COUNT

◆ ACPI_TABLE_PCCT

| typedef struct acpi_table_pcct ACPI_TABLE_PCCT |

◆ ACPI_TABLE_PDTT

| typedef struct acpi_table_pdtt ACPI_TABLE_PDTT |

◆ ACPI_TABLE_PHAT

| typedef struct acpi_table_phat ACPI_TABLE_PHAT |

◆ ACPI_TABLE_PMTT

| typedef struct acpi_table_pmtt ACPI_TABLE_PMTT |

◆ ACPI_TABLE_PPTT

| typedef struct acpi_table_pptt ACPI_TABLE_PPTT |

◆ ACPI_TABLE_PRMT

| typedef struct acpi_table_prmt ACPI_TABLE_PRMT |

◆ ACPI_TABLE_PRMT_HEADER

◆ ACPI_TABLE_RASF

| typedef struct acpi_table_rasf ACPI_TABLE_RASF |

◆ ACPI_TABLE_RGRT

| typedef struct acpi_table_rgrt ACPI_TABLE_RGRT |

◆ ACPI_TABLE_SBST

| typedef struct acpi_table_sbst ACPI_TABLE_SBST |

◆ ACPI_TABLE_SDEI

| typedef struct acpi_table_sdei ACPI_TABLE_SDEI |

◆ ACPI_TABLE_SDEV

| typedef struct acpi_table_sdev ACPI_TABLE_SDEV |

◆ ACPI_TABLE_SVKL

| typedef struct acpi_table_svkl ACPI_TABLE_SVKL |

◆ ACPI_TABLE_TDEL

| typedef struct acpi_table_tdel ACPI_TABLE_TDEL |

◆ NFIT_DEVICE_HANDLE

Enumeration Type Documentation

◆ acpi_apmt_node_type

| Enumerator | |

|---|---|

| ACPI_APMT_NODE_TYPE_MC | |

| ACPI_APMT_NODE_TYPE_SMMU | |

| ACPI_APMT_NODE_TYPE_PCIE_ROOT | |

| ACPI_APMT_NODE_TYPE_ACPI | |

| ACPI_APMT_NODE_TYPE_CACHE | |

| ACPI_APMT_NODE_TYPE_COUNT | |

Definition at line 377 of file actbl2.h.

377 {

378 ACPI_APMT_NODE_TYPE_MC = 0x00,

379 ACPI_APMT_NODE_TYPE_SMMU = 0x01,

380 ACPI_APMT_NODE_TYPE_PCIE_ROOT = 0x02,

381 ACPI_APMT_NODE_TYPE_ACPI = 0x03,

382 ACPI_APMT_NODE_TYPE_CACHE = 0x04,

384};

◆ acpi_svkl_format

| Enumerator | |

|---|---|

| ACPI_SVKL_FORMAT_RAW_BINARY | |

| ACPI_SVKL_FORMAT_RESERVED | |

◆ acpi_svkl_type

| Enumerator | |

|---|---|

| ACPI_SVKL_TYPE_MAIN_STORAGE | |

| ACPI_SVKL_TYPE_RESERVED | |

◆ AcpiIortNodeType

| Enumerator | |

|---|---|

| ACPI_IORT_NODE_ITS_GROUP | |

| ACPI_IORT_NODE_NAMED_COMPONENT | |

| ACPI_IORT_NODE_PCI_ROOT_COMPLEX | |

| ACPI_IORT_NODE_SMMU | |

| ACPI_IORT_NODE_SMMU_V3 | |

| ACPI_IORT_NODE_PMCG | |

| ACPI_IORT_NODE_RMR | |

Definition at line 472 of file actbl2.h.

473{

474 ACPI_IORT_NODE_ITS_GROUP = 0x00,

475 ACPI_IORT_NODE_NAMED_COMPONENT = 0x01,

476 ACPI_IORT_NODE_PCI_ROOT_COMPLEX = 0x02,

477 ACPI_IORT_NODE_SMMU = 0x03,

478 ACPI_IORT_NODE_SMMU_V3 = 0x04,

479 ACPI_IORT_NODE_PMCG = 0x05,

480 ACPI_IORT_NODE_RMR = 0x06,

481};

◆ AcpiIvrsDeviceEntryType

Definition at line 804 of file actbl2.h.

805{

806 /* 4-byte device entries, all use ACPI_IVRS_DEVICE4 */

807

808 ACPI_IVRS_TYPE_PAD4 = 0,

809 ACPI_IVRS_TYPE_ALL = 1,

810 ACPI_IVRS_TYPE_SELECT = 2,

811 ACPI_IVRS_TYPE_START = 3,

812 ACPI_IVRS_TYPE_END = 4,

813

814 /* 8-byte device entries */

815

816 ACPI_IVRS_TYPE_PAD8 = 64,

817 ACPI_IVRS_TYPE_NOT_USED = 65,

823

824 /* Variable-length device entries */

825

827};

◆ AcpiIvrsType

| Enumerator | |

|---|---|

| ACPI_IVRS_TYPE_HARDWARE1 | |

| ACPI_IVRS_TYPE_HARDWARE2 | |

| ACPI_IVRS_TYPE_HARDWARE3 | |

| ACPI_IVRS_TYPE_MEMORY1 | |

| ACPI_IVRS_TYPE_MEMORY2 | |

| ACPI_IVRS_TYPE_MEMORY3 | |

Definition at line 721 of file actbl2.h.

722{

723 ACPI_IVRS_TYPE_HARDWARE1 = 0x10,

724 ACPI_IVRS_TYPE_HARDWARE2 = 0x11,

725 ACPI_IVRS_TYPE_HARDWARE3 = 0x40,

726 ACPI_IVRS_TYPE_MEMORY1 = 0x20,

727 ACPI_IVRS_TYPE_MEMORY2 = 0x21,

728 ACPI_IVRS_TYPE_MEMORY3 = 0x22

729};

◆ AcpiLpitType

| Enumerator | |

|---|---|

| ACPI_LPIT_TYPE_NATIVE_CSTATE | |

| ACPI_LPIT_TYPE_RESERVED | |

◆ AcpiMadtBioPicVersion

| Enumerator | |

|---|---|

| ACPI_MADT_BIO_PIC_VERSION_NONE | |

| ACPI_MADT_BIO_PIC_VERSION_V1 | |

| ACPI_MADT_BIO_PIC_VERSION_RESERVED | |

◆ AcpiMadtCorePicVersion

| Enumerator | |

|---|---|

| ACPI_MADT_CORE_PIC_VERSION_NONE | |

| ACPI_MADT_CORE_PIC_VERSION_V1 | |

| ACPI_MADT_CORE_PIC_VERSION_RESERVED | |

◆ AcpiMadtEioPicVersion

| Enumerator | |

|---|---|

| ACPI_MADT_EIO_PIC_VERSION_NONE | |

| ACPI_MADT_EIO_PIC_VERSION_V1 | |

| ACPI_MADT_EIO_PIC_VERSION_RESERVED | |

◆ AcpiMadtGicVersion

| Enumerator | |

|---|---|

| ACPI_MADT_GIC_VERSION_NONE | |

| ACPI_MADT_GIC_VERSION_V1 | |

| ACPI_MADT_GIC_VERSION_V2 | |

| ACPI_MADT_GIC_VERSION_V3 | |

| ACPI_MADT_GIC_VERSION_V4 | |

| ACPI_MADT_GIC_VERSION_RESERVED | |

Definition at line 1232 of file actbl2.h.

1233{

1234 ACPI_MADT_GIC_VERSION_NONE = 0,

1235 ACPI_MADT_GIC_VERSION_V1 = 1,

1236 ACPI_MADT_GIC_VERSION_V2 = 2,

1237 ACPI_MADT_GIC_VERSION_V3 = 3,

1238 ACPI_MADT_GIC_VERSION_V4 = 4,

1240};

◆ AcpiMadtHtPicVersion

| Enumerator | |

|---|---|

| ACPI_MADT_HT_PIC_VERSION_NONE | |

| ACPI_MADT_HT_PIC_VERSION_V1 | |

| ACPI_MADT_HT_PIC_VERSION_RESERVED | |

◆ AcpiMadtLioPicVersion

| Enumerator | |

|---|---|

| ACPI_MADT_LIO_PIC_VERSION_NONE | |

| ACPI_MADT_LIO_PIC_VERSION_V1 | |

| ACPI_MADT_LIO_PIC_VERSION_RESERVED | |

◆ AcpiMadtLpcPicVersion

| Enumerator | |

|---|---|

| ACPI_MADT_LPC_PIC_VERSION_NONE | |

| ACPI_MADT_LPC_PIC_VERSION_V1 | |

| ACPI_MADT_LPC_PIC_VERSION_RESERVED | |

◆ AcpiMadtMsiPicVersion

| Enumerator | |

|---|---|

| ACPI_MADT_MSI_PIC_VERSION_NONE | |

| ACPI_MADT_MSI_PIC_VERSION_V1 | |

| ACPI_MADT_MSI_PIC_VERSION_RESERVED | |

◆ AcpiMadtType

Definition at line 1003 of file actbl2.h.

1004{

1005 ACPI_MADT_TYPE_LOCAL_APIC = 0,

1006 ACPI_MADT_TYPE_IO_APIC = 1,

1007 ACPI_MADT_TYPE_INTERRUPT_OVERRIDE = 2,

1008 ACPI_MADT_TYPE_NMI_SOURCE = 3,

1009 ACPI_MADT_TYPE_LOCAL_APIC_NMI = 4,

1010 ACPI_MADT_TYPE_LOCAL_APIC_OVERRIDE = 5,

1011 ACPI_MADT_TYPE_IO_SAPIC = 6,

1012 ACPI_MADT_TYPE_LOCAL_SAPIC = 7,

1013 ACPI_MADT_TYPE_INTERRUPT_SOURCE = 8,

1014 ACPI_MADT_TYPE_LOCAL_X2APIC = 9,

1015 ACPI_MADT_TYPE_LOCAL_X2APIC_NMI = 10,

1016 ACPI_MADT_TYPE_GENERIC_INTERRUPT = 11,

1017 ACPI_MADT_TYPE_GENERIC_DISTRIBUTOR = 12,

1018 ACPI_MADT_TYPE_GENERIC_MSI_FRAME = 13,

1019 ACPI_MADT_TYPE_GENERIC_REDISTRIBUTOR = 14,

1020 ACPI_MADT_TYPE_GENERIC_TRANSLATOR = 15,

1021 ACPI_MADT_TYPE_MULTIPROC_WAKEUP = 16,

1022 ACPI_MADT_TYPE_CORE_PIC = 17,

1023 ACPI_MADT_TYPE_LIO_PIC = 18,

1024 ACPI_MADT_TYPE_HT_PIC = 19,

1025 ACPI_MADT_TYPE_EIO_PIC = 20,

1026 ACPI_MADT_TYPE_MSI_PIC = 21,

1027 ACPI_MADT_TYPE_BIO_PIC = 22,

1028 ACPI_MADT_TYPE_LPC_PIC = 23,

1031};

◆ AcpiNfitType

Definition at line 1729 of file actbl2.h.

1730{

1731 ACPI_NFIT_TYPE_SYSTEM_ADDRESS = 0,

1732 ACPI_NFIT_TYPE_MEMORY_MAP = 1,

1733 ACPI_NFIT_TYPE_INTERLEAVE = 2,

1734 ACPI_NFIT_TYPE_SMBIOS = 3,

1735 ACPI_NFIT_TYPE_CONTROL_REGION = 4,

1736 ACPI_NFIT_TYPE_DATA_REGION = 5,

1737 ACPI_NFIT_TYPE_FLUSH_ADDRESS = 6,

1738 ACPI_NFIT_TYPE_CAPABILITIES = 7,

1740};

◆ AcpiPcctType

Definition at line 2301 of file actbl2.h.

2302{

2303 ACPI_PCCT_TYPE_GENERIC_SUBSPACE = 0,

2304 ACPI_PCCT_TYPE_HW_REDUCED_SUBSPACE = 1,

2310};

@ ACPI_PCCT_TYPE_EXT_PCC_SLAVE_SUBSPACE

Definition: actbl2.h:2307

@ ACPI_PCCT_TYPE_EXT_PCC_MASTER_SUBSPACE

Definition: actbl2.h:2306

@ ACPI_PCCT_TYPE_HW_REDUCED_SUBSPACE_TYPE2

Definition: actbl2.h:2305

◆ AcpiPpttType

| Enumerator | |

|---|---|

| ACPI_PPTT_TYPE_PROCESSOR | |

| ACPI_PPTT_TYPE_CACHE | |

| ACPI_PPTT_TYPE_ID | |

| ACPI_PPTT_TYPE_RESERVED | |

Definition at line 2729 of file actbl2.h.

2730{

2731 ACPI_PPTT_TYPE_PROCESSOR = 0,

2732 ACPI_PPTT_TYPE_CACHE = 1,

2733 ACPI_PPTT_TYPE_ID = 2,

2734 ACPI_PPTT_TYPE_RESERVED = 3

2735};

◆ AcpiRasfCapabiliities

| Enumerator | |

|---|---|

| ACPI_HW_PATROL_SCRUB_SUPPORTED | |

| ACPI_SW_PATROL_SCRUB_EXPOSED | |

◆ AcpiRasfCommands

| Enumerator | |

|---|---|

| ACPI_RASF_EXECUTE_RASF_COMMAND | |

◆ AcpiRasfPatrolScrubCommands

| Enumerator | |

|---|---|

| ACPI_RASF_GET_PATROL_PARAMETERS | |

| ACPI_RASF_START_PATROL_SCRUBBER | |

| ACPI_RASF_STOP_PATROL_SCRUBBER | |

Definition at line 2962 of file actbl2.h.

2963{

2964 ACPI_RASF_GET_PATROL_PARAMETERS = 1,

2965 ACPI_RASF_START_PATROL_SCRUBBER = 2,

2966 ACPI_RASF_STOP_PATROL_SCRUBBER = 3

2967};

◆ AcpiRasfStatus

| Enumerator | |

|---|---|

| ACPI_RASF_SUCCESS | |

| ACPI_RASF_NOT_VALID | |

| ACPI_RASF_NOT_SUPPORTED | |

| ACPI_RASF_BUSY | |

| ACPI_RASF_FAILED | |

| ACPI_RASF_ABORTED | |

| ACPI_RASF_INVALID_DATA | |

Definition at line 2975 of file actbl2.h.

2976{

2977 ACPI_RASF_SUCCESS = 0,

2978 ACPI_RASF_NOT_VALID = 1,

2979 ACPI_RASF_NOT_SUPPORTED = 2,

2980 ACPI_RASF_BUSY = 3,

2981 ACPI_RASF_FAILED = 4,

2982 ACPI_RASF_ABORTED = 5,

2983 ACPI_RASF_INVALID_DATA = 6

2984};

◆ AcpiRgrtImageType

| Enumerator | |

|---|---|

| ACPI_RGRT_TYPE_RESERVED0 | |

| ACPI_RGRT_IMAGE_TYPE_PNG | |

| ACPI_RGRT_TYPE_RESERVED | |

◆ AcpiSacType

| Enumerator | |

|---|---|

| ACPI_SDEV_TYPE_ID_COMPONENT | |

| ACPI_SDEV_TYPE_MEM_COMPONENT | |

◆ AcpiSdevType

| Enumerator | |

|---|---|

| ACPI_SDEV_TYPE_NAMESPACE_DEVICE | |

| ACPI_SDEV_TYPE_PCIE_ENDPOINT_DEVICE | |

| ACPI_SDEV_TYPE_RESERVED | |

Definition at line 3082 of file actbl2.h.

3083{

3084 ACPI_SDEV_TYPE_NAMESPACE_DEVICE = 0,

3085 ACPI_SDEV_TYPE_PCIE_ENDPOINT_DEVICE = 1,

3087};