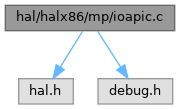

#include <hal.h>

#include <debug.h>

Go to the source code of this file.

◆ default_EISA_polarity

◆ default_EISA_trigger

◆ default_ISA_polarity

◆ default_ISA_trigger

◆ default_MCA_polarity

◆ default_MCA_trigger

◆ default_PCI_polarity

◆ default_PCI_trigger

◆ NDEBUG

◆ AssignIrqVector()

Definition at line 237 of file ioapic.c.

238{

239#if 0

240 static ULONG current_vector = FIRST_DEVICE_VECTOR, vector_offset = 0;

241#endif

243

246 {

248 }

249#if 0

250 if (current_vector > FIRST_SYSTEM_VECTOR)

251 {

252 vector_offset++;

253 current_vector = FIRST_DEVICE_VECTOR + vector_offset;

254 }

255 else if (current_vector == FIRST_SYSTEM_VECTOR)

256 {

257 DPRINT1(

"Ran out of interrupt sources\n");

259 }

260

263 current_vector += 8;

265#else

269#endif

270}

ULONG IRQVectorMap[MAX_IRQ_SOURCE]

Referenced by IOAPICSetupIrqs().

◆ Disable8259AIrq()

Definition at line 658 of file ioapic.c.

659{

661

663 {

665 tmp |= (1 << (

irq - 8));

667 }

668 else

669 {

673 }

674}

#define READ_PORT_UCHAR(p)

#define WRITE_PORT_UCHAR(p, d)

Referenced by IOAPICSetupIrqs().

◆ EISA_ELCR_Read()

Definition at line 66 of file ioapic.c.

67{

69 {

72 }

73 DPRINT1(

"Broken MPtable reports ISA irq %lu\n",

irq);

74 return 0;

75}

◆ HaliReconfigurePciInterrupts()

| VOID HaliReconfigurePciInterrupts |

( |

VOID |

| ) |

|

Definition at line 634 of file ioapic.c.

635{

637

639 {

641 {

642 DPRINT(

"%02lx: IrqType %02x, IrqFlag %04x, SrcBusId %02x"

643 ", SrcBusIrq %02x, DstApicId %02x, DstApicInt %02x\n",

646

649 (

IRQMap[

i].SrcBusIrq >> 2) & 0x1f,

651 0x3c ,

652 1);

653

654 }

655 }

656}

GLsizei GLenum const GLvoid GLsizei GLenum GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLint GLint GLint GLshort GLshort GLshort GLubyte GLubyte GLubyte GLuint GLuint GLuint GLushort GLushort GLushort GLbyte GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLfloat GLint GLint GLint GLint GLshort GLshort GLshort GLshort GLubyte GLubyte GLubyte GLubyte GLuint GLuint GLuint GLuint GLushort GLushort GLushort GLushort GLboolean const GLdouble const GLfloat const GLint const GLshort const GLbyte const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLdouble const GLfloat const GLfloat const GLint const GLint const GLshort const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort GLenum GLenum GLenum GLfloat GLenum GLint GLenum GLenum GLenum GLfloat GLenum GLenum GLint GLenum GLfloat GLenum GLint GLint GLushort GLenum GLenum GLfloat GLenum GLenum GLint GLfloat const GLubyte GLenum GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLint GLint GLsizei GLsizei GLint GLenum GLenum const GLvoid GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLenum const GLdouble GLenum GLenum const GLfloat GLenum GLenum const GLint GLsizei GLuint GLfloat GLuint GLbitfield GLfloat GLint GLuint GLboolean GLenum GLfloat GLenum GLbitfield GLenum GLfloat GLfloat GLint GLint const GLfloat GLenum GLfloat GLfloat GLint GLint GLfloat GLfloat GLint GLint const GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat const GLdouble const GLfloat const GLdouble const GLfloat GLint i

ULONG NTAPI HalSetBusDataByOffset(IN BUS_DATA_TYPE BusDataType, IN ULONG BusNumber, IN ULONG SlotNumber, IN PVOID Buffer, IN ULONG Offset, IN ULONG Length)

MP_CONFIGURATION_INTSRC IRQMap[MAX_IRQ_SOURCE]

◆ IOAPICClear()

Definition at line 387 of file ioapic.c.

388{

390

392 {

394 }

395}

IN PDCB IN VBO IN ULONG IN BOOLEAN Pin

static VOID IOAPICClearPin(ULONG Apic, ULONG Pin)

Referenced by IOAPICClearAll().

◆ IOAPICClearAll()

Definition at line 398 of file ioapic.c.

399{

401

403 {

405 }

406}

static VOID IOAPICClear(ULONG Apic)

Referenced by IOAPICEnable().

◆ IOAPICClearPin()

Definition at line 371 of file ioapic.c.

372{

374

375 DPRINT(

"IOAPICClearPin(Apic %lu, Pin %lu\n", Apic,

Pin);

376

377

378

381

384}

VOID IOAPICWrite(ULONG Apic, ULONG Offset, ULONG Value)

Referenced by IOAPICClear().

◆ IOAPICDump()

Definition at line 524 of file ioapic.c.

525{

527 ULONG reg0, reg1, reg2=0;

528

531 {

532 DbgPrint(

"Number of IO-APIC #%d registers: %d.\n",

535 }

536

537

538

539

540

541 DbgPrint(

"Testing the IO APIC.......................\n");

542

544 {

548 {

550 }

551

554 DbgPrint(

".... register #00: %08X\n", reg0);

556 if (reg0 & 0xF0FFFFFF)

557 {

558 DbgPrint(

" WARNING: Unexpected IO-APIC\n");

559 }

560

561 DbgPrint(

".... register #01: %08X\n", reg1);

563

564 DbgPrint(

"....... : max redirection entries: %04X\n",

i);

572 {

573 DbgPrint(

" WARNING: Unexpected IO-APIC\n");

574 }

575

577 DbgPrint(

"....... : IO APIC version: %04X\n",

i);

582 {

583 DbgPrint(

" WARNING: Unexpected IO-APIC\n");

584 }

585

586 if (reg1 & 0xFF00FF00)

587 {

588 DbgPrint(

" WARNING: Unexpected IO-APIC\n");

589 }

590

592 {

593 DbgPrint(

".... register #02: %08X\n", reg2);

594 DbgPrint(

"....... : arbitration: %02X\n",

596 if (reg2 & 0xF0FFFFFF)

597 {

598 DbgPrint(

" WARNING: Unexpected IO-APIC\n");

599 }

600 }

601

602 DbgPrint(

".... IRQ redirection table:\n");

603 DbgPrint(

" NR Log Phy Mask Trig IRR Pol"

604 " Stat Dest Deli Vect: \n");

605

607 {

609

612

615 entry.dest.logical.logical_dest,

616 entry.dest.physical.physical_dest);

617

618 DbgPrint(

"%C %C %1d %C %C %C %03X %02X\n",

619 (

entry.mask == 0) ?

'U' :

'M',

620 (

entry.trigger == 0) ?

'E' :

'L',

622 (

entry.polarity == 0) ?

'H' :

'L',

623 (

entry.delivery_status == 0) ?

'I' :

'S',

624 (

entry.dest_mode == 0) ?

'P' :

'L',

627 }

628 }

629

630 DbgPrint(

".................................... done.\n");

631}

IOAPIC_INFO IOAPICMap[MAX_IOAPIC]

ULONG IOAPICRead(ULONG Apic, ULONG Offset)

#define GET_IOAPIC_ARB(x)

#define GET_IOAPIC_VERSION(x)

#define GET_IOAPIC_MRE(x)

_Must_inspect_result_ typedef _In_ ULONG ApicId

◆ IOAPICEnable()

◆ IOAPICGetIrqEntry()

Definition at line 276 of file ioapic.c.

279{

281

283 {

287 {

289 }

290 }

291 return -1;

292}

GLuint GLuint GLsizei GLenum type

Referenced by IOAPICSetupIrqs().

◆ IOAPICMaskIrq()

Definition at line 494 of file ioapic.c.

495{

498

502 if (

Entry.dest.logical.logical_dest == 0)

503 {

505 }

508}

ULONG IrqApicMap[MAX_IRQ_SOURCE]

FORCEINLINE ULONG KeGetCurrentProcessorNumber(VOID)

Referenced by HalDisableSystemInterrupt().

◆ IOAPICRead()

◆ IOAPICSetupIds()

Definition at line 432 of file ioapic.c.

433{

436

437

438

439

441 {

442

443

445

447

449 {

453 }

454

455

456

457

458

460 {

462 {

463 if (

IRQMap[

i].DstApicId == old_id)

464 {

466 }

467 }

468 }

469

470

471

472

473

475

476 tmp &= ~IOAPIC_ID_MASK;

478

480

481

482

483

486 {

487 DPRINT1(

"Could not set I/O APIC ID!\n");

489 }

490 }

491}

Referenced by HalAllProcessorsStarted().

◆ IOAPICSetupIrqs()

Definition at line 296 of file ioapic.c.

297{

300

301 DPRINT(

"Init IO_APIC IRQs\n");

302

303

305

307 {

309 {

310

311

312

314

315 entry.delivery_mode = (APIC_DM_LOWEST >> 8);

318 entry.dest.logical.logical_dest = 0;

319

322 {

323 if (first_notcon)

324 {

326 first_notcon = 0;

327 }

328 else

329 {

331 }

332 continue;

333 }

334

337

338 if (trigger)

339 {

341 }

342

344

347

349

351 {

352

354 }

355

356 if ((apic == 0) && (

irq < 16))

357 {

359 }

362

364

366 }

367 }

368}

static ULONG Pin2Irq(ULONG idx, ULONG apic, ULONG pin)

static ULONG IOAPICGetIrqEntry(ULONG apic, ULONG pin, ULONG type)

static ULONG IRQPolarity(ULONG idx)

static ULONG IRQTrigger(ULONG idx)

VOID Disable8259AIrq(ULONG irq)

static ULONG AssignIrqVector(ULONG irq)

Referenced by HalAllProcessorsStarted().

◆ IOAPICUnmaskIrq()

◆ IOAPICWrite()

◆ IRQPolarity()

Definition at line 78 of file ioapic.c.

79{

82

83

84

85

87 {

88 case 0:

89 {

91 {

94 break;

95

98 break;

99

102 break;

103

106 break;

107

108 default:

110 polarity = 1;

111 }

112 }

113 break;

114

115 case 1:

116 polarity = 0;

117 break;

118

119 case 2:

121 polarity = 1;

122 break;

123

124 case 3:

125 polarity = 1;

126 break;

127

128 default:

130 polarity = 1;

131 }

132 return polarity;

133}

#define default_EISA_polarity(idx)

#define default_MCA_polarity(idx)

#define default_ISA_polarity(idx)

#define default_PCI_polarity(idx)

Referenced by IOAPICSetupIrqs().

◆ IRQTrigger()

Definition at line 136 of file ioapic.c.

137{

140

141

142

143

145 {

146 case 0:

147 {

149 {

152 break;

153

156 break;

157

160 break;

161

164 break;

165

166 default:

168 trigger = 1;

169 }

170 }

171 break;

172

173 case 1:

174 trigger = 0;

175 break;

176

177 case 2:

179 trigger = 1;

180 break;

181

182 case 3:

183 trigger = 1;

184 break;

185

186 default:

188 trigger = 0;

189 }

190 return trigger;

191}

#define default_ISA_trigger(idx)

#define default_EISA_trigger(idx)

#define default_MCA_trigger(idx)

#define default_PCI_trigger(idx)

Referenced by IOAPICSetupIrqs().

◆ Pin2Irq()

Definition at line 194 of file ioapic.c.

197{

200

201

202

203

205 {

206 DPRINT1(

"Broken BIOS or MPTABLE parser\n");

207 }

208

210 {

215 break;

216

218

219

220

223 {

225 }

227 break;

228

229 default:

230 DPRINT1(

"Unknown bus type %lu\n", bus);

232 }

234}

Referenced by IOAPICSetupIrqs().

◆ BUSMap

◆ IOAPICCount

◆ IOAPICMap

◆ IrqApicMap

◆ IRQCount

◆ IRQMap

◆ IRQVectorMap

◆ PCIBUSMap