|

ReactOS 0.4.16-dev-1264-g92ff994

|

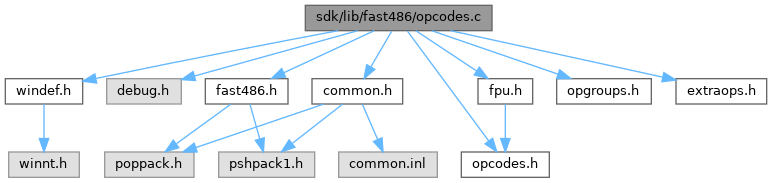

#include <windef.h>#include <debug.h>#include <fast486.h>#include "opcodes.h"#include "opgroups.h"#include "extraops.h"#include "common.h"#include "fpu.h"

Go to the source code of this file.

Functions | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeInvalid) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePrefix) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeIncrement) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeDecrement) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePushReg) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePopReg) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeNop) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeExchangeEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeShortConditionalJmp) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeClearCarry) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeSetCarry) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeComplCarry) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeClearInt) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeSetInt) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeClearDir) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeSetDir) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeHalt) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeInByte) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeIn) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeOutByte) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeOut) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeShortJump) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovRegImm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovByteRegImm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAddByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAddModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAddAl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAddEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeOrByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeOrModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeOrAl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeOrEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAndByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAndModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAndAl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAndEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeXorByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeXorModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeXorAl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeXorEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeTestByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeTestModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeTestAl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeTestEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeXchgByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeXchgModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePushEs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePopEs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePushCs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAdcByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAdcModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAdcAl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAdcEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePushSs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePopSs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeSbbByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeSbbModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeSbbAl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeSbbEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePushDs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePopDs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeDaa) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeCmpSubByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeCmpSubModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeCmpSubAl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeCmpSubEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeDas) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAaa) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAas) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePushAll) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePopAll) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeBound) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeArpl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePushImm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeImulModrmImm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePushByteImm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovByteModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovModrm) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovStoreSeg) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeLea) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovLoadSeg) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeCwde) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeCdq) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeCallAbs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeWait) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePushFlags) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodePopFlags) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeSahf) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeLahf) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeRet) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeLdsLes) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeEnter) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeLeave) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeRetFar) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeInt) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeIret) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAam) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeAad) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeXlat) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeLoop) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeJecxz) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeCall) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeJmp) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeJmpAbs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovAlOffset) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovEaxOffset) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovOffsetAl) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovOffsetEax) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeSalc) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeMovs) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeCmps) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeStos) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeLods) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeScas) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeIns) | |

| FAST486_OPCODE_HANDLER (Fast486OpcodeOuts) | |

Variables | |

| FAST486_OPCODE_HANDLER_PROC | Fast486OpcodeHandlers [FAST486_NUM_OPCODE_HANDLERS] |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAaa | ) |

Definition at line 3150 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAad | ) |

Definition at line 4734 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAam | ) |

Definition at line 4701 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAas | ) |

Definition at line 3177 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAdcAl | ) |

Definition at line 2392 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAdcByteModrm | ) |

Definition at line 2248 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAdcEax | ) |

Definition at line 2428 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAdcModrm | ) |

Definition at line 2298 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAddAl | ) |

Definition at line 1169 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAddByteModrm | ) |

Definition at line 1038 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAddEax | ) |

Definition at line 1201 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAddModrm | ) |

Definition at line 1084 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAndAl | ) |

Definition at line 1605 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAndByteModrm | ) |

Definition at line 1480 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAndEax | ) |

Definition at line 1635 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeAndModrm | ) |

Definition at line 1524 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeArpl | ) |

Definition at line 3368 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeBound | ) |

Definition at line 3272 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeCall | ) |

Definition at line 4856 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeCallAbs | ) |

Definition at line 3910 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeCdq | ) |

Definition at line 3884 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeClearCarry | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeClearDir | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeClearInt | ) |

Definition at line 667 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeCmps | ) |

Definition at line 5368 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeCmpSubAl | ) |

Definition at line 3001 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeCmpSubByteModrm | ) |

Definition at line 2837 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeCmpSubEax | ) |

Definition at line 3037 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeCmpSubModrm | ) |

Definition at line 2894 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeComplCarry | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeCwde | ) |

Definition at line 3855 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeDaa | ) |

Definition at line 2796 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeDas | ) |

Definition at line 3109 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeDecrement | ) |

Definition at line 442 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeEnter | ) |

Definition at line 4209 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeExchangeEax | ) |

Definition at line 507 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeHalt | ) |

Definition at line 749 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeImulModrmImm | ) |

Definition at line 3460 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeIn | ) |

Definition at line 802 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeInByte | ) |

Definition at line 767 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeIncrement | ) |

Definition at line 411 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeIns | ) |

Definition at line 5834 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeInt | ) |

Definition at line 4422 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeInvalid | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeIret | ) |

Definition at line 4477 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeJecxz | ) |

Definition at line 4826 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeJmp | ) |

Definition at line 4910 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeJmpAbs | ) |

Definition at line 4953 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeLahf | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeLdsLes | ) |

Definition at line 4105 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeLea | ) |

Definition at line 3764 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeLeave | ) |

Definition at line 4277 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeLods | ) |

Definition at line 5647 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeLoop | ) |

Definition at line 4785 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovAlOffset | ) |

Definition at line 5010 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovByteModrm | ) |

Definition at line 3599 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovByteRegImm | ) |

Definition at line 1010 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovEaxOffset | ) |

Definition at line 5051 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovLoadSeg | ) |

Definition at line 3810 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovModrm | ) |

Definition at line 3641 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovOffsetAl | ) |

Definition at line 5129 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovOffsetEax | ) |

Definition at line 5169 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovRegImm | ) |

Definition at line 970 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovs | ) |

Definition at line 5259 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeMovStoreSeg | ) |

Definition at line 3720 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeOrAl | ) |

Definition at line 1390 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeOrByteModrm | ) |

Definition at line 1265 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeOrEax | ) |

Definition at line 1420 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeOrModrm | ) |

Definition at line 1309 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeOut | ) |

Definition at line 892 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeOutByte | ) |

Definition at line 857 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeOuts | ) |

Definition at line 5974 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePopAll | ) |

Definition at line 3241 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePopDs | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePopEs | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePopFlags | ) |

Definition at line 4009 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePopReg | ) |

Definition at line 484 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePopSs | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePrefix | ) |

Definition at line 312 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePushAll | ) |

Definition at line 3204 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePushByteImm | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePushCs | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePushDs | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePushEs | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePushFlags | ) |

Definition at line 3989 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePushImm | ) |

Definition at line 3422 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePushReg | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodePushSs | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeRet | ) |

Definition at line 4071 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeRetFar | ) |

Definition at line 4307 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeSahf | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeSalc | ) |

Definition at line 5243 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeSbbAl | ) |

Definition at line 2678 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeSbbByteModrm | ) |

Definition at line 2524 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeSbbEax | ) |

Definition at line 2711 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeSbbModrm | ) |

Definition at line 2578 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeScas | ) |

Definition at line 5722 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeSetCarry | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeSetDir | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeSetInt | ) |

Definition at line 697 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeShortConditionalJmp | ) |

Definition at line 537 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeShortJump | ) |

Definition at line 943 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeStos | ) |

Definition at line 5514 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeTestAl | ) |

Definition at line 2016 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeTestByteModrm | ) |

Definition at line 1910 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeTestEax | ) |

Definition at line 2043 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeTestModrm | ) |

Definition at line 1947 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeWait | ) |

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeXchgByteModrm | ) |

Definition at line 2097 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeXchgModrm | ) |

Definition at line 2141 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeXlat | ) |

Definition at line 4759 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeXorAl | ) |

Definition at line 1820 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeXorByteModrm | ) |

Definition at line 1695 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeXorEax | ) |

Definition at line 1850 of file opcodes.c.

| FAST486_OPCODE_HANDLER | ( | Fast486OpcodeXorModrm | ) |

Definition at line 1739 of file opcodes.c.

| FAST486_OPCODE_HANDLER_PROC Fast486OpcodeHandlers[FAST486_NUM_OPCODE_HANDLERS] |

Definition at line 39 of file opcodes.c.

Referenced by Fast486ExecutionControl().