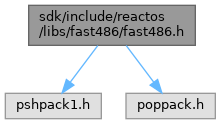

#include <pshpack1.h>

#include <poppack.h>

Go to the source code of this file.

◆ FAST486_BUSY_TSS_16_SIGNATURE

| #define FAST486_BUSY_TSS_16_SIGNATURE 0x03 |

◆ FAST486_BUSY_TSS_SIGNATURE

| #define FAST486_BUSY_TSS_SIGNATURE 0x0B |

◆ FAST486_CACHE_SIZE

◆ FAST486_CALL_GATE_16_SIGNATURE

| #define FAST486_CALL_GATE_16_SIGNATURE 0x04 |

◆ FAST486_CALL_GATE_SIGNATURE

| #define FAST486_CALL_GATE_SIGNATURE 0x0C |

◆ FAST486_CHAR_MAX

| #define FAST486_CHAR_MAX (127) |

◆ FAST486_CHAR_MIN

| #define FAST486_CHAR_MIN (-128) |

◆ FAST486_CR0_AM

| #define FAST486_CR0_AM (1 << 18) |

◆ FAST486_CR0_CD

| #define FAST486_CR0_CD (1 << 30) |

◆ FAST486_CR0_EM

| #define FAST486_CR0_EM (1 << 2) |

◆ FAST486_CR0_ET

| #define FAST486_CR0_ET (1 << 4) |

◆ FAST486_CR0_MP

| #define FAST486_CR0_MP (1 << 1) |

◆ FAST486_CR0_NE

| #define FAST486_CR0_NE (1 << 5) |

◆ FAST486_CR0_NW

| #define FAST486_CR0_NW (1 << 29) |

◆ FAST486_CR0_PE

| #define FAST486_CR0_PE (1 << 0) |

◆ FAST486_CR0_PG

| #define FAST486_CR0_PG (1 << 31) |

◆ FAST486_CR0_TS

| #define FAST486_CR0_TS (1 << 3) |

◆ FAST486_CR0_WP

| #define FAST486_CR0_WP (1 << 16) |

◆ FAST486_DBG_BREAK_EXEC

| #define FAST486_DBG_BREAK_EXEC 0 |

◆ FAST486_DBG_BREAK_READWRITE

| #define FAST486_DBG_BREAK_READWRITE 3 |

◆ FAST486_DBG_BREAK_WRITE

| #define FAST486_DBG_BREAK_WRITE 1 |

◆ FAST486_DR4_B0

| #define FAST486_DR4_B0 (1 << 0) |

◆ FAST486_DR4_B1

| #define FAST486_DR4_B1 (1 << 1) |

◆ FAST486_DR4_B2

| #define FAST486_DR4_B2 (1 << 2) |

◆ FAST486_DR4_B3

| #define FAST486_DR4_B3 (1 << 3) |

◆ FAST486_DR4_BD

| #define FAST486_DR4_BD (1 << 13) |

◆ FAST486_DR4_BS

| #define FAST486_DR4_BS (1 << 14) |

◆ FAST486_DR4_BT

| #define FAST486_DR4_BT (1 << 15) |

◆ FAST486_DR4_RESERVED

| #define FAST486_DR4_RESERVED 0xFFFF1FF0 |

◆ FAST486_DR5_G0

| #define FAST486_DR5_G0 (1 << 1) |

◆ FAST486_DR5_G1

| #define FAST486_DR5_G1 (1 << 3) |

◆ FAST486_DR5_G2

| #define FAST486_DR5_G2 (1 << 5) |

◆ FAST486_DR5_G3

| #define FAST486_DR5_G3 (1 << 7) |

◆ FAST486_DR5_GD

| #define FAST486_DR5_GD (1 << 13) |

◆ FAST486_DR5_GE

| #define FAST486_DR5_GE (1 << 9) |

◆ FAST486_DR5_L0

| #define FAST486_DR5_L0 (1 << 0) |

◆ FAST486_DR5_L1

| #define FAST486_DR5_L1 (1 << 2) |

◆ FAST486_DR5_L2

| #define FAST486_DR5_L2 (1 << 4) |

◆ FAST486_DR5_L3

| #define FAST486_DR5_L3 (1 << 6) |

◆ FAST486_DR5_LE

| #define FAST486_DR5_LE (1 << 8) |

◆ FAST486_DR5_RESERVED

| #define FAST486_DR5_RESERVED 0x0000DC00 |

◆ FAST486_FPU_DEFAULT_CONTROL

| #define FAST486_FPU_DEFAULT_CONTROL 0x037F |

◆ FAST486_IDT_INT_GATE

| #define FAST486_IDT_INT_GATE 0x06 |

◆ FAST486_IDT_INT_GATE_32

| #define FAST486_IDT_INT_GATE_32 0x0E |

◆ FAST486_IDT_TRAP_GATE

| #define FAST486_IDT_TRAP_GATE 0x07 |

◆ FAST486_IDT_TRAP_GATE_32

| #define FAST486_IDT_TRAP_GATE_32 0x0F |

◆ FAST486_LDT_SIGNATURE

| #define FAST486_LDT_SIGNATURE 0x02 |

◆ FAST486_LONG_MAX

◆ FAST486_LONG_MIN

| #define FAST486_LONG_MIN (-2147483648LL) |

◆ FAST486_NUM_CTRL_REGS

| #define FAST486_NUM_CTRL_REGS 3 |

◆ FAST486_NUM_DBG_REGS

| #define FAST486_NUM_DBG_REGS 6 |

◆ FAST486_NUM_FPU_REGS

| #define FAST486_NUM_FPU_REGS 8 |

◆ FAST486_NUM_GEN_REGS

| #define FAST486_NUM_GEN_REGS 8 |

◆ FAST486_NUM_SEG_REGS

| #define FAST486_NUM_SEG_REGS 6 |

◆ FAST486_PAGE_SIZE

| #define FAST486_PAGE_SIZE 4096 |

◆ FAST486_PREFIX_ADSIZE

| #define FAST486_PREFIX_ADSIZE (1 << 2) |

◆ FAST486_PREFIX_LOCK

| #define FAST486_PREFIX_LOCK (1 << 3) |

◆ FAST486_PREFIX_OPSIZE

| #define FAST486_PREFIX_OPSIZE (1 << 1) |

◆ FAST486_PREFIX_REP

| #define FAST486_PREFIX_REP (1 << 5) |

◆ FAST486_PREFIX_REPNZ

| #define FAST486_PREFIX_REPNZ (1 << 4) |

◆ FAST486_PREFIX_SEG

| #define FAST486_PREFIX_SEG (1 << 0) |

◆ FAST486_SHORT_MAX

◆ FAST486_SHORT_MIN

| #define FAST486_SHORT_MIN (-32768L) |

◆ FAST486_TASK_GATE_SIGNATURE

| #define FAST486_TASK_GATE_SIGNATURE 0x05 |

◆ FAST486_TSS_16_SIGNATURE

| #define FAST486_TSS_16_SIGNATURE 0x01 |

◆ FAST486_TSS_SIGNATURE

| #define FAST486_TSS_SIGNATURE 0x09 |

◆ FASTCALL