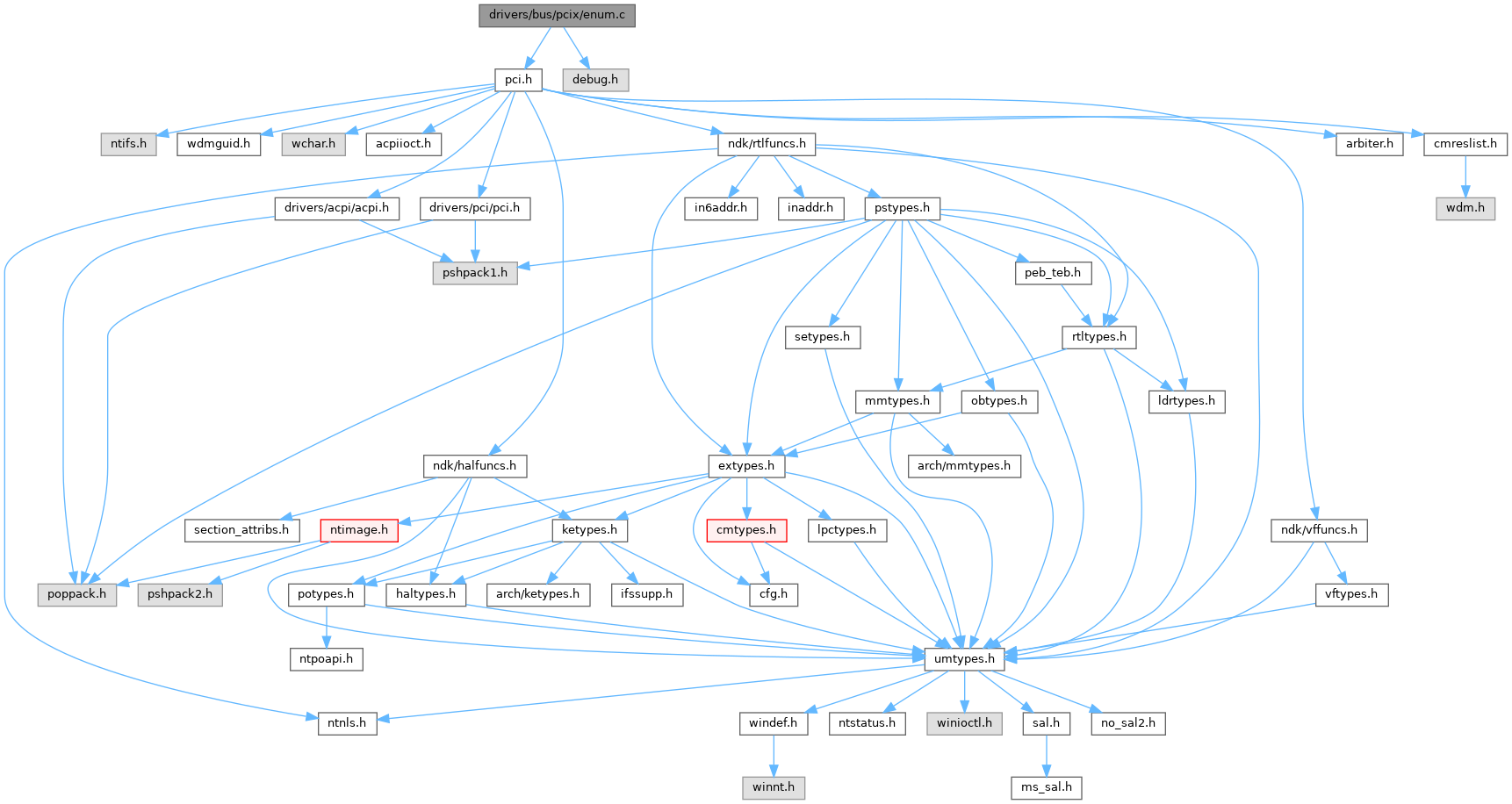

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

Variables | |

| PIO_RESOURCE_REQUIREMENTS_LIST | PciZeroIoResourceRequirements |

| PCI_CONFIGURATOR | PciConfigurators [] |

Macro Definition Documentation

◆ NDEBUG

Function Documentation

◆ PciAllocateCmResourceList()

Definition at line 333 of file enum.c.

Referenced by PciQueryResources().

◆ PciAllocateIoRequirementsList()

| PIO_RESOURCE_REQUIREMENTS_LIST NTAPI PciAllocateIoRequirementsList | ( | IN ULONG | Count, |

| IN ULONG | BusNumber, | ||

| IN ULONG | SlotNumber | ||

| ) |

Definition at line 300 of file enum.c.

Referenced by PciBuildRequirementsList().

◆ PciApplyHacks()

| VOID NTAPI PciApplyHacks | ( | IN PPCI_FDO_EXTENSION | DeviceExtension, |

| IN PPCI_COMMON_HEADER | PciData, | ||

| IN PCI_SLOT_NUMBER | SlotNumber, | ||

| IN ULONG | OperationType, | ||

| PPCI_PDO_EXTENSION | PdoExtension | ||

| ) |

Definition at line 803 of file enum.c.

Referenced by PciScanBus(), and PciSetResources().

◆ PciBuildRequirementsList()

| NTSTATUS NTAPI PciBuildRequirementsList | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PPCI_COMMON_HEADER | PciData, | ||

| OUT PIO_RESOURCE_REQUIREMENTS_LIST * | Buffer | ||

| ) |

Definition at line 560 of file enum.c.

Referenced by PciAssignSlotResources(), and PciQueryRequirements().

◆ PciComputeNewCurrentSettings()

| BOOLEAN NTAPI PciComputeNewCurrentSettings | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PCM_RESOURCE_LIST | ResourceList | ||

| ) |

Definition at line 55 of file enum.c.

Referenced by PciAssignSlotResources(), and PciPdoIrpStartDevice().

◆ PciConfigureIdeController()

| BOOLEAN NTAPI PciConfigureIdeController | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PPCI_COMMON_HEADER | PciData, | ||

| IN BOOLEAN | Initial | ||

| ) |

Definition at line 663 of file enum.c.

Referenced by PciApplyHacks(), and PciSetResources().

◆ PciGetEnhancedCapabilities()

| VOID NTAPI PciGetEnhancedCapabilities | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PPCI_COMMON_HEADER | PciData | ||

| ) |

Definition at line 1180 of file enum.c.

Referenced by PciScanBus().

◆ PciGetFunctionLimits()

| NTSTATUS NTAPI PciGetFunctionLimits | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PPCI_COMMON_HEADER | Current, | ||

| IN ULONGLONG | HackFlags | ||

| ) |

Definition at line 1492 of file enum.c.

Referenced by PciScanBus().

◆ PcipGetFunctionLimits()

| NTSTATUS NTAPI PcipGetFunctionLimits | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

Definition at line 1351 of file enum.c.

Referenced by PciGetFunctionLimits().

◆ PcipIsSameDevice()

| BOOLEAN NTAPI PcipIsSameDevice | ( | IN PPCI_PDO_EXTENSION | DeviceExtension, |

| IN PPCI_COMMON_HEADER | PciData | ||

| ) |

Definition at line 1072 of file enum.c.

Referenced by PciScanBus(), and PciSetResources().

◆ PciProcessBus()

| VOID NTAPI PciProcessBus | ( | IN PPCI_FDO_EXTENSION | DeviceExtension | ) |

Definition at line 1528 of file enum.c.

Referenced by PciScanBus().

◆ PcipUpdateHardware()

Definition at line 247 of file enum.c.

Referenced by PciUpdateHardware().

◆ PciQueryDeviceRelations()

| NTSTATUS NTAPI PciQueryDeviceRelations | ( | IN PPCI_FDO_EXTENSION | DeviceExtension, |

| IN OUT PDEVICE_RELATIONS * | pDeviceRelations | ||

| ) |

Definition at line 2043 of file enum.c.

Referenced by PciFdoIrpQueryDeviceRelations().

◆ PciQueryEjectionRelations()

| NTSTATUS NTAPI PciQueryEjectionRelations | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN OUT PDEVICE_RELATIONS * | pDeviceRelations | ||

| ) |

Definition at line 547 of file enum.c.

Referenced by PciPdoIrpQueryDeviceRelations().

◆ PciQueryRequirements()

| NTSTATUS NTAPI PciQueryRequirements | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN OUT PIO_RESOURCE_REQUIREMENTS_LIST * | RequirementsList | ||

| ) |

Definition at line 592 of file enum.c.

Referenced by PciPdoIrpQueryResourceRequirements().

◆ PciQueryResources()

| NTSTATUS NTAPI PciQueryResources | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| OUT PCM_RESOURCE_LIST * | Buffer | ||

| ) |

Definition at line 363 of file enum.c.

Referenced by PciPdoIrpQueryResources().

◆ PciQueryTargetDeviceRelations()

| NTSTATUS NTAPI PciQueryTargetDeviceRelations | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN OUT PDEVICE_RELATIONS * | pDeviceRelations | ||

| ) |

Definition at line 520 of file enum.c.

Referenced by PciPdoIrpQueryDeviceRelations().

◆ PciScanBus()

| NTSTATUS NTAPI PciScanBus | ( | IN PPCI_FDO_EXTENSION | DeviceExtension | ) |

Definition at line 1580 of file enum.c.

Referenced by PciQueryDeviceRelations().

◆ PciSetResources()

| NTSTATUS NTAPI PciSetResources | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN BOOLEAN | DoReset, | ||

| IN BOOLEAN | SomethingSomethingDarkSide | ||

| ) |

Definition at line 2164 of file enum.c.

Referenced by PciAssignSlotResources(), and PciPdoIrpStartDevice().

◆ PciSkipThisFunction()

| BOOLEAN NTAPI PciSkipThisFunction | ( | IN PPCI_COMMON_HEADER | PciData, |

| IN PCI_SLOT_NUMBER | Slot, | ||

| IN UCHAR | OperationType, | ||

| IN ULONGLONG | HackFlags | ||

| ) |

Definition at line 1106 of file enum.c.

Referenced by PciGetFunctionLimits(), and PciScanBus().

◆ PciUpdateHardware()

| VOID NTAPI PciUpdateHardware | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PPCI_COMMON_HEADER | PciData | ||

| ) |

Definition at line 274 of file enum.c.

Referenced by PciSetResources().

◆ PciWriteLimitsAndRestoreCurrent()

Definition at line 1308 of file enum.c.

Referenced by PcipGetFunctionLimits().

Variable Documentation

◆ PciConfigurators

| PCI_CONFIGURATOR PciConfigurators[] |

Definition at line 20 of file enum.c.

Referenced by PcipGetFunctionLimits(), and PciSetResources().

◆ PciZeroIoResourceRequirements

| PIO_RESOURCE_REQUIREMENTS_LIST PciZeroIoResourceRequirements |

Definition at line 18 of file enum.c.

Referenced by PciBuildRequirementsList(), and PciQueryRequirements().