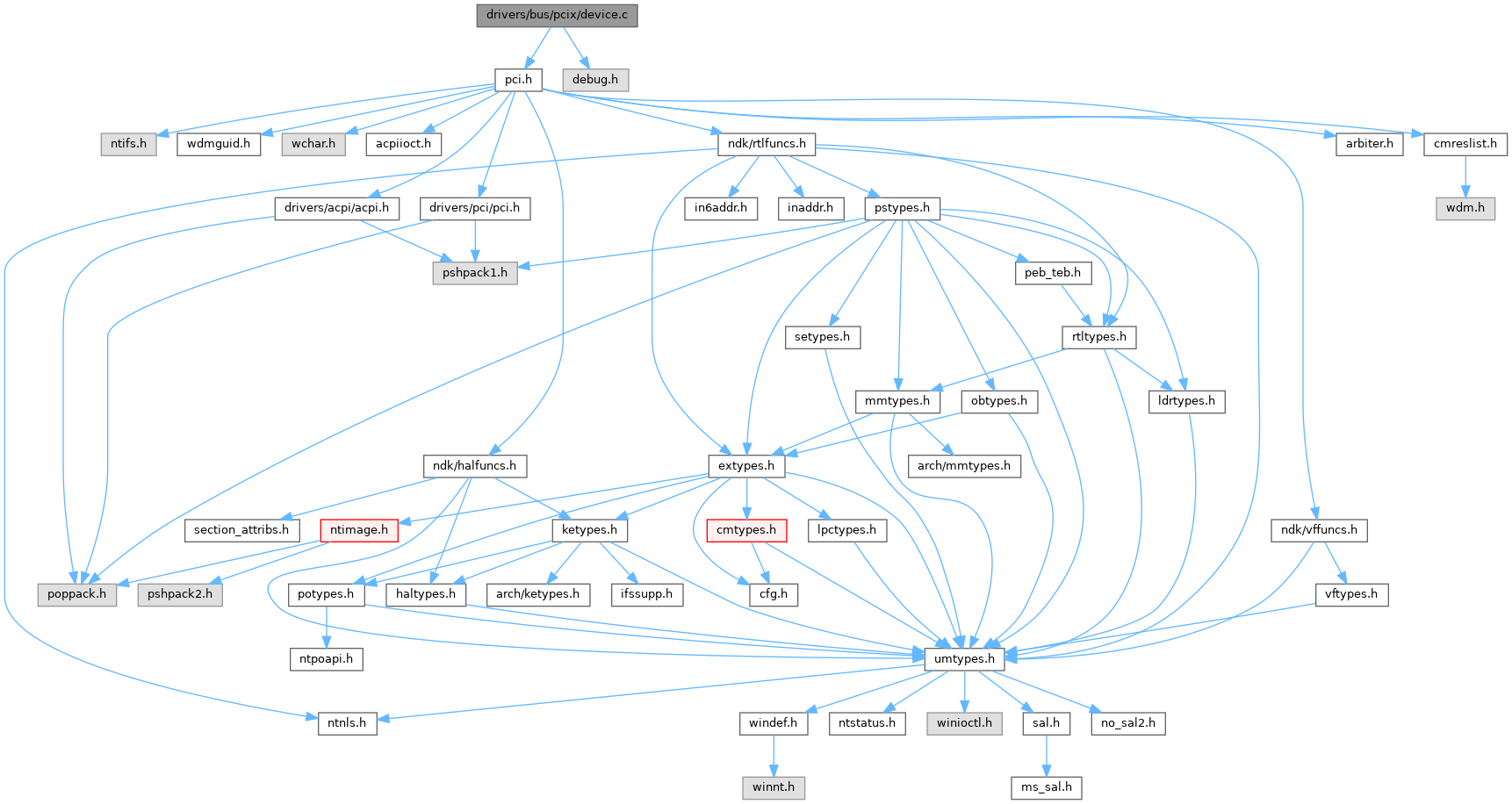

Include dependency graph for device.c:

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

Macro Definition Documentation

◆ NDEBUG

Function Documentation

◆ Device_ChangeResourceSettings()

| VOID NTAPI Device_ChangeResourceSettings | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PPCI_COMMON_HEADER | PciData | ||

| ) |

Definition at line 283 of file device.c.

285{

287 UNREFERENCED_PARAMETER(PciData);

288 /* Not yet implemented */

289 UNIMPLEMENTED_DBGBREAK();

290}

◆ Device_GetAdditionalResourceDescriptors()

| VOID NTAPI Device_GetAdditionalResourceDescriptors | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context, |

| IN PPCI_COMMON_HEADER | PciData, | ||

| IN PIO_RESOURCE_DESCRIPTOR | IoDescriptor | ||

| ) |

Definition at line 259 of file device.c.

262{

264 UNREFERENCED_PARAMETER(PciData);

265 UNREFERENCED_PARAMETER(IoDescriptor);

266 /* Not yet implemented */

267 UNIMPLEMENTED_DBGBREAK();

268}

◆ Device_MassageHeaderForLimitsDetermination()

| VOID NTAPI Device_MassageHeaderForLimitsDetermination | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

Definition at line 218 of file device.c.

219{

220 PPCI_COMMON_HEADER PciData;

222 PULONG BarArray;

224

225 /* Get pointers from context data */

227 PciData = Context->PciData;

228

229 /* Get the array of BARs */

230 BarArray = PciData->u.type0.BaseAddresses;

231

232 /* Check for IDE controllers that are not in native mode */

235 (PdoExtension->ProgIf & 5) != 5)

236 {

237 /* These controllers only use legacy resources */

238 i = 4;

239 }

240

241 /* Set all the bits on, which will allow us to recover the limit data */

243

244 /* Do the same for the PCI ROM BAR */

245 PciData->u.type0.ROMBaseAddress = PCI_ADDRESS_ROM_ADDRESS_MASK;

246}

GLsizei GLenum const GLvoid GLsizei GLenum GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLint GLint GLint GLshort GLshort GLshort GLubyte GLubyte GLubyte GLuint GLuint GLuint GLushort GLushort GLushort GLbyte GLbyte GLbyte GLbyte GLdouble GLdouble GLdouble GLdouble GLfloat GLfloat GLfloat GLfloat GLint GLint GLint GLint GLshort GLshort GLshort GLshort GLubyte GLubyte GLubyte GLubyte GLuint GLuint GLuint GLuint GLushort GLushort GLushort GLushort GLboolean const GLdouble const GLfloat const GLint const GLshort const GLbyte const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLdouble const GLfloat const GLfloat const GLint const GLint const GLshort const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort const GLdouble const GLfloat const GLint const GLshort GLenum GLenum GLenum GLfloat GLenum GLint GLenum GLenum GLenum GLfloat GLenum GLenum GLint GLenum GLfloat GLenum GLint GLint GLushort GLenum GLenum GLfloat GLenum GLenum GLint GLfloat const GLubyte GLenum GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLint GLint GLsizei GLsizei GLint GLenum GLenum const GLvoid GLenum GLenum const GLfloat GLenum GLenum const GLint GLenum GLenum const GLdouble GLenum GLenum const GLfloat GLenum GLenum const GLint GLsizei GLuint GLfloat GLuint GLbitfield GLfloat GLint GLuint GLboolean GLenum GLfloat GLenum GLbitfield GLenum GLfloat GLfloat GLint GLint const GLfloat GLenum GLfloat GLfloat GLint GLint GLfloat GLfloat GLint GLint const GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat GLint GLfloat GLfloat const GLdouble const GLfloat const GLdouble const GLfloat GLint i

Definition: glfuncs.h:248

Definition: iotypes.h:3580

Definition: pci.h:264

◆ Device_ResetDevice()

| VOID NTAPI Device_ResetDevice | ( | IN PPCI_PDO_EXTENSION | PdoExtension, |

| IN PPCI_COMMON_HEADER | PciData | ||

| ) |

Definition at line 272 of file device.c.

274{

276 UNREFERENCED_PARAMETER(PciData);

277 /* Not yet implemented */

278 UNIMPLEMENTED_DBGBREAK();

279}

◆ Device_RestoreCurrent()

| VOID NTAPI Device_RestoreCurrent | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

◆ Device_SaveCurrentSettings()

| VOID NTAPI Device_SaveCurrentSettings | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

Definition at line 20 of file device.c.

21{

22 PPCI_COMMON_HEADER PciData;

23 PIO_RESOURCE_DESCRIPTOR IoDescriptor;

24 PCM_PARTIAL_RESOURCE_DESCRIPTOR CmDescriptor;

26 PULONG BarArray;

28

29 /* Get variables from context */

30 PciData = Context->Current;

32

33 /* Loop all the PCI BARs */

34 BarArray = PciData->u.type0.BaseAddresses;

36 {

37 /* Get the resource descriptor and limit descriptor for this BAR */

40

41 /* Build the resource descriptor based on the limit descriptor */

48

49 /* Check if we're handling PCI BARs, or the ROM BAR */

51 {

52 /* Read the actual BAR value */

54

55 /* Check if this is an I/O BAR */

57 {

58 /* Use the right mask to get the I/O port base address */

60 BarMask = PCI_ADDRESS_IO_ADDRESS_MASK;

61 }

62 else

63 {

64 /* It's a RAM BAR, use the right mask to get the base address */

66 BarMask = PCI_ADDRESS_MEMORY_ADDRESS_MASK;

67

68 /* Check if it's a 64-bit BAR */

70 {

71 /* The next BAR value is actually the high 32-bits */

73 }

75 {

76 /* Legacy BAR, don't read more than 20 bits of the address */

77 BarMask = 0xFFFF0;

78 }

79 }

80 }

81 else

82 {

83 /* Actually a ROM BAR, so read the correct register */

84 Bar = PciData->u.type0.ROMBaseAddress;

85

86 /* Apply the correct mask for ROM BARs */

87 BarMask = PCI_ADDRESS_ROM_ADDRESS_MASK;

88

89 /* Make sure it's enabled */

91 {

92 /* If it isn't, then a descriptor won't be built for it */

94 continue;

95 }

96 }

97

98 /* Now we have the right mask, read the actual address from the BAR */

99 Bar &= BarMask;

101

102 /* And check for invalid BAR addresses */

104 {

105 /* Skip these descriptors */

108 }

109 }

110

111 /* Also save the sub-IDs that came directly from the PCI header */

112 Context->PdoExtension->SubsystemVendorId = PciData->u.type0.SubVendorID;

113 Context->PdoExtension->SubsystemId = PciData->u.type0.SubSystemID;

114}

Definition: main.cpp:19

Definition: restypes.h:8

union _CM_PARTIAL_RESOURCE_DESCRIPTOR::@384 u

struct _CM_PARTIAL_RESOURCE_DESCRIPTOR::@384::@385 Generic

struct _CM_PARTIAL_RESOURCE_DESCRIPTOR::@384::@389 Memory

Definition: miniport.h:144

struct _IO_RESOURCE_DESCRIPTOR::@2248::@2253 Generic

union _IO_RESOURCE_DESCRIPTOR::@2248 u

Definition: pci.h:235

◆ Device_SaveLimits()

| VOID NTAPI Device_SaveLimits | ( | IN PPCI_CONFIGURATOR_CONTEXT | Context | ) |

Definition at line 118 of file device.c.

119{

120 PPCI_COMMON_HEADER Current, PciData;

122 PULONG BarArray;

125

126 /* Get pointers from the context */

128 Current = Context->Current;

129 PciData = Context->PciData;

130

131 /* And get the array of bARs */

132 BarArray = PciData->u.type0.BaseAddresses;

133

134 /* First, check for IDE controllers that are not in native mode */

137 (PdoExtension->ProgIf & 5) != 5)

138 {

139 /* They should not be using any non-legacy resources */

140 BarArray[0] = 0;

141 BarArray[1] = 0;

142 BarArray[2] = 0;

143 BarArray[3] = 0;

144 }

146 ((PdoExtension->DeviceId == 0x88F0) ||

147 (PdoExtension->DeviceId == 0x8880)))

148 {

149 /*

150 * The problem is caused by the S3 Vision 968/868 video controller which

151 * is used on the Diamond Stealth 64 Video 3000 series, Number Nine 9FX

152 * motion 771, and other popular video cards, all containing a memory bug.

153 * The 968/868 claims to require 32 MB of memory, but it actually decodes

154 * 64 MB of memory.

155 */

157 {

158 /* Find its 32MB RAM BAR */

160 {

161 /* Increase it to 64MB to make sure nobody touches the buffer */

162 BarArray[i] = 0xFC000000;

164 }

165 }

166 }

167

168 /* Check for Cirrus Logic GD5430/5440 cards */

170 {

171 /* Check for the I/O port requirement */

172 if (BarArray[1] == 0xFC01)

173 {

174 /* Check for completely bogus BAR */

175 if (Current->u.type0.BaseAddresses[1] == 1)

176 {

177 /* Ignore it */

178 BarArray[1] = 0;

180 }

181 else

182 {

183 /* Otherwise, this BAR seems okay */

185 Current->u.type0.BaseAddresses[1]);

186 }

187 }

188 else if (BarArray[1])

189 {

190 /* Strange, the I/O BAR was not found as expected (or at all) */

192 BarArray[1]);

193 }

194 }

195

196 /* Finally, process all the limit descriptors */

199 {

200 /* And build them based on the BARs */

202 {

203 /* This function returns TRUE if the BAR was 64-bit, handle this */

205 i++;

207 }

208 }

209

210 /* Create the last descriptor based on the ROM address */

212 &PciData->u.type0.ROMBaseAddress,

213 TRUE);

214}

BOOLEAN NTAPI PciCreateIoDescriptorFromBarLimit(PIO_RESOURCE_DESCRIPTOR ResourceDescriptor, IN PULONG BarArray, IN BOOLEAN Rom)

Definition: utils.c:1175