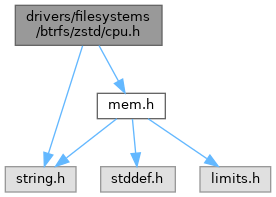

Include dependency graph for cpu.h:

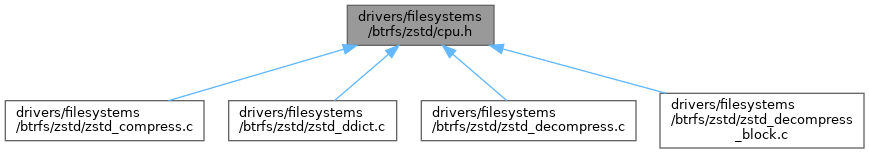

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | ZSTD_cpuid_t |

Macros | |

| #define | X(name, r, bit) |

| #define | C(name, bit) X(name, f1c, bit) |

| #define | D(name, bit) X(name, f1d, bit) |

| #define | B(name, bit) X(name, f7b, bit) |

| #define | C(name, bit) X(name, f7c, bit) |

Functions | |

| MEM_STATIC ZSTD_cpuid_t | ZSTD_cpuid (void) |

| C (sse3, 0) C(pclmuldq | |

| C (dtes64, 2) C(monitor | |

| C (dscpl, 4) C(vmx | |

| C (smx, 6) C(eist | |

| C (tm2, 8) C(ssse3 | |

| C (cnxtid, 10) C(fma | |

| C (cx16, 13) C(xtpr | |

| C (pdcm, 15) C(pcid | |

| C (dca, 18) C(sse41 | |

| C (sse42, 20) C(x2apic | |

| C (movbe, 22) C(popcnt | |

| C (tscdeadline, 24) C(aes | |

| C (xsave, 26) C(osxsave | |

| C (avx, 28) C(f16c | |

| C (rdrand, 30) D(fpu | |

| D (vme, 1) D(de | |

| D (pse, 3) D(tsc | |

| D (msr, 5) D(pae | |

| D (mce, 7) D(cx8 | |

| D (apic, 9) D(sep | |

| D (mtrr, 12) D(pge | |

| D (mca, 14) D(cmov | |

| D (pat, 16) D(pse36 | |

| D (psn, 18) D(clfsh | |

| D (ds, 21) D(acpi | |

| D (mmx, 23) D(fxsr | |

| D (sse, 25) D(sse2 | |

| D (ss, 27) D(htt | |

| D (tm, 29) D(pbe | |

| B (bmi1, 3) B(hle | |

| B (avx2, 5) B(smep | |

| B (bmi2, 8) B(erms | |

| B (invpcid, 10) B(rtm | |

| B (mpx, 14) B(avx512f | |

| B (avx512dq, 17) B(rdseed | |

| B (adx, 19) B(smap | |

| B (avx512ifma, 21) B(pcommit | |

| B (clflushopt, 23) B(clwb | |

| B (avx512pf, 26) B(avx512er | |

| B (avx512cd, 28) B(sha | |

| B (avx512bw, 30) B(avx512vl | |

| C (prefetchwt1, 0) C(avx512vbmi | |

Macro Definition Documentation

◆ B

◆ C [1/2]

◆ C [2/2]

◆ D

◆ X

Value:

Function Documentation

◆ B() [1/12]

| B | ( | adx | , |

| 19 | |||

| ) |

◆ B() [2/12]

| B | ( | avx2 | , |

| 5 | |||

| ) |

◆ B() [3/12]

| B | ( | avx512bw | , |

| 30 | |||

| ) |

◆ B() [4/12]

| B | ( | avx512cd | , |

| 28 | |||

| ) |

◆ B() [5/12]

| B | ( | avx512dq | , |

| 17 | |||

| ) |

◆ B() [6/12]

| B | ( | avx512ifma | , |

| 21 | |||

| ) |

◆ B() [7/12]

| B | ( | avx512pf | , |

| 26 | |||

| ) |

◆ B() [8/12]

| B | ( | bmi1 | , |

| 3 | |||

| ) |

◆ B() [9/12]

| B | ( | bmi2 | , |

| 8 | |||

| ) |

◆ B() [10/12]

| B | ( | clflushopt | , |

| 23 | |||

| ) |

◆ B() [11/12]

| B | ( | invpcid | , |

| 10 | |||

| ) |

◆ B() [12/12]

| B | ( | mpx | , |

| 14 | |||

| ) |

◆ C() [1/16]

◆ C() [2/16]

| C | ( | cnxtid | , |

| 10 | |||

| ) |

◆ C() [3/16]

| C | ( | cx16 | , |

| 13 | |||

| ) |

◆ C() [4/16]

| C | ( | dca | , |

| 18 | |||

| ) |

◆ C() [5/16]

| C | ( | dscpl | , |

| 4 | |||

| ) |

◆ C() [6/16]

| C | ( | dtes64 | , |

| 2 | |||

| ) |

◆ C() [7/16]

| C | ( | movbe | , |

| 22 | |||

| ) |

◆ C() [8/16]

| C | ( | pdcm | , |

| 15 | |||

| ) |

◆ C() [9/16]

| C | ( | prefetchwt1 | , |

| 0 | |||

| ) |

◆ C() [10/16]

| C | ( | rdrand | , |

| 30 | |||

| ) |

◆ C() [11/16]

| C | ( | smx | , |

| 6 | |||

| ) |

◆ C() [12/16]

| C | ( | sse3 | , |

| 0 | |||

| ) |

◆ C() [13/16]

| C | ( | sse42 | , |

| 20 | |||

| ) |

◆ C() [14/16]

| C | ( | tm2 | , |

| 8 | |||

| ) |

◆ C() [15/16]

| C | ( | tscdeadline | , |

| 24 | |||

| ) |

◆ C() [16/16]

| C | ( | xsave | , |

| 26 | |||

| ) |

◆ D() [1/14]

| D | ( | apic | , |

| 9 | |||

| ) |

◆ D() [2/14]

| D | ( | ds | , |

| 21 | |||

| ) |

◆ D() [3/14]

| D | ( | mca | , |

| 14 | |||

| ) |

◆ D() [4/14]

| D | ( | mce | , |

| 7 | |||

| ) |

◆ D() [5/14]

| D | ( | mmx | , |

| 23 | |||

| ) |

◆ D() [6/14]

| D | ( | msr | , |

| 5 | |||

| ) |

◆ D() [7/14]

| D | ( | mtrr | , |

| 12 | |||

| ) |

◆ D() [8/14]

| D | ( | pat | , |

| 16 | |||

| ) |

◆ D() [9/14]

| D | ( | pse | , |

| 3 | |||

| ) |

◆ D() [10/14]

| D | ( | psn | , |

| 18 | |||

| ) |

◆ D() [11/14]

| D | ( | ss | , |

| 27 | |||

| ) |

◆ D() [12/14]

| D | ( | sse | , |

| 25 | |||

| ) |

◆ D() [13/14]

| D | ( | tm | , |

| 29 | |||

| ) |

◆ D() [14/14]

| D | ( | vme | , |

| 1 | |||

| ) |

◆ ZSTD_cpuid()

| MEM_STATIC ZSTD_cpuid_t ZSTD_cpuid | ( | void | ) |

Definition at line 34 of file cpu.h.

34 {

36 U32 f1d = 0;

37 U32 f7b = 0;

38 U32 f7c = 0;

39#if defined(_MSC_VER) && (defined(_M_X64) || defined(_M_IX86))

42 {

48 }

53 }

54 }

55#elif defined(__i386__) && defined(__PIC__) && !defined(__clang__) && defined(__GNUC__)

56 /* The following block like the normal cpuid branch below, but gcc

57 * reserves ebx for use of its pic register so we must specially

58 * handle the save and restore to avoid clobbering the register

59 */

61 __asm__(

62 "pushl %%ebx\n\t"

63 "cpuid\n\t"

64 "popl %%ebx\n\t"

66 : "a"(0)

67 : "ecx", "edx");

69 U32 f1a;

70 __asm__(

71 "pushl %%ebx\n\t"

72 "cpuid\n\t"

73 "popl %%ebx\n\t"

75 : "a"(1));

76 }

78 __asm__(

79 "pushl %%ebx\n\t"

80 "cpuid\n\t"

81 "movl %%ebx, %%eax\n\t"

82 "popl %%ebx"

83 : "=a"(f7b), "=c"(f7c)

84 : "a"(7), "c"(0)

85 : "edx");

86 }

87#elif defined(__x86_64__) || defined(_M_X64) || defined(__i386__)

91 U32 f1a;

93 }

95 U32 f7a;

97 : "=a"(f7a), "=b"(f7b), "=c"(f7c)

98 : "a"(7), "c"(0)

99 : "edx");

100 }

101#endif

102 {

103 ZSTD_cpuid_t cpuid;

105 cpuid.f1d = f1d;

106 cpuid.f7b = f7b;

107 cpuid.f7c = f7c;

108 return cpuid;

109 }

110}

__INTRIN_INLINE void __cpuidex(int CPUInfo[4], int InfoType, int ECXValue)

Definition: intrin_x86.h:1680

__asm__(".p2align 4, 0x90\n" ".seh_proc __seh2_global_filter_func\n" "__seh2_global_filter_func:\n" "\tsub %rbp, %rax\n" "\tpush %rbp\n" "\t.seh_pushreg %rbp\n" "\tpush %rbx\n" "\t.seh_pushreg %rbx\n" "\tpush %rdi\n" "\t.seh_pushreg %rdi\n" "\tpush %rsi\n" "\t.seh_pushreg %rsi\n" "\tpush %r12\n" "\t.seh_pushreg %r12\n" "\tpush %r13\n" "\t.seh_pushreg %r13\n" "\tpush %r14\n" "\t.seh_pushreg %r14\n" "\tpush %r15\n" "\t.seh_pushreg %r15\n" "\tsub $40, %rsp\n" "\t.seh_stackalloc 40\n" "\t.seh_endprologue\n" "\tsub %rax, %rdx\n" "\tmov %rdx, %rbp\n" "\tjmp *%r8\n" "__seh2_global_filter_func_exit:\n" "\t.p2align 4\n" "\tadd $40, %rsp\n" "\tpop %r15\n" "\tpop %r14\n" "\tpop %r13\n" "\tpop %r12\n" "\tpop %rsi\n" "\tpop %rdi\n" "\tpop %rbx\n" "\tpop %rbp\n" "\tret\n" "\t.seh_endproc")

Referenced by ZSTD_initCCtx(), ZSTD_initDCtx_internal(), and ZSTD_initStaticCCtx().