#include <hal.h>#include <debug.h>

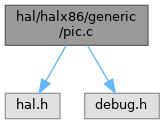

Include dependency graph for pic.c:

Go to the source code of this file.

Macros | |

| #define | NDEBUG |

Functions | |

| VOID NTAPI | HalpInitializeLegacyPICs (VOID) |

Macro Definition Documentation

◆ NDEBUG

Function Documentation

◆ HalpInitializeLegacyPICs()

Definition at line 18 of file pic.c.

19{

20 I8259_ICW1 Icw1;

21 I8259_ICW2 Icw2;

22 I8259_ICW3 Icw3;

23 I8259_ICW4 Icw4;

24

26

27 /* Initialize ICW1 for master, interval 8, edge-triggered mode with ICW4 */

33 Icw1.InterruptVectorAddress = 0;

35

36 /* ICW2 - interrupt vector offset */

39

40 /* Connect slave to IRQ 2 */

41 Icw3.Bits = 0;

44

45 /* Enable 8086 mode, non-automatic EOI, non-buffered mode, non special fully nested mode */

50 Icw4.Reserved = 0;

52

53 /* Mask all interrupts */

55

56 /* Initialize ICW1 for slave, interval 8, edge-triggered mode with ICW4 */

64

65 /* Set interrupt vector base */

68

69 /* Slave ID */

70 Icw3.Bits = 0;

71 Icw3.SlaveId = 2;

73

74 /* Enable 8086 mode, non-automatic EOI, non-buffered mode, non special fully nested mode */

79 Icw4.Reserved = 0;

81

82 /* Mask all interrupts */

84}

PPC_QUAL void __outbyte(unsigned long const Port, const unsigned char Data)

Definition: intrin_ppc.h:605

Definition: halhw.h:224

Definition: halhw.h:238

Definition: halhw.h:248

Definition: halhw.h:272

Referenced by HalpInitializePICs().